**1. **por的必要性

①有些簡單的異步SRAM芯片為了與CPU配合使用可能只需要一個3.3V的電源,但為了減小面積(或者說提高容量)芯片內(nèi)部存儲陣列可能會選用coredevice,core device的電源(如0.8V)要遠低于IO電源(3.3V),這就需要內(nèi)置一個3.3V轉(zhuǎn)0.8V的LDO,SRAM陣列檢測到0.8V電源trigger到一定閾值(如0.6V)再進行后續(xù)的讀寫操作,按順序完成整個上電過程,否則會出現(xiàn)讀寫錯誤。

②對于規(guī)模比較大的FPGA芯片,往往需要3、4個甚至更多電源。FPGA正常工作之前要經(jīng)過上電檢測、數(shù)字模塊的復(fù)位清零、內(nèi)部SRAM輸出使能、阻抗校正、全局寫使能等一系列操作。

因此,上電檢測是芯片正常工作的第一道保障,其重要性不言而喻。

2. por****舉例

假設(shè)芯片包含vdd09、vdd1p2、vdd1p8和vddio,其中vdd09為芯片內(nèi)部coredevice供電;vdd1p2為輸入輸出buffer供電;vdd1p8為內(nèi)部模擬電路(如bandgap,ldo等)供電;vddio為IO電源,IO電源需要兼容1.8V、2.5V和3.3V。

當(dāng)4路電源達到trigger閾值后,por電路產(chǎn)生por_b信號,指示上電完成,可以進行后續(xù)操作。下面介紹一下4路電源的por電路如何實現(xiàn)。

2.1 vdd09 por****電路

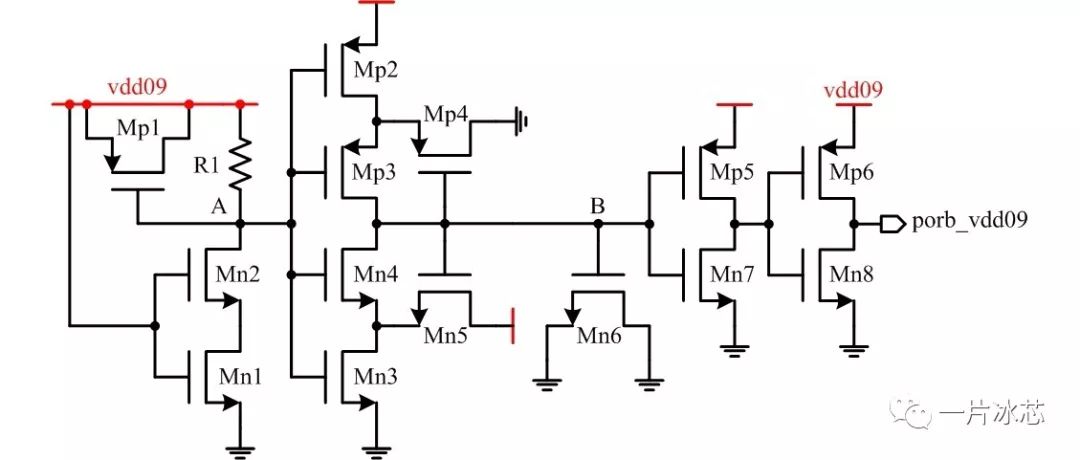

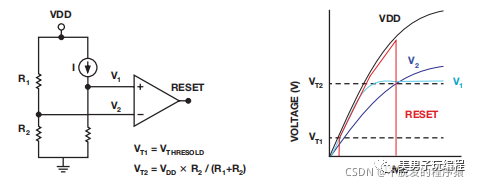

vdd09por電路如圖1所示,圖中所有管子均為0.9V的低壓管,Mp2Mp4和Mn3Mn5構(gòu)成Schmitt觸發(fā)器 ^[1-3]^ ,Schmitt觸發(fā)器有兩個重要的特性:①對于一個變化很慢的輸入波形,在輸出端有一個快速翻轉(zhuǎn)響應(yīng);②對正向和負向變化的輸入信號有不同的開關(guān)閾值。Schmitt觸發(fā)器的一個主要用途是把一個含噪聲或緩慢變化的輸入信號轉(zhuǎn)變成一個“干凈”的數(shù)字信號。

Fig1. vdd09的por電路

我們把vdd09的上電過程分三步進行解析:

①當(dāng)vdd09A = vdd09,porb_vdd09 = 0;

②當(dāng)vdd09上升到Vth,n附近時,M1和M2開始導(dǎo)通,此時V A = vdd09 - IR1,porb_vdd09= 0,I為流過R1的電流,由于I很小,隨著vdd09的抬高VA繼續(xù)增大,但此時VA變化的斜率逐漸變緩;

③當(dāng)vdd09繼續(xù)升高到大于Vth,n時,I急劇增大,此時隨著vdd09的變高VA將快速變小,當(dāng)VA減小到Schmitt觸發(fā)器的翻轉(zhuǎn)閾值時,porb_vdd09由低變高輸出vdd09。

整個上下電過程中A點和B點電壓和Schmitt觸發(fā)器的翻轉(zhuǎn)閾值變化如圖2所示,兩條曲線的交點即為上下電時的trigger電壓(V H ,V L ),圖中A1、A2、A3區(qū)域?qū)?yīng)①、②、③步。下電過程與上電過程類似,這里不再贅述。

Fig2. vdd09上下電過程各點波形

2.2 vdd1p2 por****電路

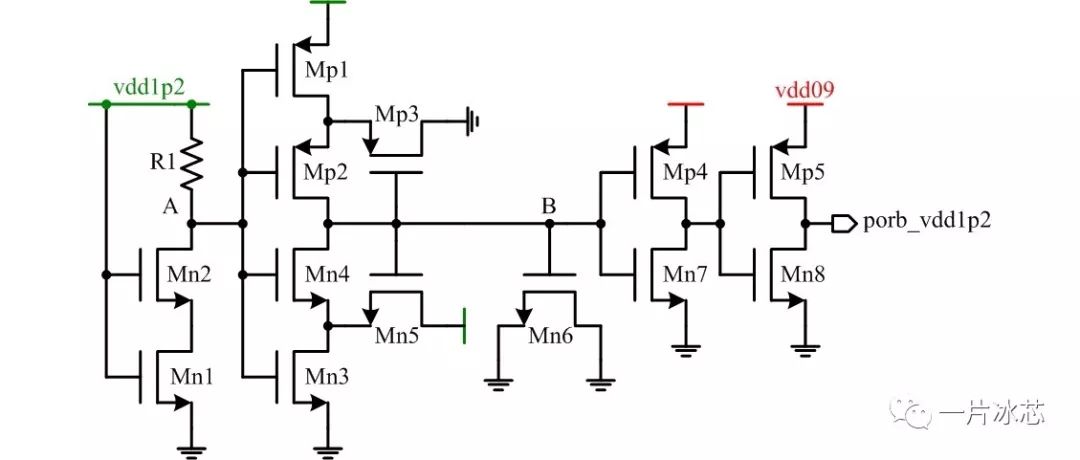

vdd1p2 por電路如圖3所示,圖中除Mp5和Mn8為0.9V的低壓管,其余均為1.2V device。

Fig3. vdd1p2的por電路

對比圖1和圖3結(jié)構(gòu),可以看出vdd1p2的por電路與vdd09的por電路結(jié)構(gòu)基本一致,只是增加了1.2V的device。

2.3 vdd1p8 por****電路

vdd1p8 por電路如圖4所示,圖中除Mp6和Mn8為0.9V的低壓管,其余均為1.8V device。

Fig4. vdd1p8的por電路

對比圖1和圖4結(jié)構(gòu),可以看出vdd1p8的por電路與vdd09的por電路類似,唯一不同的是Mn1和Mn2柵極的連接方式,由于0.9V低壓管和1.8V高壓管閾值電壓差別不大,但設(shè)計時vdd1p8的trigger電壓要比vdd09的trigger電壓高,若Mn1和Mn2仍接到vdd1p8,此時vdd1p8的por電路trigger電壓很難做高,將Mn1和Mn2的柵極與B點相連,可以抬高vdd1p8的trigger電壓。

2.4 vddio por****電路

vddio por電路如圖5所示,圖中除Mp7和Mn8為0.9V的低壓管,其余均為1.8V device。

Fig5. vdd1p8的por電路

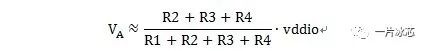

vddio por電路是設(shè)計難點,因為PDK里沒有高于1.8V的device且vddio要兼容1.8V/2.5V/3.3V電平標準,要考慮器件耐壓問題。假設(shè)vddio開始上電時vdd1p8已經(jīng)完成上電,此時Schmitt觸發(fā)器翻轉(zhuǎn)閾值保持不變,A點電壓為:

隨著vddio的抬高,A點電壓上升到Schmitt觸發(fā)器的翻轉(zhuǎn)閾值,此時的vddio電壓即為上電時刻的trigger電壓。

在實際電路設(shè)計時要注意以下兩點:

①為了保證電路的可靠性,應(yīng)確保VA不高于1.8V,取R2+R3+R4≈R1從而保證了VA最高為1.65V左右。

②當(dāng)溫度升高時,Schmitt觸發(fā)器的翻轉(zhuǎn)閾值會減小,若VA由純電阻分壓得到,在溫度變化時VA將基本保持不變,從而使得trigger電壓發(fā)生較大的偏移。為了補償溫度對trigger電壓的影響,電路引入了Mn1管,這樣A點電壓將隨著溫度的升高而降低,從而補償了施密特觸發(fā)器翻轉(zhuǎn)閾值隨溫度的變化。

**3. **總結(jié)

2.1~2.4節(jié)完成了vdd09/vdd1p2/vdd1p8/vddio的上電檢測,檢測完成后經(jīng)過與邏輯后,產(chǎn)生整體的por_b信號,指示后續(xù)電路完成4路電源的上電檢測。

-

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2029瀏覽量

61768 -

電源供電

+關(guān)注

關(guān)注

0文章

160瀏覽量

22339 -

FPGA開發(fā)

+關(guān)注

關(guān)注

1文章

43瀏覽量

15287 -

SRAM芯片

+關(guān)注

關(guān)注

0文章

65瀏覽量

12287 -

POR電路

+關(guān)注

關(guān)注

0文章

2瀏覽量

5548

發(fā)布評論請先 登錄

局放帶電檢測

做一個感應(yīng)水龍頭的供電檢測芯片方案開發(fā)

STM32的掉電檢測機制——PVD

微弱光信號的光電檢測系統(tǒng)設(shè)計

地線帶電檢測電路

聊聊芯片中的上電檢測(por)

聊聊芯片中的上電檢測(por)

評論