**1 **層級(jí)關(guān)系

曾經(jīng)我一直認(rèn)為cosim最頂層必須是一個(gè)數(shù)字頂層,其實(shí)不然。具體使用哪個(gè)做頂層要看項(xiàng)目,以數(shù)字為頂層的好處是,模擬仿真的結(jié)果都轉(zhuǎn)換為數(shù)字,比較好處理。

當(dāng)數(shù)字模塊是一個(gè)專用模塊,其它是以模擬模塊為主,這時(shí)候可以用模擬作為頂層。

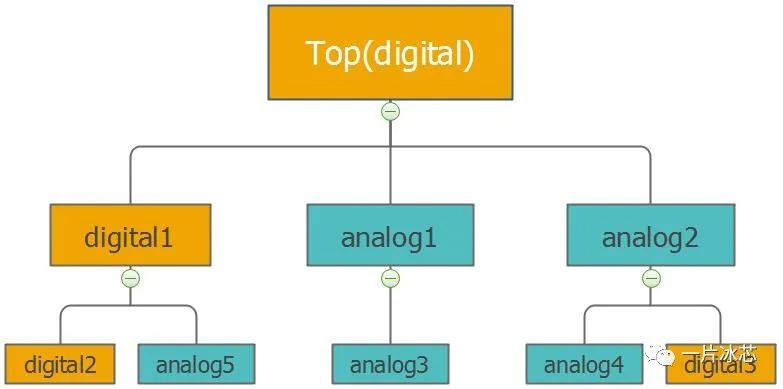

圖1給出了數(shù)字做頂層時(shí)的cosim層級(jí)關(guān)系,最頂層是數(shù)字,底層模擬模塊可以包含數(shù)字,數(shù)字模塊也可包含模擬,仿真時(shí)數(shù)字和模擬接口用a2d和d2a進(jìn)行轉(zhuǎn)換 。

Fig1. 數(shù)字做頂層時(shí)cosim層級(jí)關(guān)系.

**2 **仿真步驟

Synopsys做為主流三大EDA供應(yīng)商(另外兩家是Cadence和Mentor),其自帶的文檔就是最好的,我們不用費(fèi)勁周折去網(wǎng)上找,xa-vcscosim仿真方法在xa的安裝目錄下有實(shí)例($xa_install_dir/doc/tutorials/mixed_signal/XA-VCS),照著實(shí)例跑一下流程就行,xa自帶4位加法器cosim仿真文件如圖2所示。

Fig2. xa自帶cosim仿真實(shí)例文本

XA-VCS_tutorial.pdf中給出了仿真方法并對(duì)文件做了注釋,注釋如圖3所示。

Fig3. XA-VCS 4位加法器文件注釋

仔細(xì)讀一下XA-VCS_tutorial.pdf文檔并實(shí)際操作一下就能學(xué)會(huì)。

注:執(zhí)行run_xa_vcs命令之前要先啟動(dòng)xa和vcs軟件,run_xa_vcs不認(rèn)的話chmod一下。

例子雖然簡(jiǎn)單,帶來的問題就是Case覆蓋不全。例子中并沒有給出模擬到數(shù)字,數(shù)字到模擬之間的電平轉(zhuǎn)換規(guī)則,具體語法可參考文獻(xiàn)[2]中的a2d和d2a命令,將想要的電平轉(zhuǎn)換規(guī)則寫在vcsAD.init文本。

finesim-vcs或hsim-vcs仿真方法與xa-vcs類似,只要將vcsAD.init中的xa指令換成finesim或hsim即可。

**3 **仿真結(jié)果

圖4給出了我用finesim-vcs仿真pll的結(jié)果(根據(jù)xa自帶的例子改的),可見a2d/d2a的轉(zhuǎn)換是正確的。

Fig4. finesim-vcs仿真pll a2d/d2a轉(zhuǎn)換

圖5給出了我用finesim-vcs仿真pll的vctrl波形(模擬),可見環(huán)路能夠正常鎖定。

Fig5. finesim-vcs仿真pll vctrl波形

圖6給出了我用Cadence AMS(步驟跟xa-vcs類似,只是多了圖形界面(個(gè)人不太喜歡圖形界面,影響效率,不過流程也沒那么簡(jiǎn)單)仿真二分頻的波形。

Fig6. AMS仿真分頻器波形

**4 **思考與討論

①a2d和d2a該如何合理寫入vcsAD.init?②如何從xa切換到finesim?③如何用Cadence的AMS做混仿,AMS與xa-vcs各自的優(yōu)缺點(diǎn)是什么?

-

EDA工具

+關(guān)注

關(guān)注

4文章

273瀏覽量

32955 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30822 -

電平轉(zhuǎn)換

+關(guān)注

關(guān)注

3文章

157瀏覽量

34346 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9992 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6835

發(fā)布評(píng)論請(qǐng)先 登錄

絕對(duì)經(jīng)典VCS中文教程

VCS可以驗(yàn)證FPGA RAMB的INIT初值嗎?謝謝

在VCS中如何利用Makefile腳本進(jìn)行仿真?

nanosim和vcs混合仿真的過程是怎樣的?

基于linux系統(tǒng)的VCS使用及仿真說明

一種數(shù)模混合SoC 設(shè)計(jì)協(xié)同仿真的驗(yàn)證方法

一種數(shù)模混合SoC 設(shè)計(jì)協(xié)同仿真的驗(yàn)證方法

基于linux系統(tǒng)實(shí)現(xiàn)的vivado調(diào)用VCS仿真教程

以xa-vcs為例如何進(jìn)行cosim仿真驗(yàn)證?

以xa-vcs為例如何進(jìn)行cosim仿真驗(yàn)證?

評(píng)論