基于ATE的IC測試原理、方法及故障分析

本文以ATE為基礎(chǔ),討論了 集成電路測試的基本原理和測試方法,并進(jìn)行了故 障分析.

集成 電 路 測試主要分為三種:

verifa ct iont est,稱之為芯片驗(yàn)證 ,主要用來驗(yàn)證一個新的設(shè)計在量產(chǎn)之前功能是否正確,參數(shù)特 性等是否符合pec以及電路的穩(wěn)定性和可靠性.測 試范圍包括功能測試和AC/DC測試,測試項目相 對來說比較全面.其主要目的除了調(diào)試之外還為量產(chǎn)測試作準(zhǔn)備.Verification的周期直接關(guān)系到產(chǎn)品的質(zhì)量和競爭力以及投放市場的時間.

mass production test,稱之為量產(chǎn)測試 .量產(chǎn)測 試在整個Ic生產(chǎn)體系中位于制程的后段,其主要 功能在于檢測Ic在制造過程中所發(fā)生的瑕疵和造 成瑕疵的原因.因此,量產(chǎn)測試是確保Ic產(chǎn)品良好 率,提供有效的數(shù)據(jù)供工程分析使用的重要步驟. mass production test以測試時間計費(fèi),同時測試設(shè) 備價格的高低也將影響每小時的測試費(fèi)用,從而直 接影響產(chǎn)品的成本,因此提高測試覆蓋率和測試效 率非常重要.

burn- in ,主要用于測試可靠性 .采用各種加速 因子來模擬器件長期的失效模型,常用的有 加高溫, 加高電壓等 .

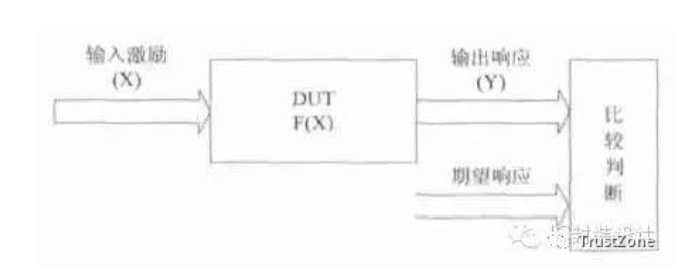

集 成 電 路測試的基本原則是通過測試向量對芯片施加激勵,測量芯片響應(yīng)輸出(response),與事先 預(yù)測的結(jié)果比較,若符合,則大體上可以說明芯片是好的。

原文連接:基于ATE的IC測試原理、方法及故障分析.PDF[1]

淺談基于ATE的IC測試精確度及穩(wěn)定性問題

隨著IC產(chǎn)業(yè)的飛速發(fā)展,IC的復(fù)雜度及其電氣參數(shù)的性能也日益提高,同時也給IC測試帶來了眾多難題,其中測試的精確度及穩(wěn)定性是一直困擾工程師的兩大難題,尤其在量產(chǎn)ATE測試時表現(xiàn)更為嚴(yán)重,那么, 如何在測試中做到精確、穩(wěn)定的測試這些IC的各項性能參數(shù) ,以 確保產(chǎn)品質(zhì)量,并避免由于測試不穩(wěn)定而導(dǎo)致反復(fù)重測而浪費(fèi)大量測試時間呢 ?

本文就IC測試的基本參數(shù): 電壓、電流、時間、THD等的測試進(jìn)行深入分析 ,并舉以實(shí)例來說明如何解決此類問題,以供廣大測試工程師參考。

電壓測試問題

在IC的測試中,電壓的測試是所有測試參數(shù)中最為常見的一種參數(shù),尤其是模擬芯片的測試,電壓測試更顯常見及重要,如:LDO、LED驅(qū)動、音頻功放、運(yùn)放、馬達(dá)驅(qū)動等很多類型的模擬芯片都含有電壓參數(shù)的測試,而且都是其主要性能參數(shù)。

另外,也有很多其他的參數(shù)都是通過電壓的測量來間接得到的,如增益(Gain)、電源電壓抑制比(PSRR)、共模抑制比(CMRR)等。工程師們在調(diào)試中也經(jīng)常會遇到電壓測的不精確或者不穩(wěn)定的現(xiàn)象,對于測試不精確的問題,目前主要采用correlation的辦法,來調(diào)整測試的誤差,但這種方法對于線性的芯片尚可使用,但對于非線性的芯片卻無用武之地。

針對測試不穩(wěn)定的問題,大多采用多次測量取平均值的辦法來解決,但這種辦法也是治標(biāo)不治本,同樣會給產(chǎn)品的質(zhì)量帶來隱患。那么如何解決電壓測試的這些問題呢?以下將具體分析產(chǎn)生這些現(xiàn)象的具體原因,并針對這些原因闡述一些解決辦法。

- 1)、芯片工作狀態(tài)未完全建立或有震蕩

一般在開發(fā)測試程序之前必須了解所測試的芯片的功能及性能參數(shù),這樣在開發(fā)及調(diào)試程序時才能心中有數(shù),比如測試LDO的輸出電壓參數(shù),你必須清楚:在當(dāng)前的輸入及輸出濾波電容之下,它的輸入電壓加上之后,輸出電壓需要多長時間才能達(dá)到穩(wěn)定,而你在程序中設(shè)定的等待時間必須大于這個穩(wěn)定時間,這樣才能做到測試的準(zhǔn)確且穩(wěn)定。

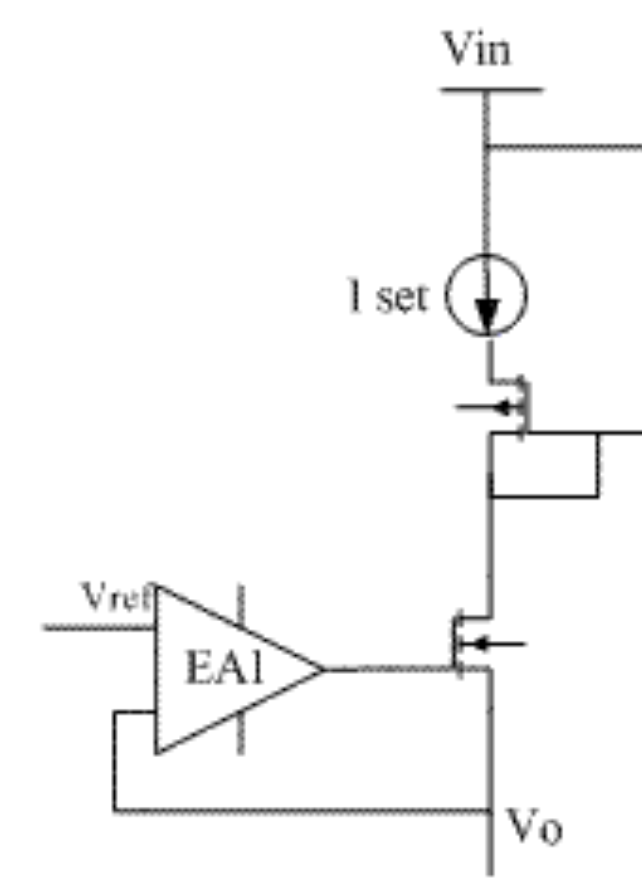

當(dāng)然LDO的輸出穩(wěn)定時間一般都在微秒級(幾十到上百微秒),所以調(diào)試時不太會遇到此類問題,但有的時候我們需要測試芯片內(nèi)部的基準(zhǔn)電壓,但又沒有辦法直接進(jìn)行測試,只能通過其他的引腳間接測試,如圖1為LED驅(qū)動芯片的部分線路圖,

圖1

我們要測試芯片內(nèi)部Vref的電壓,但又沒有直接的引腳出來,所以只能通過測試VO端的電壓進(jìn)行間接測試,但是需要注意的是:如果VO端懸空,沒有任何電流流出,那么它上面的MOS管則不能正常導(dǎo)通工作,EA1的反饋回路也不能正常建立,而導(dǎo)致VO端的電壓也不確定,此時測試的VO電壓將不能代表Vref的電壓。所以在測試時,我們必須給VO一定的負(fù)載讓MOS管及EA1能夠正常工作,這樣才能正確測試Vref的電壓。

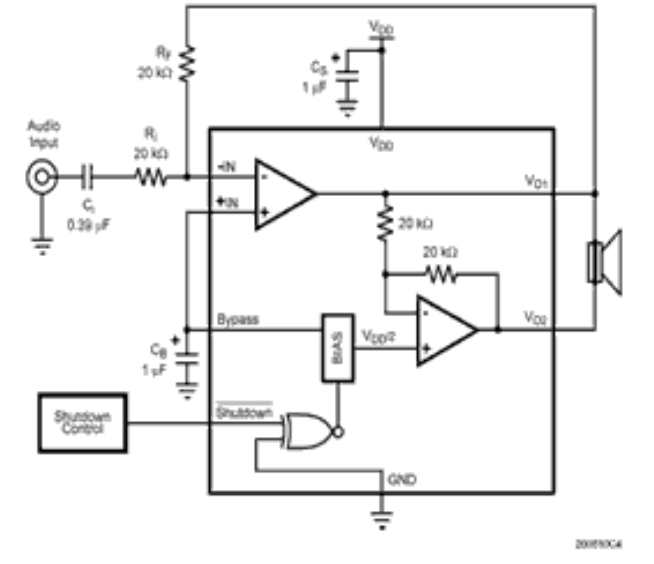

芯片工作狀態(tài)的建立,有時需要比較長的時間,如圖2為一音頻功放(LM4990)的功能框圖及典型應(yīng)用線路圖,

圖2

我們在ATE測試時會測試一些靜態(tài)直流參數(shù),如bypass、Vo1、Vo2端電壓值,當(dāng)你仔細(xì)研讀此芯片的手冊,你會發(fā)現(xiàn)在電源電壓為5V、Cbypass為1Uf時(注意不同的電源電壓及Cbypass電容,其穩(wěn)定時間也是不同的),bypass端的電壓需要至少100ms才能達(dá)到穩(wěn)定,而Vo1、Vo2端的電壓又受bypass端電壓的影響,所以要想穩(wěn)定且準(zhǔn)確的測試這些直流參數(shù),必須要在芯片上電之后等待100ms以上再進(jìn)行測試(必須考慮不同批次芯片間的差異,所以在實(shí)際測試中的等待時間可在120ms左右),但對于量產(chǎn)測試,測試時間的長短將直接影響到測試效率及測試費(fèi)用,我們必須縮短測試時間!那么如何來解決這個問題呢,一般我們可以采用如下兩種辦法:

第一,可以減小Cbypass的電容,這樣同樣的充電電流及電壓,充電時間會隨著電容的減小而減少,可以使用0.1uF或者更小的電容來替代,此時有些讀者可能會說:這樣做肯定會影響到后面的交流參數(shù)(如THD)的測試,沒錯!肯定會有影響!那么又如何來解決呢?其實(shí)很簡單,也可以有兩種解決方案:1、通過測試評估,適當(dāng)調(diào)整在0.1uF時的交流參數(shù)的測試規(guī)范,當(dāng)測試要求不高時可采用此方案;2、通過外加繼電器來選擇測試直流及交流參數(shù)時的電容值,但是繼電器的連接方式也是很有講究的,不然也會對交流參數(shù)有影響,這在后面的段落中再詳細(xì)闡述。

第二,可以采用預(yù)充電的方式對Cbypass進(jìn)行提前大電流充電,如果bypass端在電源電壓為5V時正常情況下是2.5V左右,我們可以預(yù)充電到2.3V,這樣同樣可以節(jié)省很多時間,但這種解決辦法必須注意一個問題就是:不要在充電的同時給bypass端帶來額外的干擾,而導(dǎo)致芯片不能正常工作。

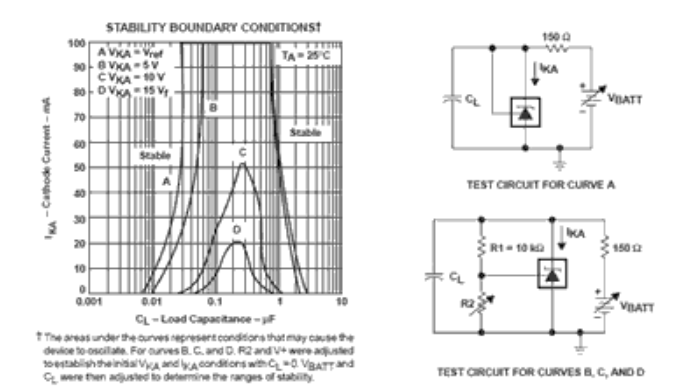

震蕩在芯片調(diào)試時也是比較常見的現(xiàn)象,由此給芯片測試也帶來諸多問題,引起震蕩的原因有很多:輸出容性負(fù)載的大小、阻抗不匹配、不當(dāng)?shù)姆答伝芈返龋鐖D3為一款LDO(TL431)芯片手冊中的一幅電性能特性曲線及測試圖,圖中明顯規(guī)定了輸出容性負(fù)載CL的大小范圍,

但是我們在實(shí)際調(diào)試中可能沒有注意到這一點(diǎn),如果選用的輸出電容不是在芯片穩(wěn)定所需要的容值范圍之內(nèi),那么輸出就會產(chǎn)生震蕩,導(dǎo)致輸出測試不準(zhǔn)且不穩(wěn)定。所以在此再次提醒大家:在調(diào)試之前務(wù)必將芯片性能做到比較詳細(xì)的了解,以免在后期的調(diào)試中浪費(fèi)大量的時間。

另外震蕩不光是在芯片正常工作時發(fā)生,在靜態(tài)時也有可能發(fā)生。尤其當(dāng)你測試放大倍數(shù)比較高的運(yùn)放時,此時的輸入引腳要特別注意,必要時要進(jìn)行隔離,以免引入不必要的噪聲而導(dǎo)致輸出產(chǎn)生震蕩。

-

濾波電容

+關(guān)注

關(guān)注

8文章

459瀏覽量

41133 -

輸出電壓

+關(guān)注

關(guān)注

2文章

1839瀏覽量

39441 -

PSRR

+關(guān)注

關(guān)注

0文章

220瀏覽量

40088 -

ATE

+關(guān)注

關(guān)注

6文章

158瀏覽量

27338 -

LED驅(qū)動芯片

+關(guān)注

關(guān)注

8文章

186瀏覽量

26730

發(fā)布評論請先 登錄

3nm時代即將到來,ATE測試機(jī)有了這些明顯變化

聊聊IC測試機(jī)(1)ATE/ATS內(nèi)部結(jié)構(gòu)簡介

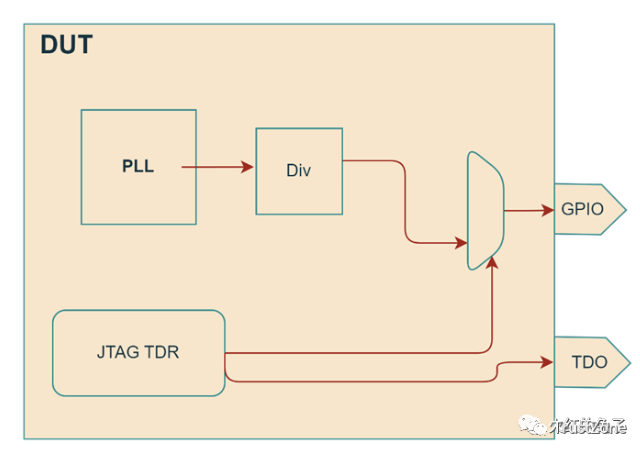

聊聊IC測試機(jī)(4)DFT PLL向量,ATE怎么用?

IC測試基本原理與ATE測試向量生成

TSOP48測試機(jī),BGA IC測試架(BGA IC測試治具和BGA 測試座)。

TSOP48測試機(jī),BGA植球返修, IC測試架(BGA IC測試治具和BGA 測試座

TSOP48測試機(jī),BGA植球返修, IC測試架(BGA IC測試治具和BGA 測試座)。

TSOP48測試機(jī),BGA植球返修, IC測試架

TSOP48測試機(jī),BGA植球返修, IC測試架(BGA IC測試治具和BGA 測試座)。

TSOP48測試機(jī),BGA植球返修, IC測試架

河洛發(fā)表邏輯/混合訊號IC測試機(jī)

IC測試原理與ATE測試向量的生成

聊聊IC測試機(jī)(3)基于ATE的IC測試原理、方法及故障分析

聊聊IC測試機(jī)(3)基于ATE的IC測試原理、方法及故障分析

評論