為什么pcb走線需要等長?

可以參考這篇文章 PCB設計十大誤區-繞不完的等長_等長仿真計算-CSDN博客,簡單的理解就是時序是指電路系統的時間特性,即電路的狀態隨時間的變化情況。數字電路中的信號延遲、時鐘頻率。

數字電路中,每個操作都需要在正確的時間執行,因為電子元件并不是瞬間完成其功能的。例如,在時鐘信號的上升沿或下降沿處將數據寫入存儲器,然后等待一段時間后讀取數據。如果在錯誤的時序下執行這些操作,從機數據接收錯誤,導致亂碼,(奇偶校驗位就是防止數據亂碼)

時序分析,在高速數字電路中,通過對電路的設計和模擬來確保電路操作的正確時間關系。它可以通過使用時序約束來指定電路組件之間的相對時序關系。時序分析可以幫助設計人員避免電路中的冒險現象、穩態和暫態時序故障等問題。

時序匹配:在高速數字電路中,信號的到達時間對于確保數據的正確傳輸非常重要。如果信號經過的路徑長度不同,就會導致信號間的時延差異,可能導致時序錯誤。通過保持信號路徑等長,可以最大程度上減小時延差異,使信號到達終點的時間保持一致。

信號完整性:信號在傳輸過程中可能會受到噪聲、互相干擾和反射等影響。等長走線可以幫助降低這些問題的發生概率。當信號經過不等長的走線時,由于信號的傳播速度是有限的,不等長的走線可能導致信號波形的失真和不完整。通過保持信號路徑等長,可以減小這些問題的風險,提升信號的完整性。

信號匹配:在差分信號傳輸中,等長走線也可以實現差分信號的匹配。差分信號是指同時傳輸正負兩個相位相反的信號,通過比較這兩個信號的差異來恢復原始信號。等長走線可以確保正負兩個信號的傳播時間一致,從而保持差分信號的匹配性能。

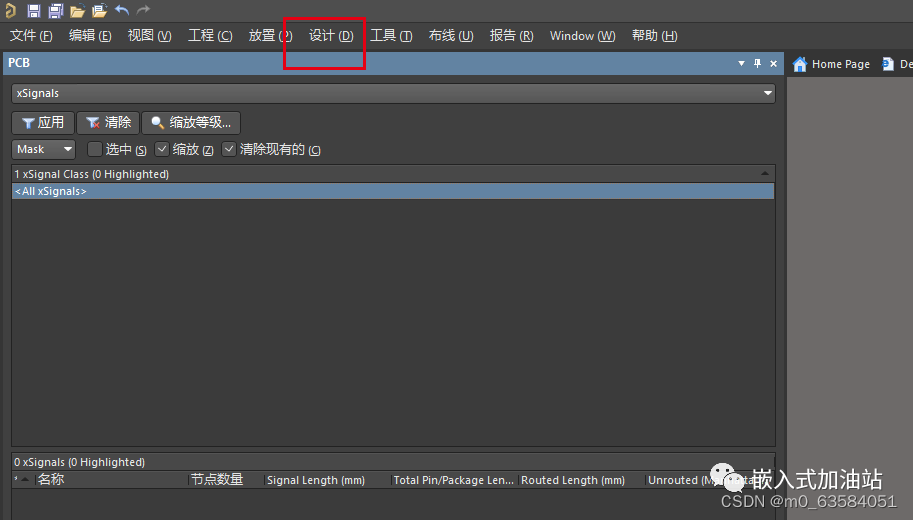

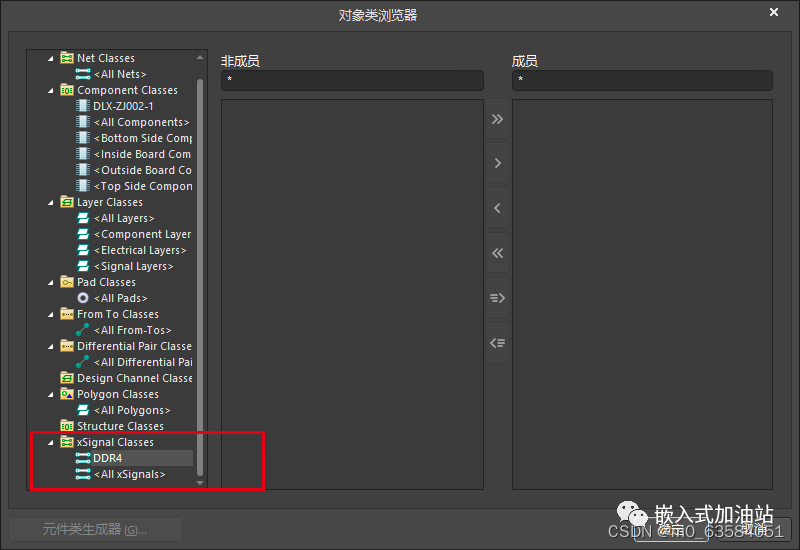

1.添加xSignal,class

編輯

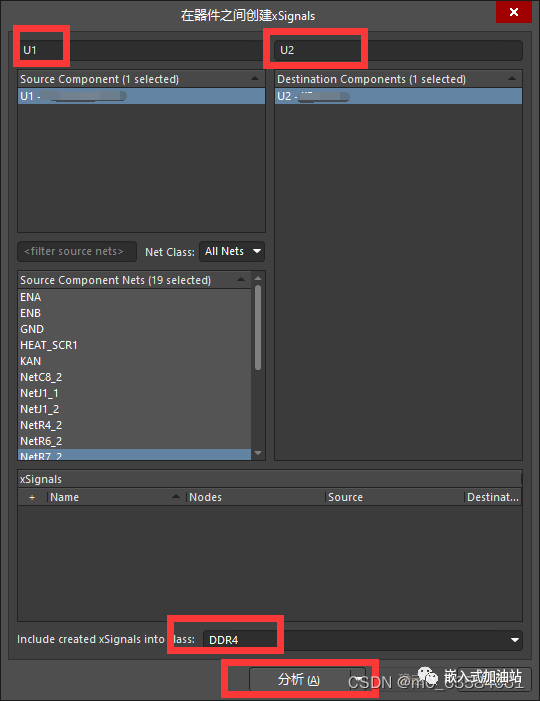

編輯2.再點擊設置-創建xsignal,選擇兩個器件需要等長的網絡

編輯

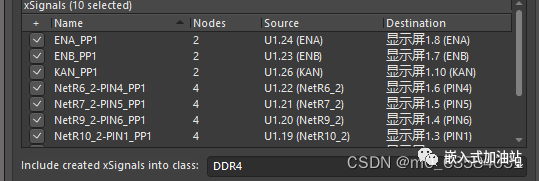

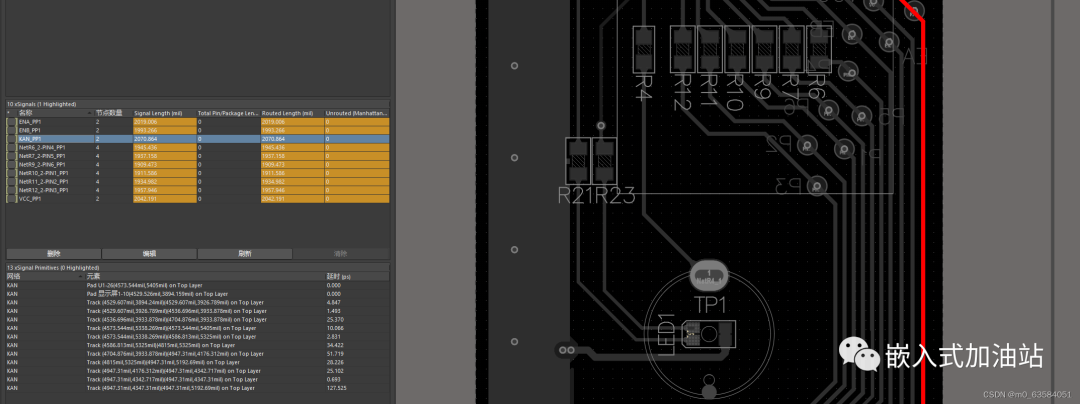

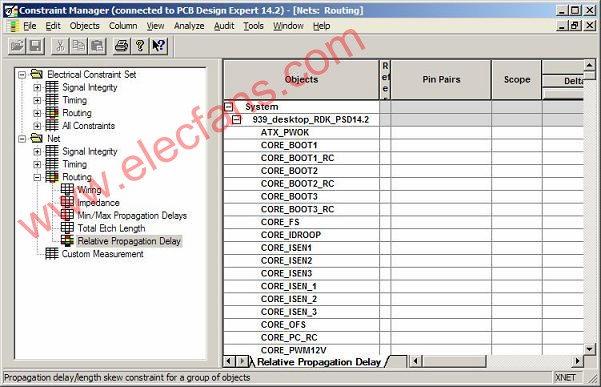

點擊分析可以選擇要等長的網絡

編輯

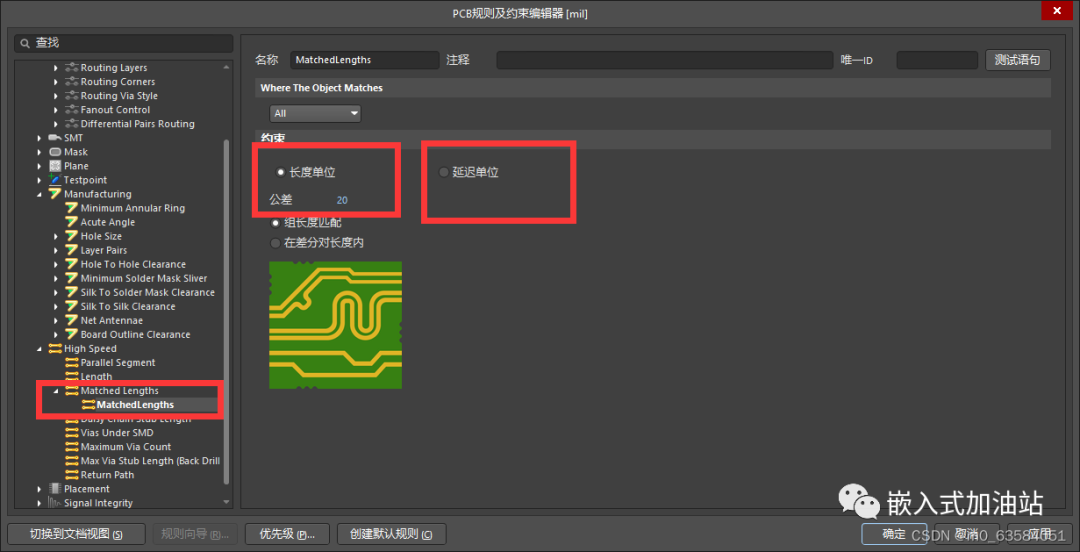

規則中設置長度公差

編輯

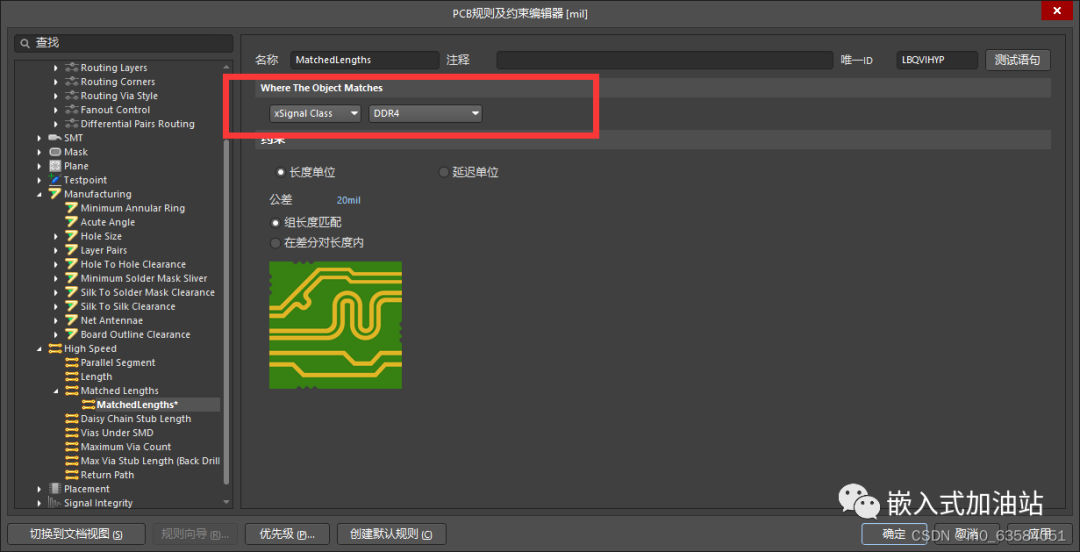

選擇創建的類

編輯

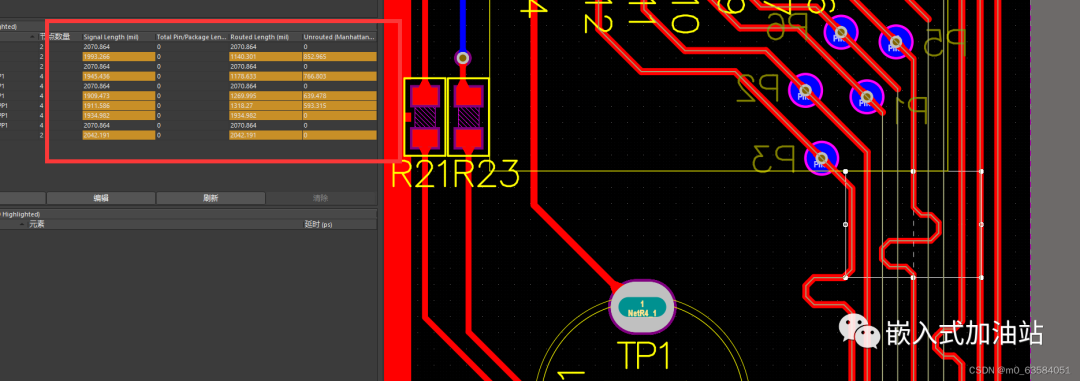

此時黃色表示警告,以黑色線為標準

編輯

編輯

黑色表示公差<=20mil

-

pcb

+關注

關注

4357文章

23440瀏覽量

407652 -

altium

+關注

關注

47文章

973瀏覽量

119750 -

數字電路

+關注

關注

193文章

1637瀏覽量

81660 -

Designer

+關注

關注

0文章

132瀏覽量

36403

原文標題:Altium Designer 21 xSignal等長設置

文章出處:【微信號:嵌入式加油站,微信公眾號:嵌入式加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

請教,SIM卡PCB走線,這個CKL時鐘線和數據線DATA要等長嘛,一條走頂層一條走底層如圖這樣可以嘛

請問地址線需不需要等長走線?

AD9446 LVDS信號線的PCB走線的差分對間等長有沒有要求?

教您在Allegro中設置走線等長進階

PCB設計做等長走線的目的是什么

PCB設計中如何實現等長走線

DDR 高速PCB 設計走線繞等長資料下載

為什么pcb走線需要等長?

為什么pcb走線需要等長?

評論