LOD效應也是DSM效應的其中一種。DSM Effect即Deep Sub-Micron Effect,包括WPE、LOD、OSE、Hot carrier effects等等,本篇介紹LOD effect,和WPE一樣,是大家經常討論的effects。

大家知道,用于隔離器件的幾種方法:整面全區氧化、LOCOS、STI。

整面全區氧化隔離在最早期使用,工藝簡單,但是效率不高,占用很大面積,現在先進工藝不再使用。

后來出現了LOCOS隔離,局部氧化,優于整面全區氧化,但是有鳥嘴。

先進工藝現在多用STI淺槽隔離,工藝相對復雜,但是隔離效果好,占用面積小。

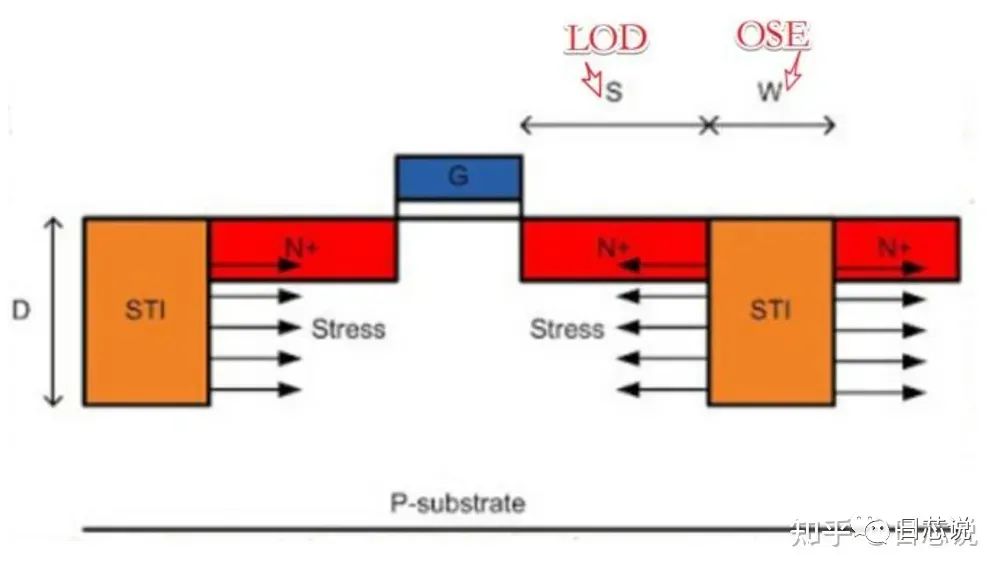

LOCOS是做的濕法氧化,STI是用的CVD工藝,CVD化學氣相沉積沉積速率高,說白了就是挖出溝槽這個動作會對兩側的器件產生機械壓力,因此STI會產生應力。

這個應力會使得STI兩側的器件特性受到影響,具體什么影響呢?這里就涉及到了LOD和OSE效應了。

LOD效應:由于STI到多晶硅柵poly的距離也就是器件有源區長度的不同,應力對器件的影響也不同,因此叫做擴散區長度效應,如下圖,有源區OD的長度越大,STI對器件的應力影響越小。因此,如果想要2個MOS匹配,那么他們到STI的距離應該是一樣的或者距離大到可以忽略不計LOD效應。

OSE效應:OD Space Effect,是由于STI本身的寬度不同引起的對兩側器件的應力不同。這個效應在數字IC研究居多,模擬IC主要研究LOD效應。

LOD效應和WPE效應一樣,直接影響MOS管的閾值電壓等參數,因此如果電路對閾值電壓比較敏感,那么在layout中一定要把LOD效應考慮在內,不然layout畫完再做優化就很費事,導致芯片設計周期變長。

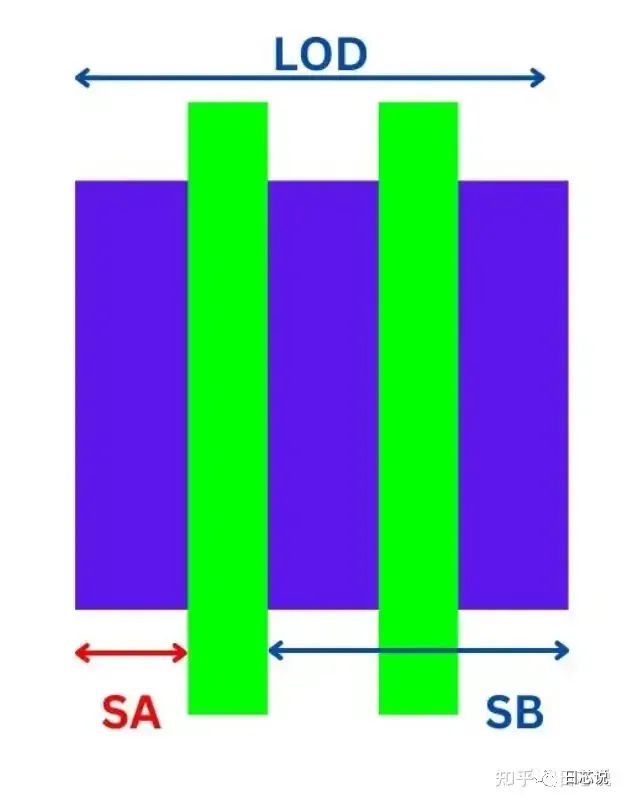

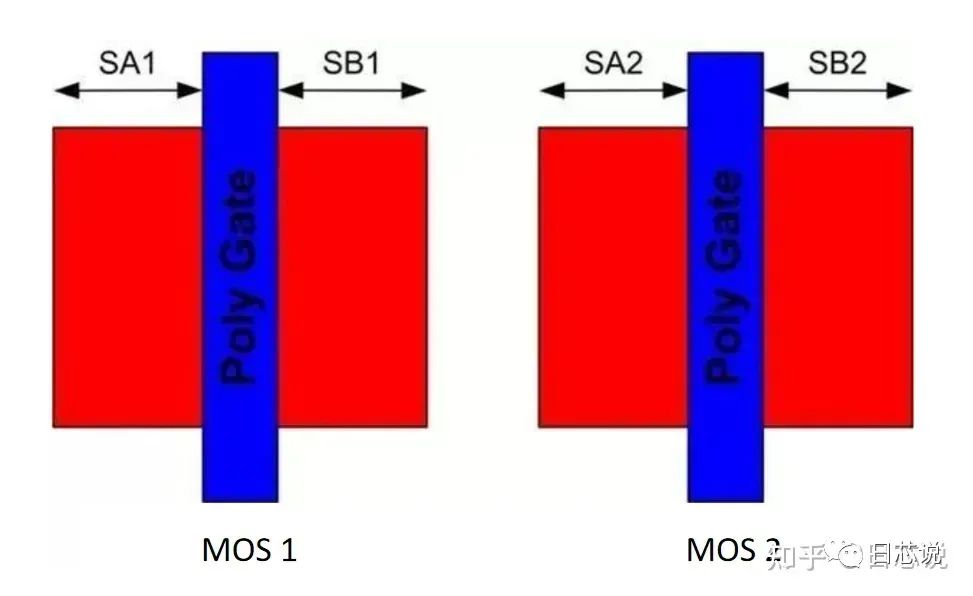

LOD效應對MOS性能影響的大小,與有源區OD的長度有關,如下圖,綠色代表poly,藍色代表OD有源區,以左側poly為MOS管為例,SA代表源極OD長度,SB代表漏極OD長度(可互換),對于單個MOS來說,源漏極OD長度不是必須相等的。

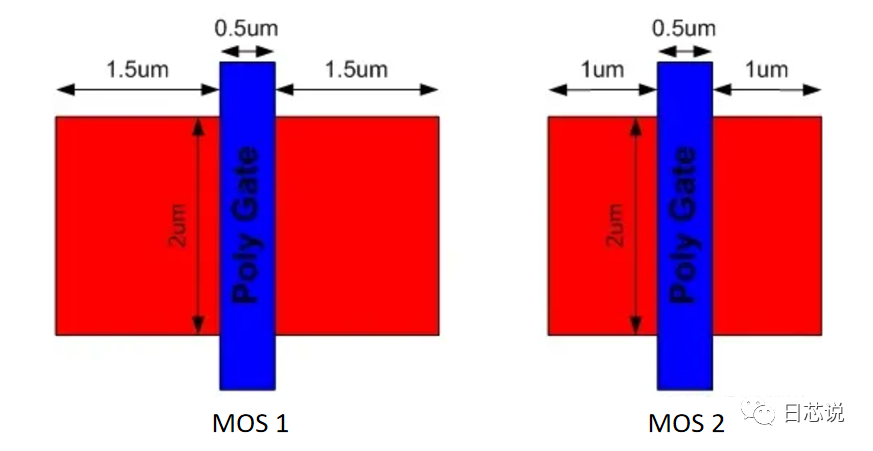

下圖中,兩個MOS的W都是2um,L都是0.5um,但由于左邊管子MOS A的源漏的長度是SA=SB=1.5um,右邊管子MOS B的源漏的長度是SA=SB=1um,那么相同尺寸的管子,由于OD長度不相等,所以流過的電流大小并不完全相等。

因此,如果想要MOS A和B做到完全匹配,那么A和B的OD長度應該做到相等才可以,即SA_A=SA_B,SB_A=SB_B。

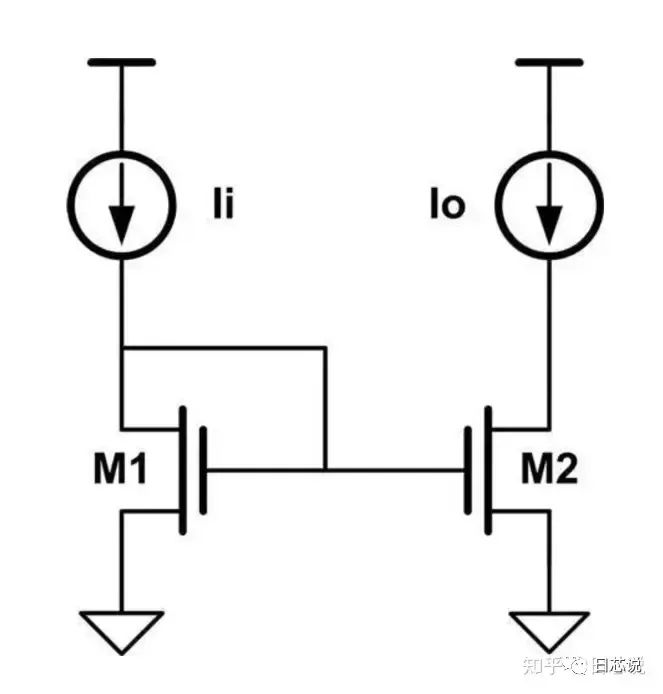

在具體的模擬IC電路中,如何考量LOD效應呢,接下來以一個簡單的mirror電路為例講解一下,以下部分筆記參考bubuchen的筆記。

以下電流鏡電路,Ii是輸入電流,Io是輸出電流,拿到這個電路,我們第一目的是想要Ii完全等于Io,或者有整數倍的關系。

假如,我們想要Io=Ii,即M1和M2的尺寸要相等。以一個finger為例,M1和M2分開放置,不共用源漏,如下圖。在layout中,我們要保證SA1=SA2,SB1=SB2,不用保證SA=SB,那么LOD效應對MOS 1和MOS 2的影響是一樣的,因此M1和M2就可以做到匹配了,Io=Ii就不會因為LOD造成誤差。

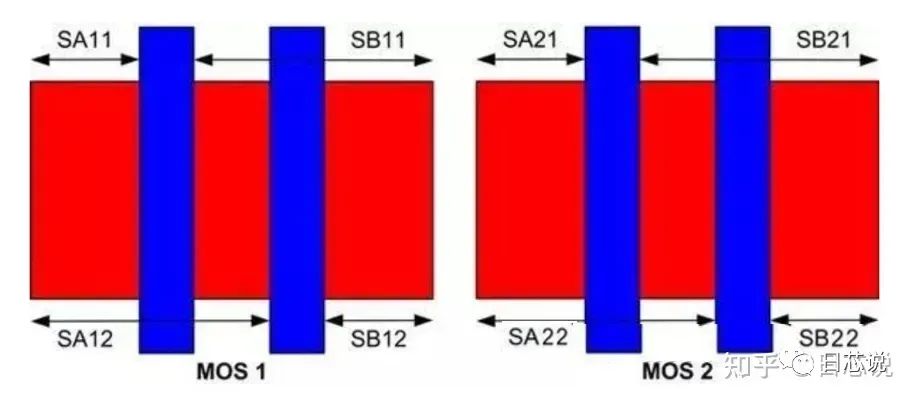

如果fingger=2會是什么情況呢?如下圖,M1和M2的finger都是2,且不共用源漏,分開放置,為了使得M1和M2匹配且不受LOD影響,那么我們在版圖中應該做到SA11=SA21,SB11=SB21,SA12=SA22,SB12=SB22,那么LOD對M1和M2的影響是一樣的,因此M1和M2就可以做到匹配了,Io=Ii就不會因為LOD造成誤差。

所以當我們要設計Io=Ii時,,不論是Single Finger或是Multi Fingers,我們主要保證MOS 1和MOS 2的Layout一模一樣即可避免LOD Effect所造成的Mismatch,即使MOS 1和MOS 2畫在同一塊OD也是如此。

如果我們想要做到Io=4Ii,且是多個finger的情況,在畫版圖的時候,為了節省面積,在電路圖源漏有短接的,在版圖中也會源漏共用。在這個電流鏡電路中,M1和M2的源端是短接的,因此在版圖中也是共用源端。

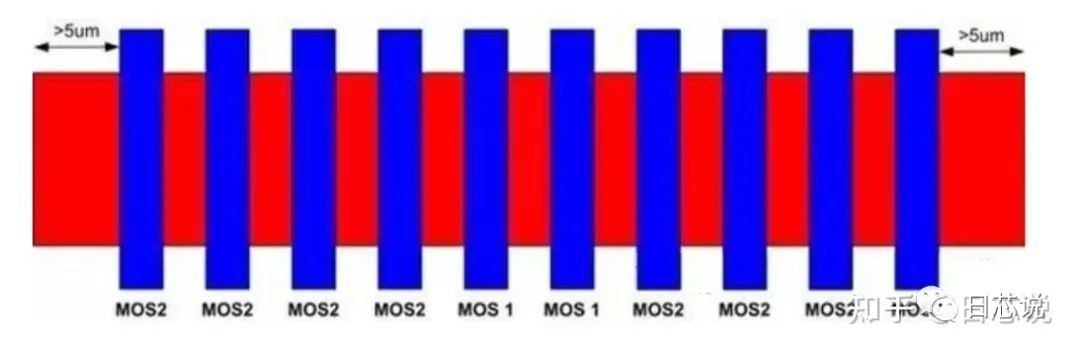

假設工藝要求中OD長度大于5um以上即可忽略LOD效應,那么如下圖,M1的finger是2,M2的finger是8,這樣做到了1:4的比例,且所有的finger的poly到STI的距離(即所有的OD長度)均大于5um,可以忽略LOD效應。

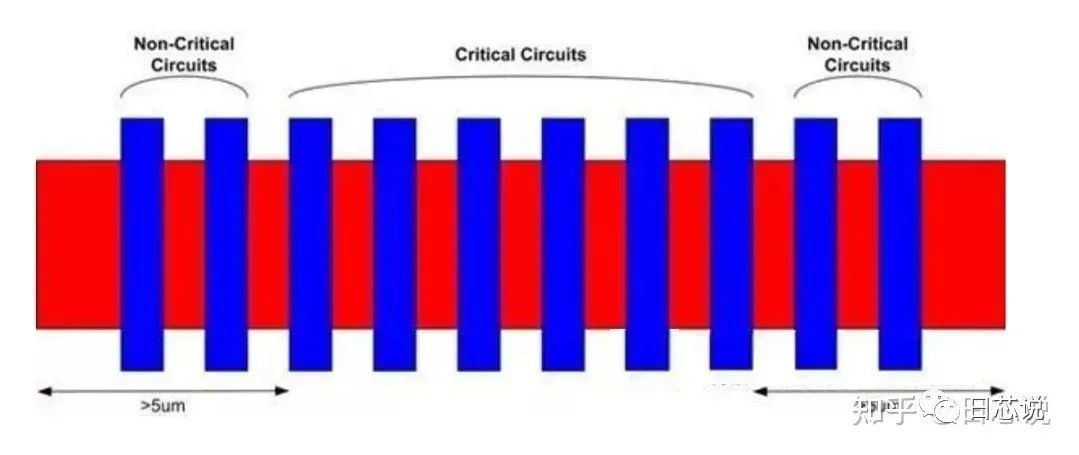

實際畫版圖時,管子兩側會放置dummy,這樣要保證了OD的長度夠長,且做到很好的匹配。

有同學會問了,兩側做到5um以上會不會太浪費面積,為什么1:4的比例不做成1:4而是2:8呢?能否做1:4呢?接下來分析這個問題。

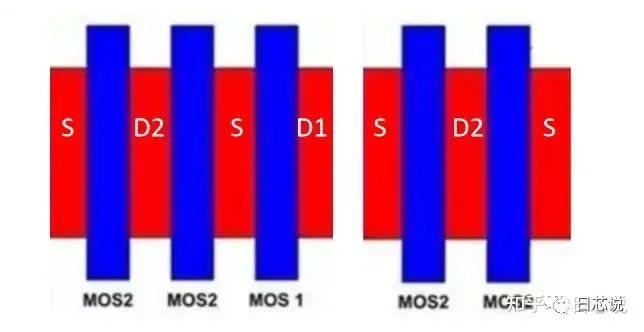

如果做成2:8的比例,即使兩側OD長度不大于5um,那么在兩側放上dummy,其實這時候LOD效應已經很小了,這種放置dummy的方法,如果采用1:4的比例,即M1的finger是1,M2的finger是4,那么版圖中會是以下的樣子,S代表M1和M2的源端,D1代表M1的漏端,D2代表M2的漏端。即使兩側放了dummy,LOD效應在M1和M2的影響也是不一樣的,因此不是完美的1:4的比例了。

-

MOS管

+關注

關注

109文章

2624瀏覽量

70708 -

電流鏡

+關注

關注

0文章

44瀏覽量

17573 -

DSM

+關注

關注

0文章

24瀏覽量

18255 -

LOD

+關注

關注

0文章

17瀏覽量

9697 -

Layout設計

+關注

關注

1文章

14瀏覽量

1701

發布評論請先 登錄

講一講嵌入式技術

講一講高級定時器的死區時間是怎么算出來的

講一講在FatFs文件系統下讀取SD卡的該如何做

C程序設計概述 第一講

第一講 數字電子技術緒論

講一講LOD效應

講一講LOD效應

評論