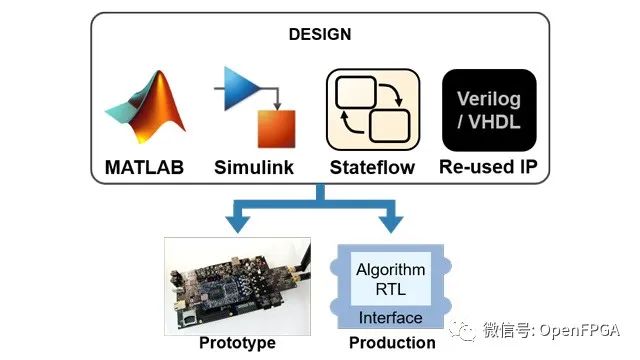

我們將使用實例講解MATLAB / Simulink HDL 使用入門。

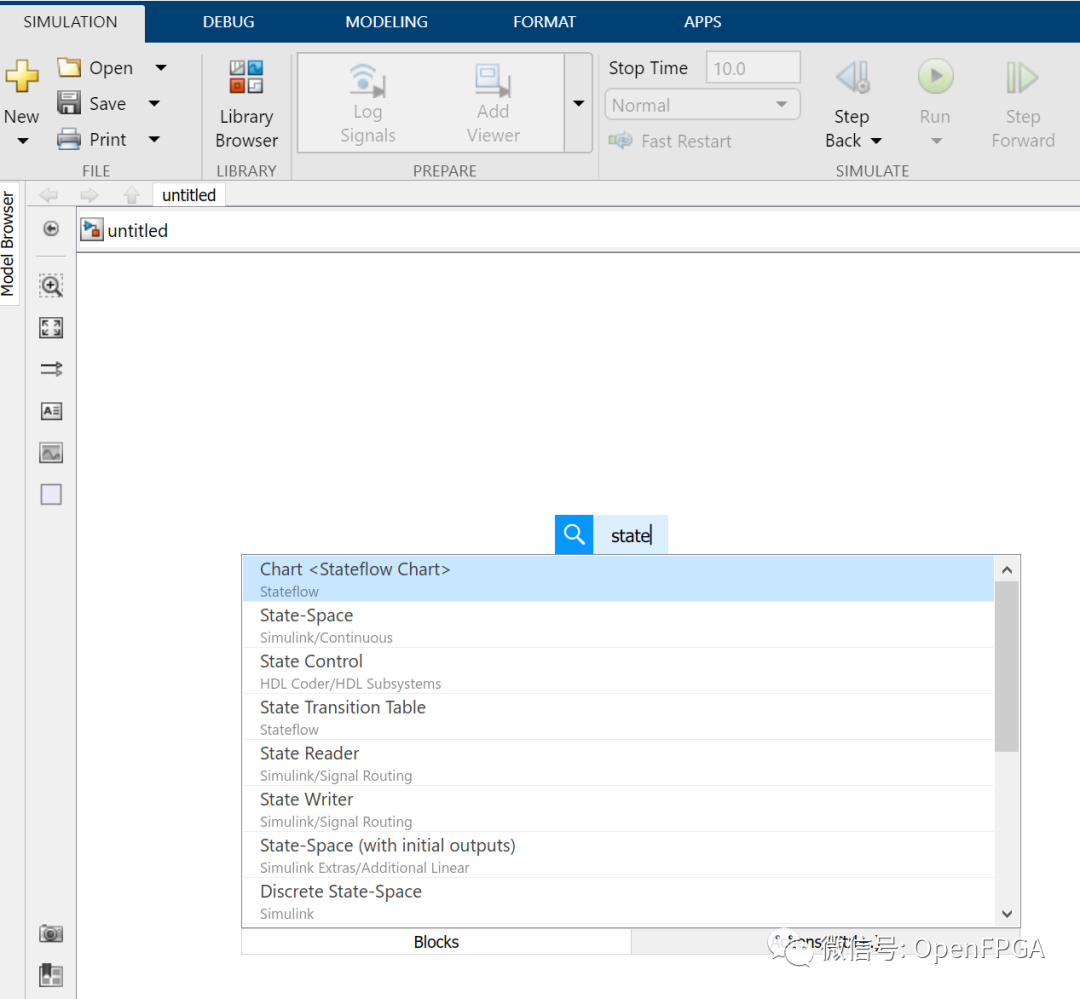

開始這個項目,首先需要創建一個包含 Stateflow 的新 Simulink 。只需單擊畫布中的任意位置并開始輸入 Stateflow。

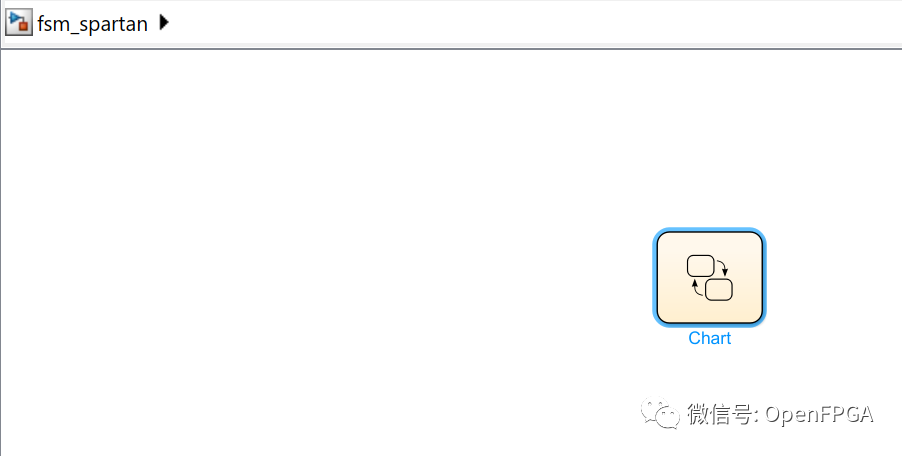

此時應該能在畫布上看到 Stateflow 圖標。雙擊圖標進行編輯。

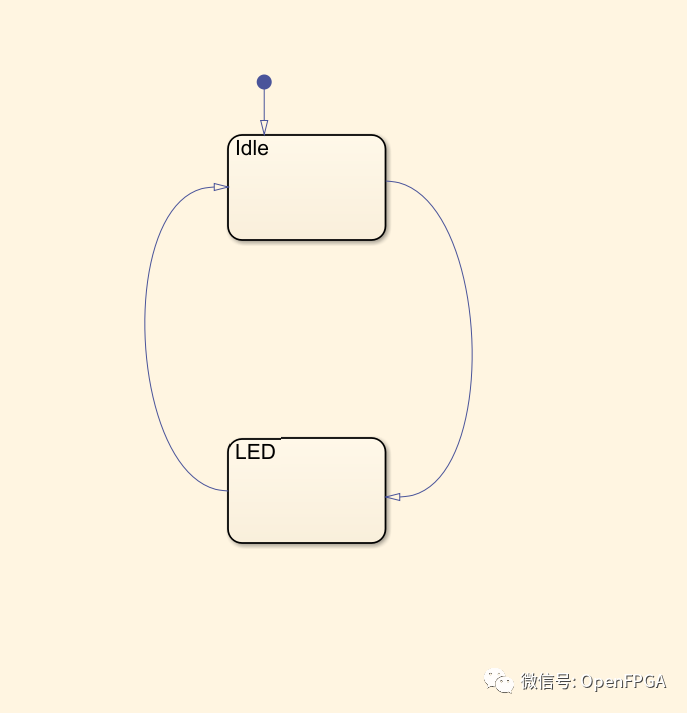

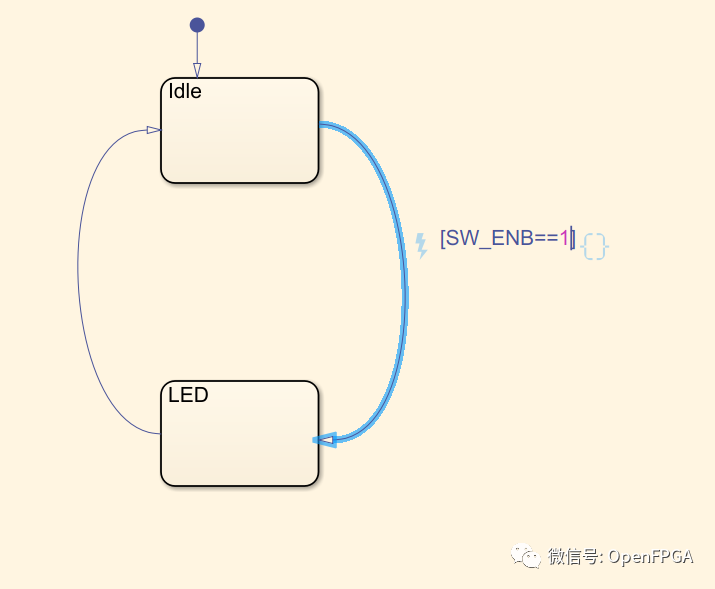

進入圖表編輯器后,可以添加狀態以及狀態之間的轉換。開始,我們創建兩種狀態并將它們命名為“idle”和“LED”。它們之間的轉換還沒有任何條件。

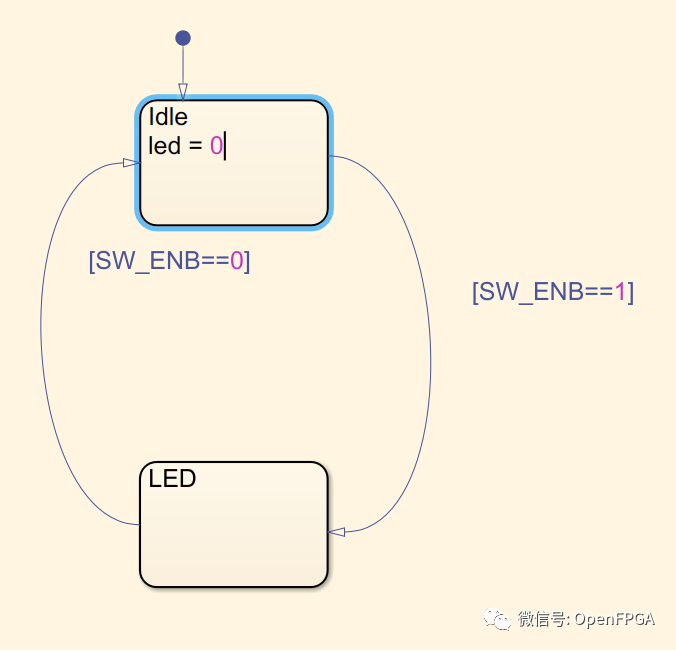

要添加狀態轉換條件,可以雙擊轉換并輸入所需的條件。

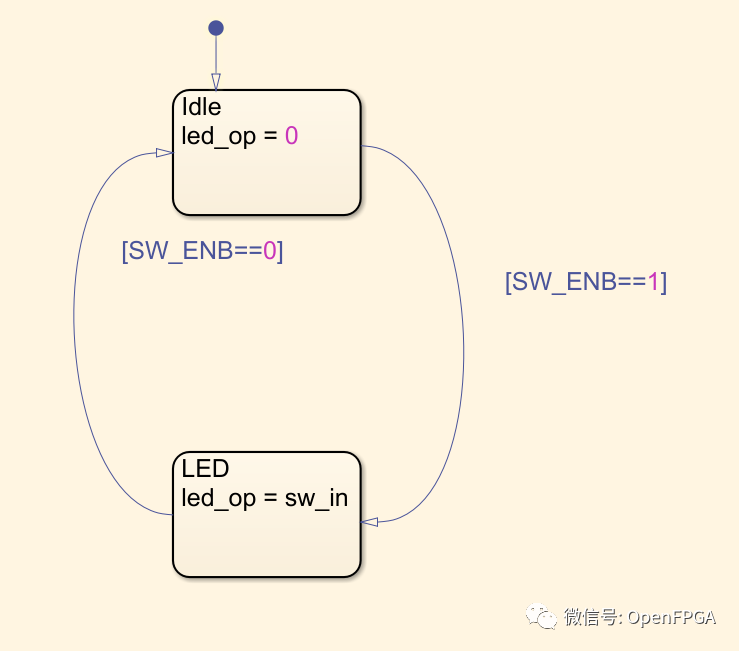

當然,狀態機可以具有 Mealey 和 Moore 輸出,這些輸出作為當前狀態 (Moore) 或當前狀態和輸入 (Mealey) 的函數出現。在本例中,將 LED 輸出聲明為 Moore 輸出,并在每個狀態下聲明。

最終的結果如下所示。

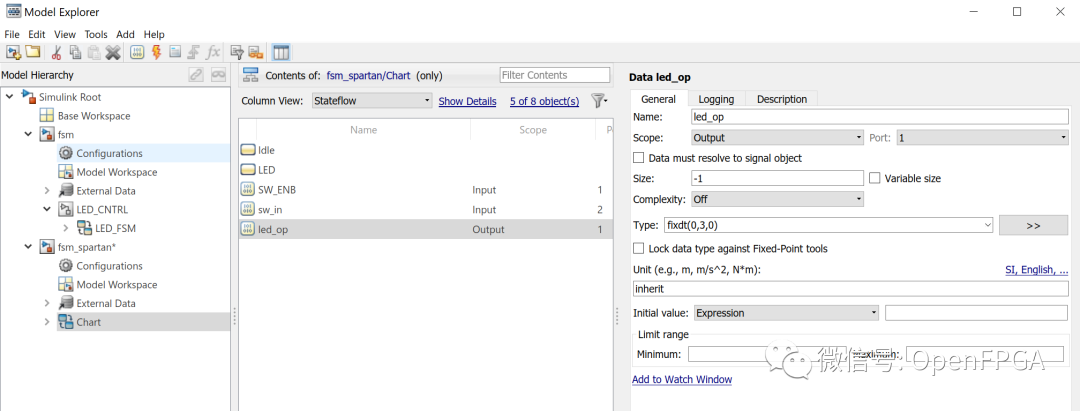

使用模型瀏覽器,我們可以定義狀態機的輸入和輸出。對于輸入,我們將它們保留為與 Simulink 相同的類型,但需要定義輸出。由于 LED 需要三位,因此我們使用類型 fixdt(0,3,0)。這意味著向量是三位寬、無符號的,并且沒有數字的小數元素。

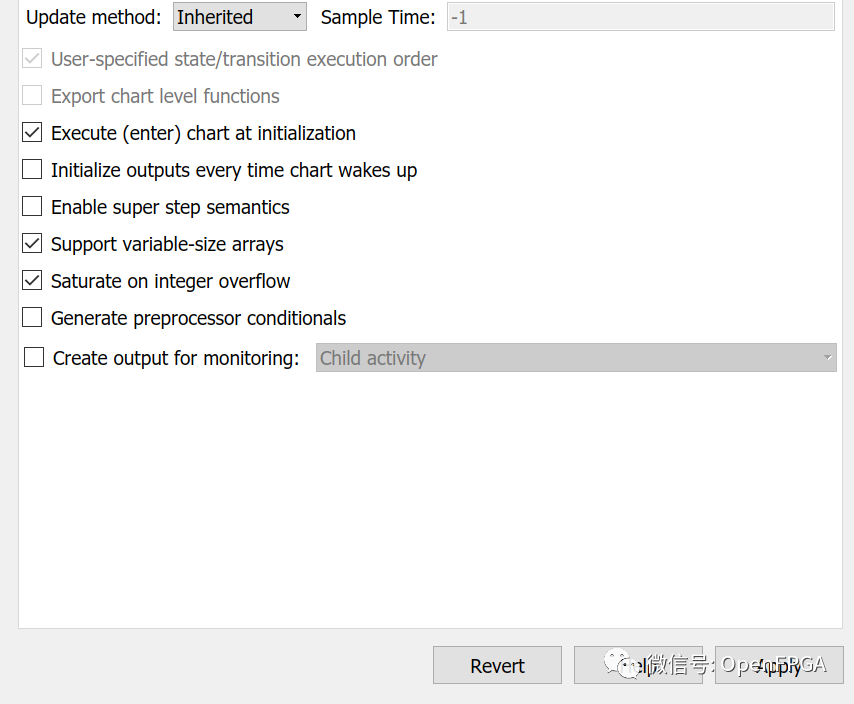

此外,在模型資源管理器中選中“初始化時執行(輸入)圖表”選項。

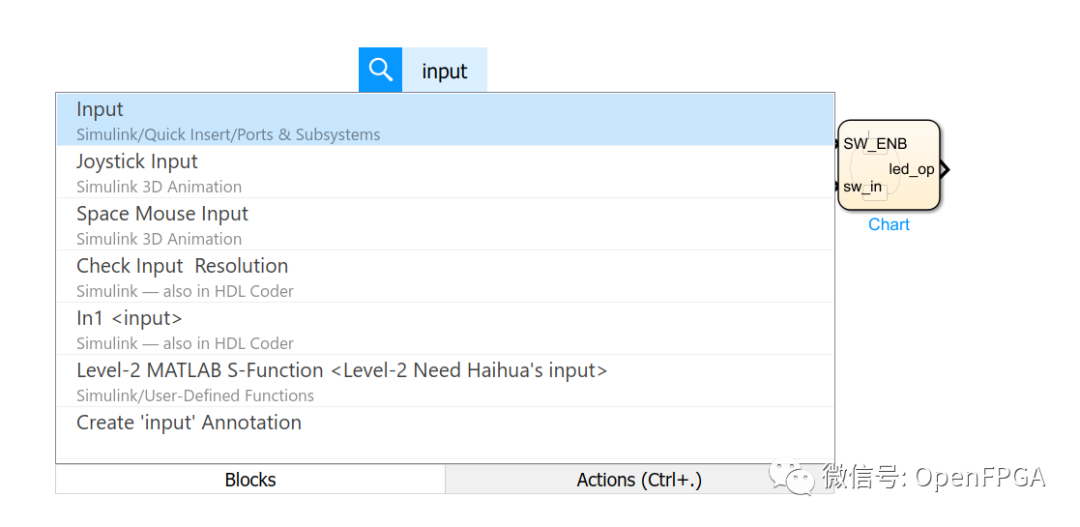

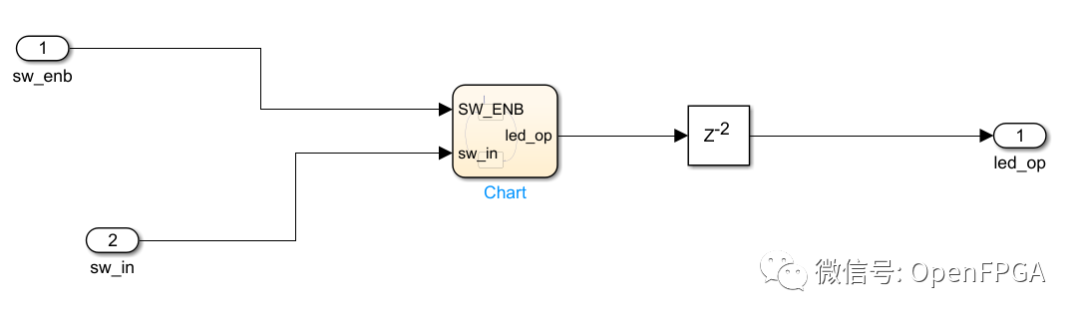

導航到圖表上方的畫布。這里我們需要添加塊的 IO,我們還將添加延遲。在畫布中,開始輸入輸入或輸出以獲取所需的端口。

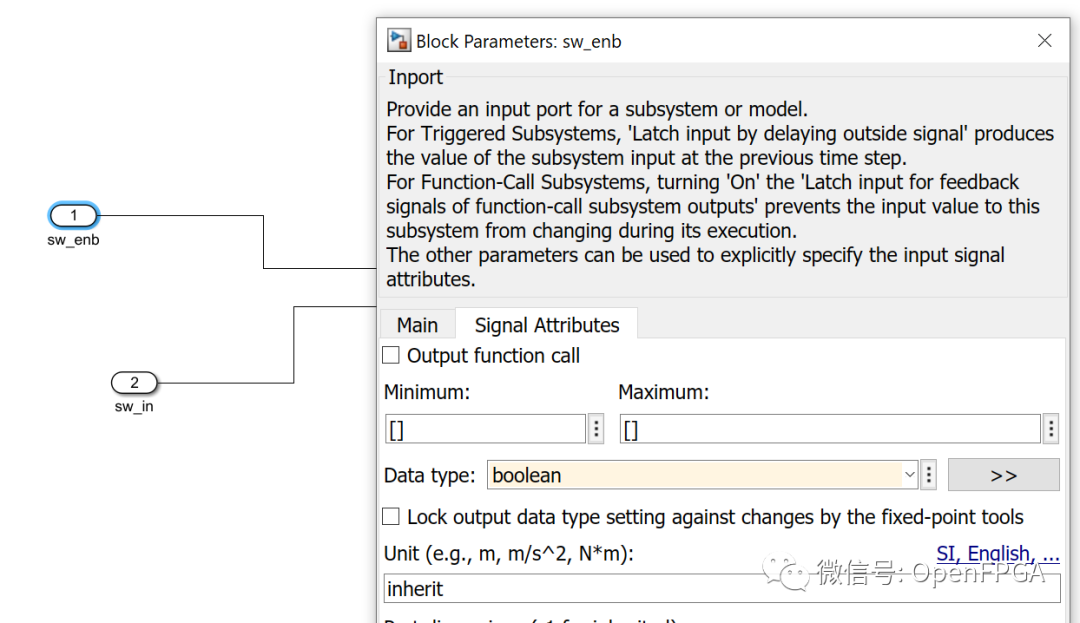

還可以通過雙擊輸入和輸出來命名端口,將其設置為正確的類型。

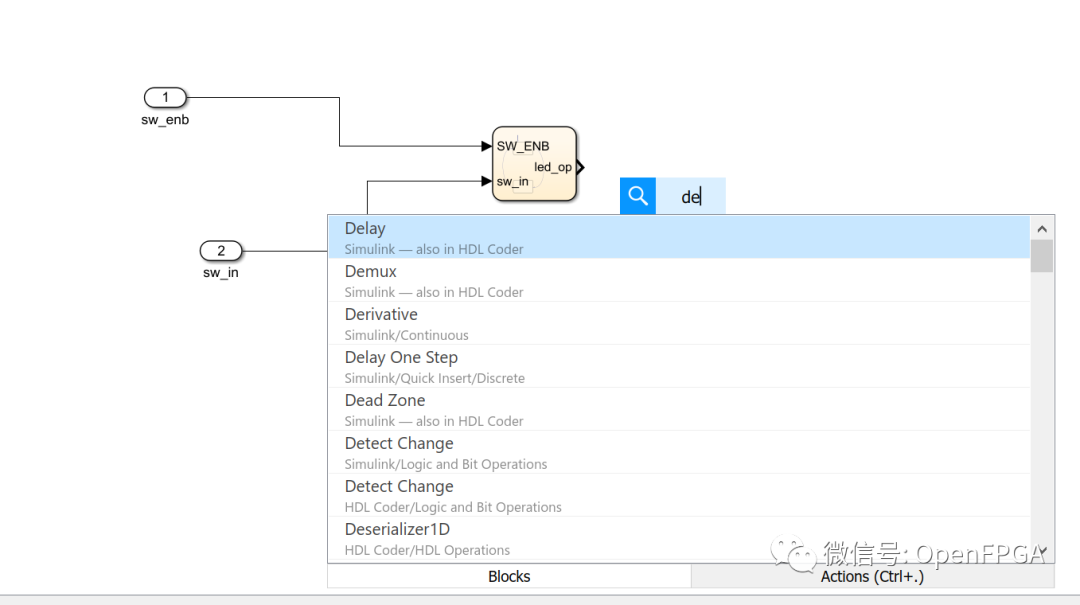

將 sw_in 設置為與之前聲明的輸出類型相同的 fixdt(0,3,0)。我們使用延遲來添加寄存器。要添加額外的延遲,只需在畫布中鍵入即可。

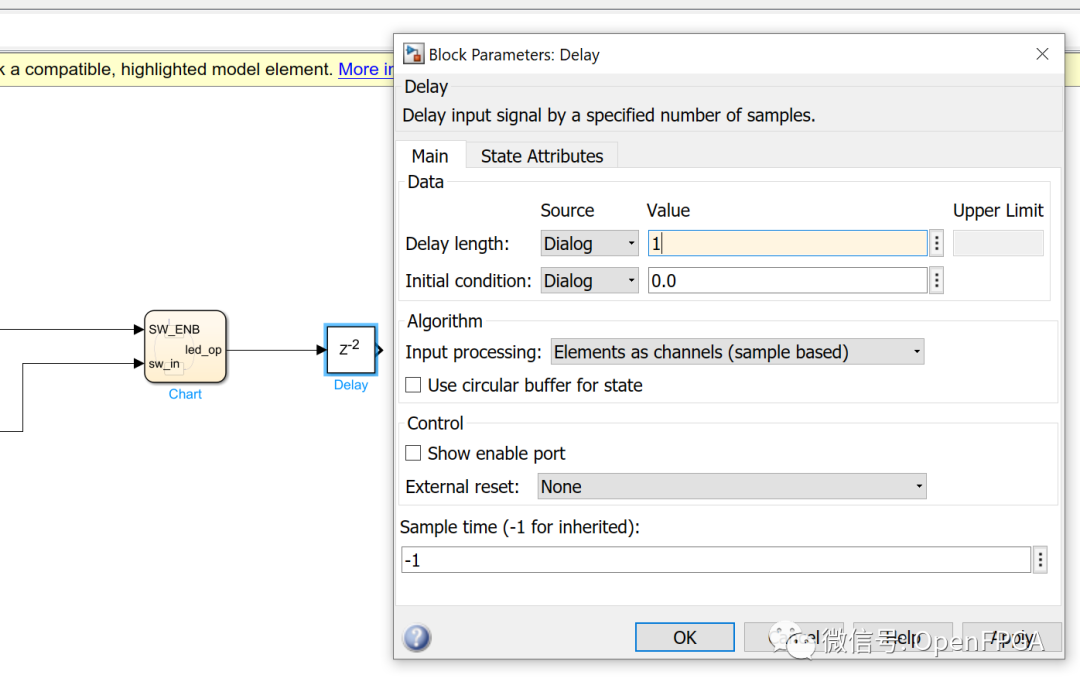

要更改延遲的長度,雙擊延遲并將其更改為延遲 1。

下圖顯示了完整的圖表。

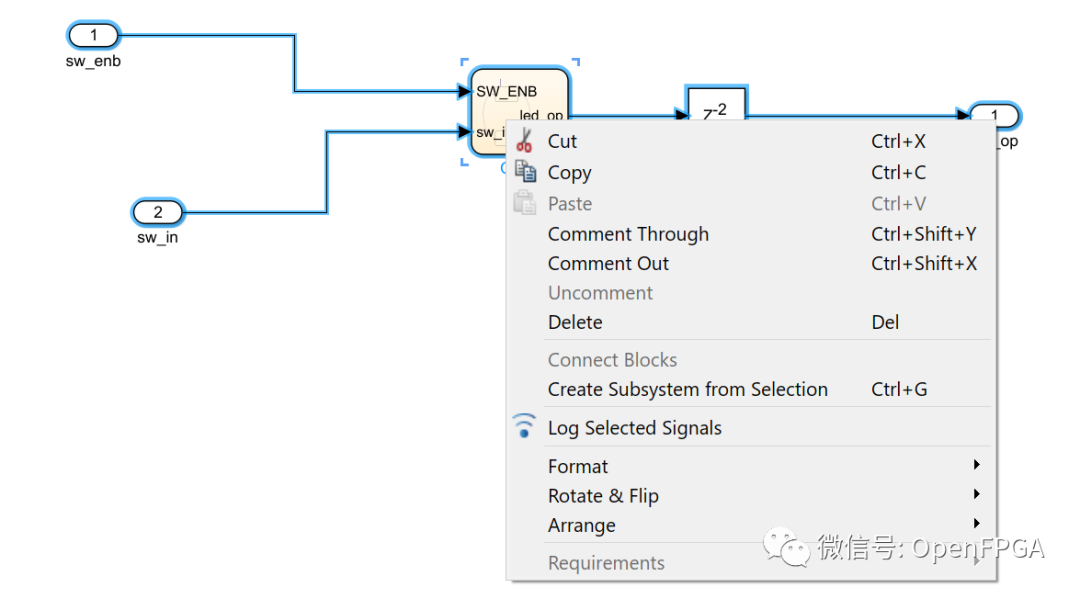

現在我們可以將其生成 RTL,但首先我們將為它創建一個測試平臺。選擇畫布上的所有元素,右鍵單擊它,然后選擇從選擇創建子系統。

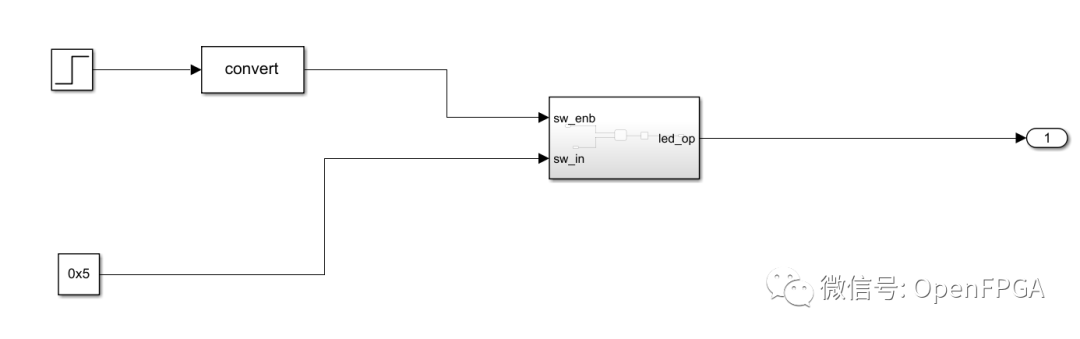

添加階躍函數和常數,設置子系統模塊中使用的模塊類型,并確保將離散采樣的采樣時間設置為 -1。

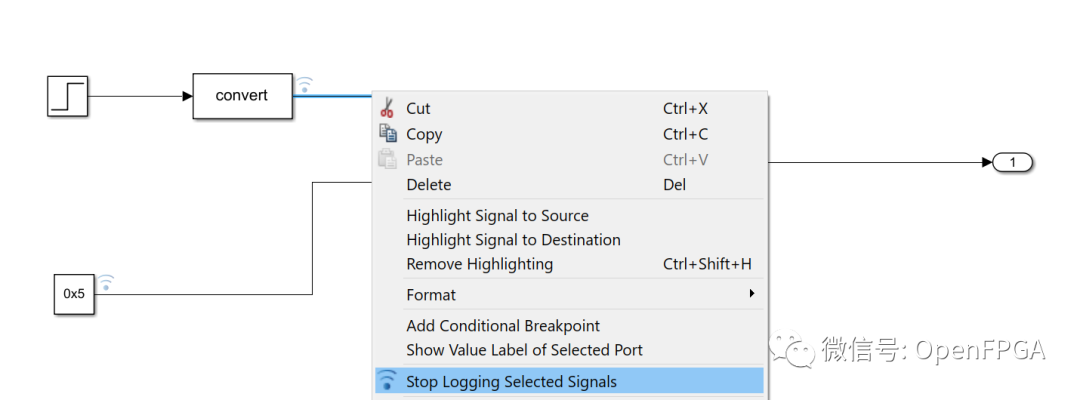

右鍵單擊感興趣的信號并選擇開始記錄所選信號。

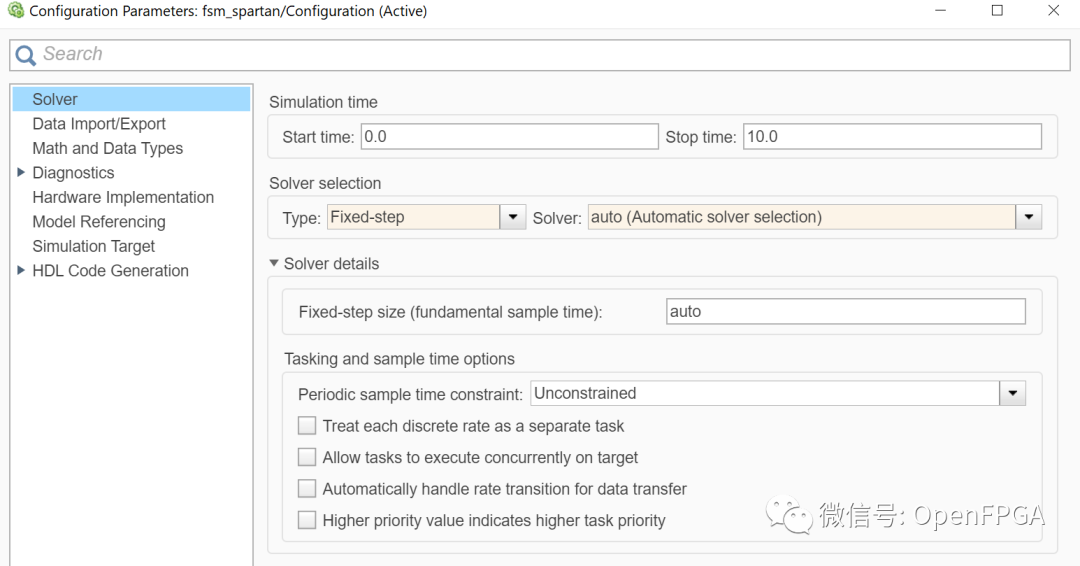

打開模型資源管理器并將模型設置為具有固定步長的計時器的離散時間。

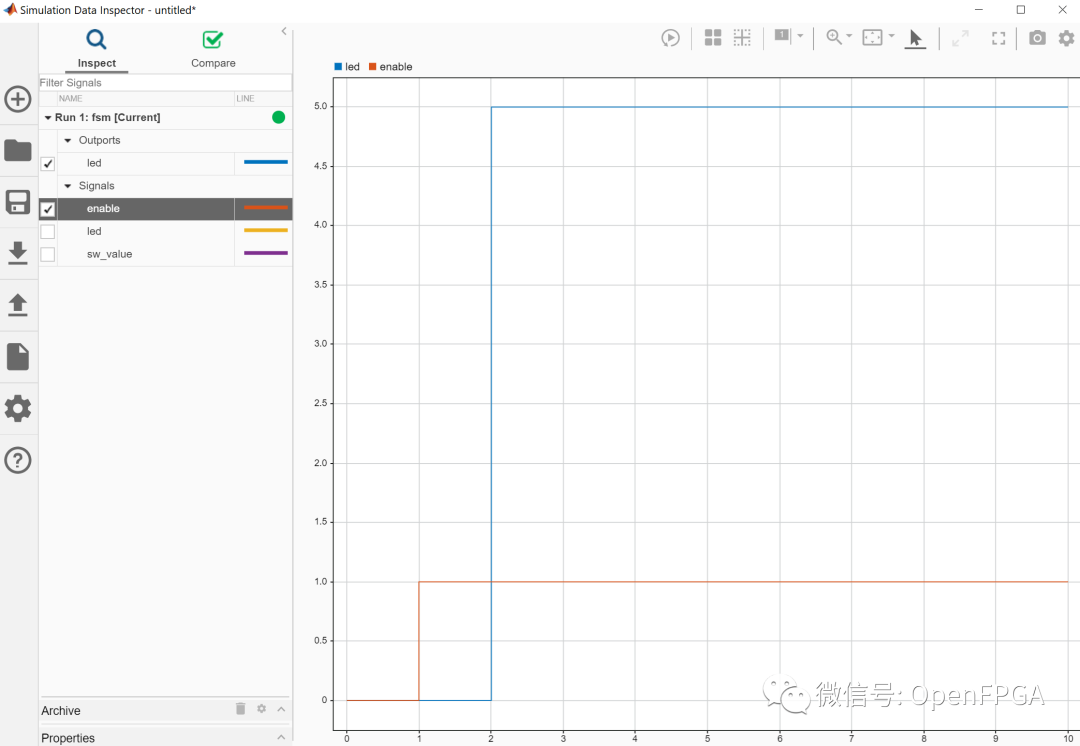

運行模擬并打開數據檢查器。應該能夠看到 SW_ENB 被置位,并且 LED 輸出在下一個時鐘后變高。

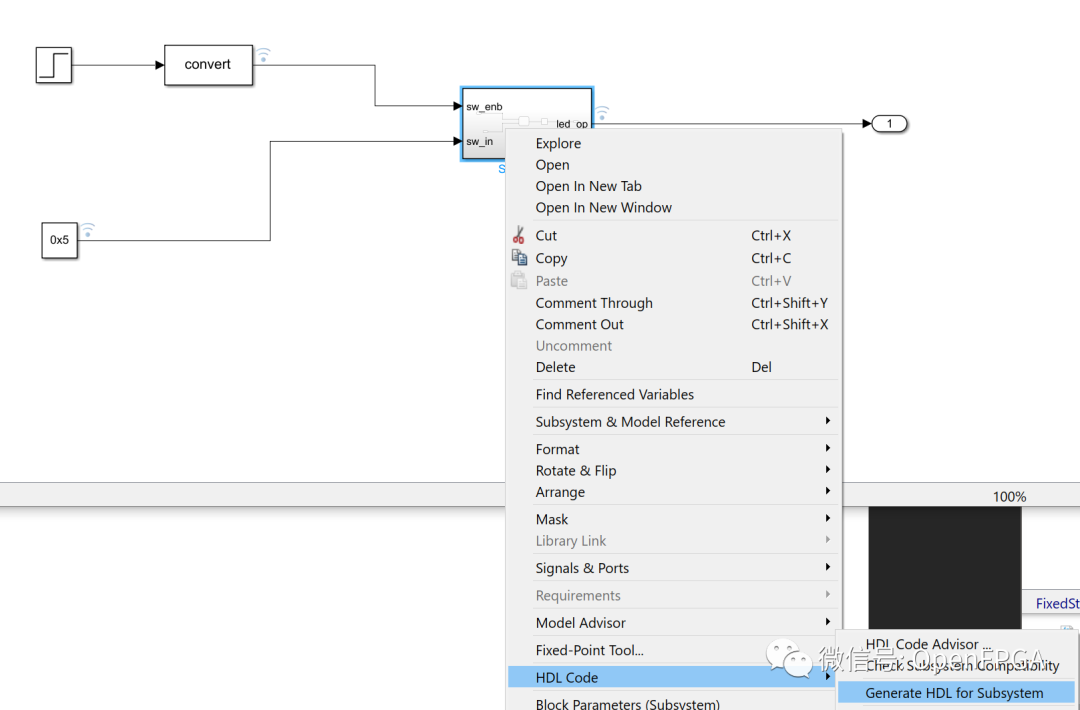

現在我們可以創建 HDL 并將其導出到 Vivado 中使用。我們可以通過右鍵單擊子系統并選擇為子系統生成 HDL 來完成此操作。

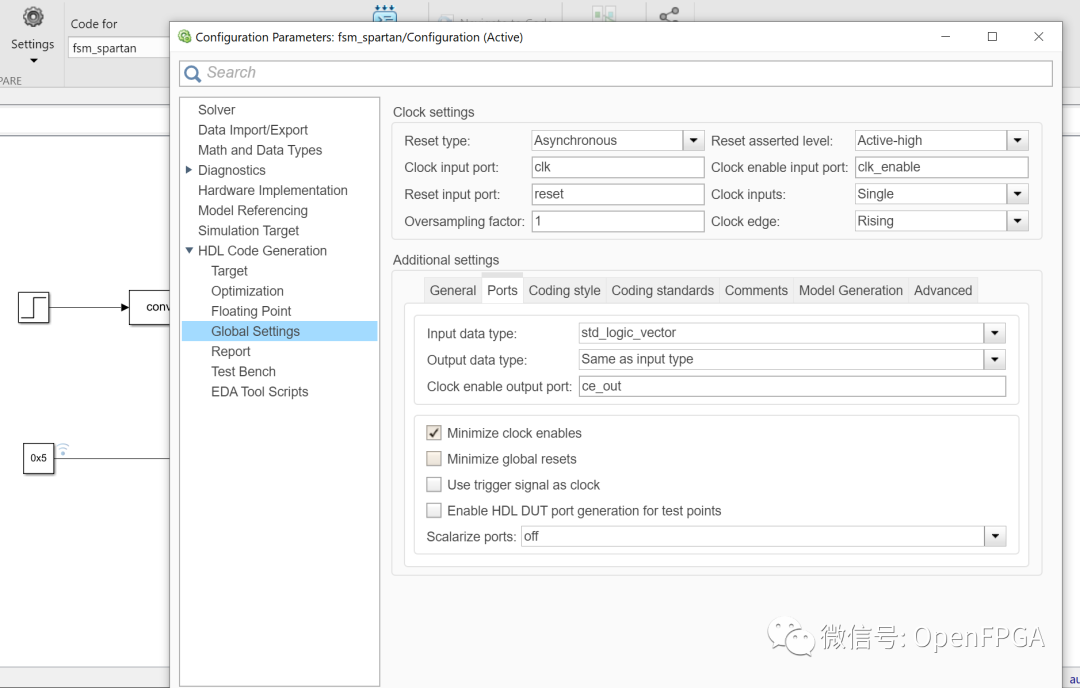

如果要更改任何生成的 HDL 代碼格式(即刪除時鐘啟用),需要從 HDL 代碼生成選項卡中選擇全局設置選項。

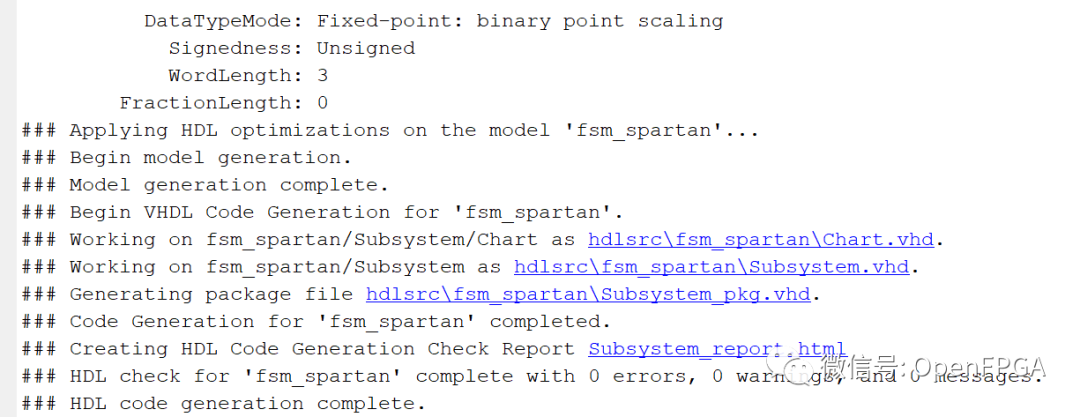

生成代碼后,將在生成代碼的 MATLAB 窗口中看到一條消息。

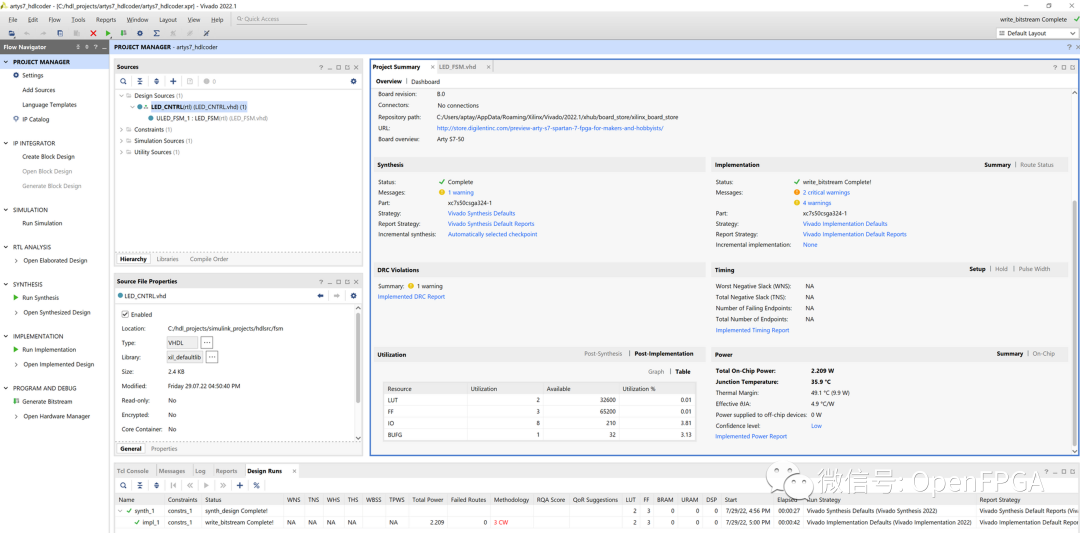

然后可以將該 HDL 導入到 Vivado 項目中。生成的代碼本身實際上是可讀的,并且取決于我們對 Simulink 圖的注釋程度。例如,我可以命名狀態圖,這將反映在case語句名稱中。

生成三個 VHDL 文件:包含聲明的包、實現狀態機的實際源代碼以及頂級文件。

在 Vivado 中進行綜合,最終設計需要三個觸發器和兩個 LUT。

當然,這是一個簡單的示例,但能夠學習流程,以便可以將它用于更復雜的應用程序。

-

led

+關注

關注

242文章

23762瀏覽量

671669 -

matlab

+關注

關注

188文章

2998瀏覽量

233463 -

HDL

+關注

關注

8文章

330瀏覽量

47877 -

文件

+關注

關注

1文章

578瀏覽量

25248 -

Simulink

+關注

關注

22文章

540瀏覽量

63725

原文標題:MATLAB / Simulink HDL 快速入門

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

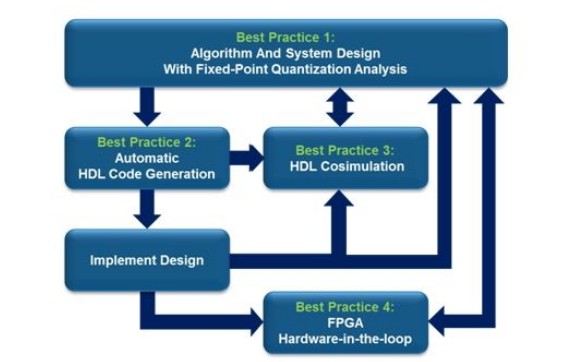

專家支招:使用MATLAB和Simulink算法創建FPGA原型

使用MATLAB Simulink和HDL編碼器創建自定義IP--AWB

初學者的MATLAB_Simulink翻譯

什么是MATLAB SIMULINK?Simulink有哪些應用實例?

淺析MATLAB和Simulink嵌入式視覺應用

基于MatLab/Simulink的GPS系統仿真

MathWorks發布在MATLAB和Simulink中提供

MathWorks推出基于MATLAB生成HDL代碼的產品

MATLAB教程之MATLAB語言的基礎知識及入門

講解MATLAB/Simulink HDL使用入門

講解MATLAB/Simulink HDL使用入門

評論