什么是"線與"邏輯,要實現(xiàn)它,在硬件特性上有什么具體要求?

線與邏輯是一種基本的數(shù)字邏輯電路,用于實現(xiàn)布爾代數(shù)中的邏輯運算。在線與邏輯中,當(dāng)所有輸入信號都是高電平時,輸出信號才為高電平;否則,輸出信號為低電平。這種邏輯運算與布爾代數(shù)中的“邏輯與”操作相對應(yīng),因此被稱為“線與”邏輯。實現(xiàn)線與邏輯需要滿足一些具體的硬件特性。

首先,為了實現(xiàn)線與邏輯電路,需要具備適當(dāng)數(shù)量的輸入和輸出端口。對于一個線與電路來說,一般至少有兩個輸入端口和一個輸出端口。這些端口應(yīng)該能夠接收和發(fā)送數(shù)字信號,因此需要具備足夠的帶寬和數(shù)據(jù)傳輸速率。

其次,對于線與邏輯電路來說,關(guān)鍵要求是能夠正確地檢測輸入信號的電平狀態(tài),并根據(jù)規(guī)定的邏輯規(guī)則生成正確的輸出電平狀態(tài)。為了實現(xiàn)這一點,電路中需要引入適當(dāng)?shù)妮斎刖彌_電路和輸出緩沖電路。輸入緩沖電路負(fù)責(zé)將輸入信號的電平狀態(tài)轉(zhuǎn)換為適合電路內(nèi)部處理的電平狀態(tài);而輸出緩沖電路則負(fù)責(zé)將電路內(nèi)部處理得到的輸出電平狀態(tài)轉(zhuǎn)換為適合外部系統(tǒng)接收的電平狀態(tài)。

此外,在線與邏輯電路中,必須注意輸入信號的時序關(guān)系。即輸入信號到達(dá)電路的順序和時間間隔必須滿足一定的要求,以確保電路能夠正確地判斷輸入信號的電平狀態(tài)。為了實現(xiàn)這一點,電路中需要引入適當(dāng)?shù)臅r序控制電路,用于對輸入信號進(jìn)行同步或延時控制,從而滿足電路的時序要求。

此外,還需要考慮線與邏輯電路的穩(wěn)定性和可靠性要求。穩(wěn)定性意味著電路在接收到合法的輸入信號后能夠保持正確的輸出狀態(tài);可靠性則意味著電路在長時間運行中能夠保持正常工作,不受干擾和噪聲的影響。為了提高電路的穩(wěn)定性和可靠性,可以采取一些措施,例如引入適當(dāng)?shù)?a href="http://m.xsypw.cn/tags/濾波器/" target="_blank">濾波器、隔離器和抗干擾技術(shù)。

在設(shè)計線與邏輯電路時,還需要考慮電路的功耗和面積要求。功耗是指電路在工作時所消耗的能量,面積是指電路所占用的物理空間。為了實現(xiàn)高性能、低功耗和小尺寸的電路,可以采用一些低功耗設(shè)計技術(shù)和高集成度的封裝技術(shù)。

總之,實現(xiàn)線與邏輯電路需要滿足適當(dāng)?shù)妮斎胼敵龆丝凇⒄_檢測輸入信號的電平狀態(tài)、考慮時序關(guān)系、保障穩(wěn)定性和可靠性、控制功耗和面積等要求。通過合理設(shè)計和應(yīng)用適當(dāng)?shù)挠布匦裕梢杂行崿F(xiàn)線與邏輯電路,并滿足布爾代數(shù)中“邏輯與”操作的要求。

-

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43222 -

緩沖電路

+關(guān)注

關(guān)注

1文章

77瀏覽量

20502

發(fā)布評論請先 登錄

常見電子類硬件筆試題整理(含答案)

從實驗室到生產(chǎn)線:聚徽廠家如何實現(xiàn)工控機(jī)技術(shù)的場景化落地

《2025年汽車標(biāo)準(zhǔn)化工作要點》發(fā)布,對自動駕駛行業(yè)提了啥要求?

上升沿時間在10ns以內(nèi)的電磁鐵驅(qū)動電路請教

如何選擇合適的PLD型號

請問LDC1000具體要怎么測距呢?

基于TPF632A 音頻驅(qū)動器的電源系統(tǒng)設(shè)計要點、具體要求

變壓器防雷接地電阻的具體要求有哪些?變壓器防雷保護(hù)措施包括哪些?

CDCI6214 REFP管腳是可以使用LVCMOS的單端輸入,輸入時鐘具體要求是什么?

簡述emc的概念,并說明emc的具體要求

影響共模電感阻抗大小的因素

邏輯電路芯片-組合邏輯電路芯片-時序邏輯電路芯片

安卓工業(yè)一體機(jī)在紡織機(jī)械設(shè)備上的應(yīng)用特點與具體要求

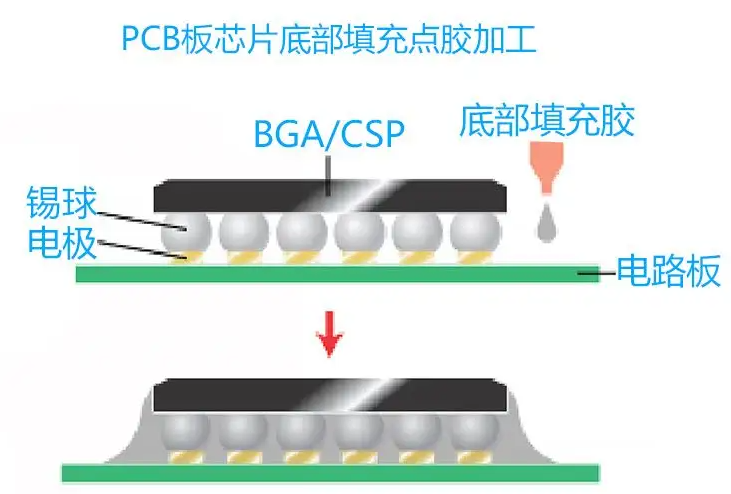

詳解點膠工藝用途和具體要求?

什么是線與邏輯?要實現(xiàn)它,在硬件特性上有什么具體要求?

什么是線與邏輯?要實現(xiàn)它,在硬件特性上有什么具體要求?

評論