最近弄PCIE,遇到一個問題,以前我們總認(rèn)為:Xilinx的PCIE core的管腳是固定的,即指定了PCIE core的位置,對應(yīng)的管腳也就指定了,真實情況是怎么樣的呢?

背景說明

硬件在分配PCIE的管腳的時候,沒有分配到xilinx推薦的對應(yīng)的管腳上,如何處理呢?是否只能改板?

背景介紹

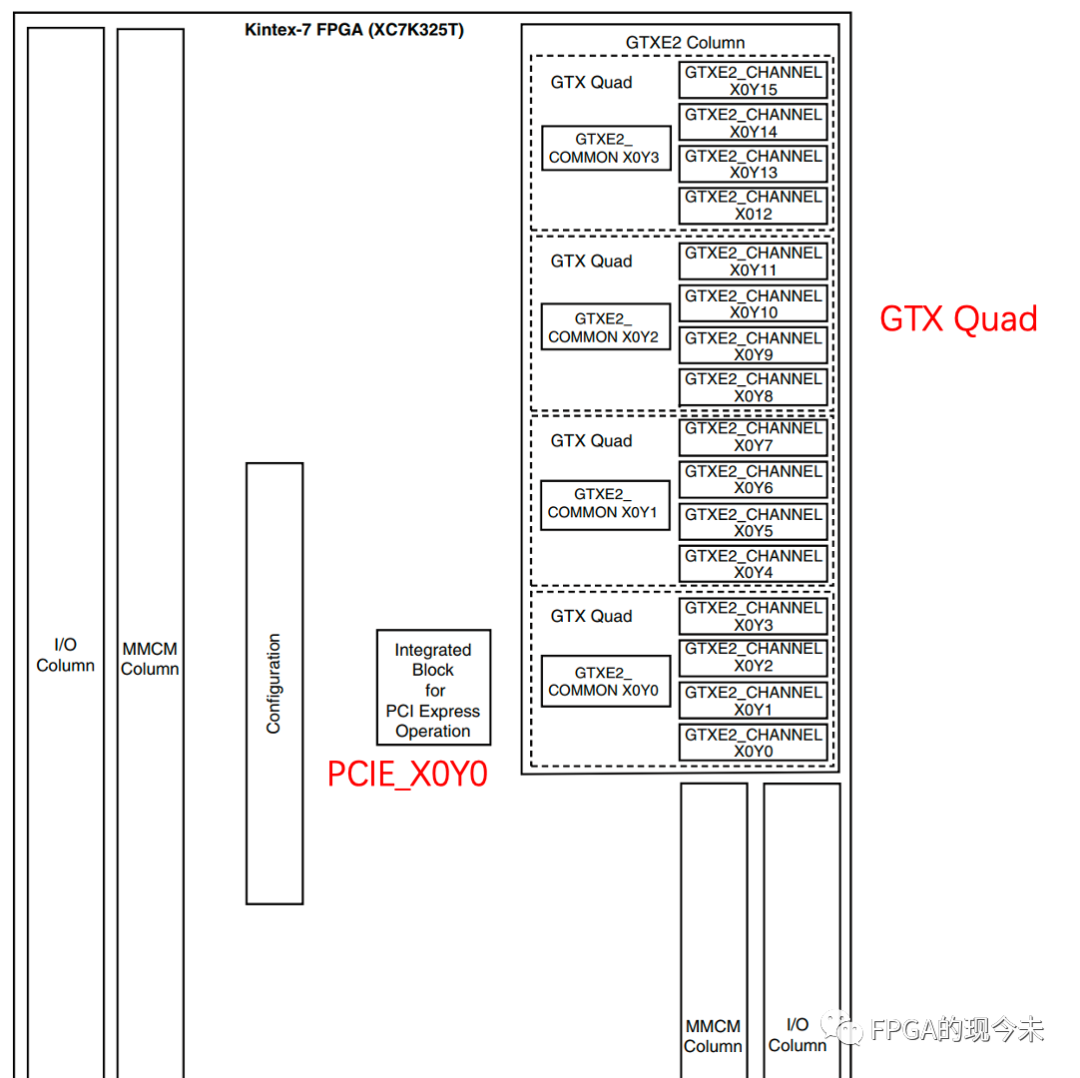

使用7系列的xilinx FPGA,需要用到PCIE core,計劃是使用xilinx提供的硬core,該系列的FPGA中只有一個硬core,所以沒得選擇,我們使用的是PCIE_X0Y0這個硬core,如下圖所示:

當(dāng)PCIE的位置確定以后,PCIE對應(yīng)的serdes位置也就“固定”了,有三種方式可以來查看這個“固定”位置。

第一、在PG054:7 Series FPGAs Integrated Block for PCI Express v3.2 LogiCORE IP Product Guide中,如下圖所示:我們可以看到,對于的K7系列的325T的器件,X4的recommended GT locationg是X0Y4/X0Y5/X0Y6/X0Y7

另外我們在文檔ug476:7 Series FPGAs GTX/GTH Transceivers中可以看到X0Y4/X0Y5/X0Y6/X0Y7對應(yīng)的管腳如下圖所示:

第二種方式,直接綜合PCIE core,綜合后,查看綜合結(jié)果,如下圖所示,我們可以看到,在不對PCIE core做任何約束的情況下,該PCIE默認(rèn)的管腳也是在channel X0Y4-——X0Y7所在Quad上。其pin的約束和上圖一致。

還有第三種方式,通過xilinx提供的example design來確定對應(yīng)的管腳約束,通過查看example design的約束,我們發(fā)現(xiàn)關(guān)于位置的約束就只有如下一行,它約束的差分時鐘雙端轉(zhuǎn)單端的refclk_ibuf,位置為IBUFDS_GTE2_X0Y3,這個剛好也位于MGT_BANG_116。

set_property LOC IBUFDS_GTE2_X0Y3 [get_cells refclk_ibuf]

結(jié)論:K7系列FPGA對于X4的PCIE,其默認(rèn)的約束就是在MGT_BANG_116,

問題

硬件在管腳分配的時候,沒有按照Xilinx默認(rèn)的管腳分配原則分配在MGT_BANG_116,而是分配到了MGT_BANG_118上(第一張圖中,右邊的4個gtx quad從上到下分別是118/117/116和115)。

解決方案

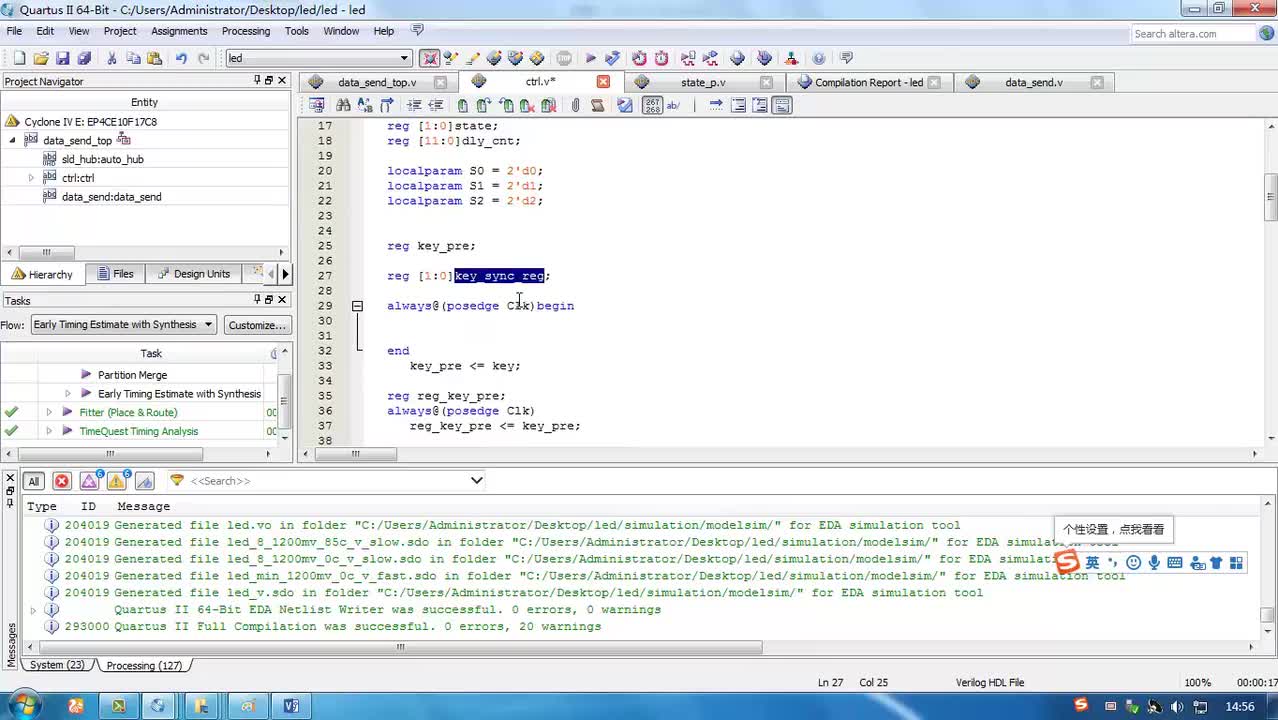

pcie core和所用的gt是分開的,我們可以通過約束channel的位置來改變所使用的channel,從而改變pcie的管腳。約束如下所示,只需要綁定channel和pcie對應(yīng)的lane即可,通過約束發(fā)現(xiàn)imp階段工程是可以通過的。

set_property LOC GTXE2_CHANNEL_X0Y12 [get_cells {***/pcie_core/pcie_7x_1_i/inst/gt_top_i/pipe_wrapper_i/pipe_lane[0].gt_wrapper_i/gtx_channel.gtxe2_channel_i}]

測試結(jié)果

通過實際上板測試,pcie core能正常link up,進(jìn)行業(yè)務(wù)測試收發(fā)數(shù)據(jù)也正常,不過這里也有一個風(fēng)險,通過device視圖我們可以看到,MGT_BANG_118所在的quad是離pcie core最遠(yuǎn)的quad,尤其是兩者之間資源比較多的時候,布線會比較多,這必然導(dǎo)致時序風(fēng)險。

結(jié)論

1、pcie的管腳有xilinx推薦的最佳約束位置,分配管腳的時候應(yīng)該嚴(yán)格按照推薦的規(guī)則來分配;

2、如果硬件把管腳弄錯了,可以通過約束來修改pcie core的默認(rèn)管腳,但是資源緊張的時候可能有時序風(fēng)險。

-

FPGA

+關(guān)注

關(guān)注

1644文章

22002瀏覽量

616018 -

Xilinx

+關(guān)注

關(guān)注

73文章

2184瀏覽量

124715 -

PCIe

+關(guān)注

關(guān)注

16文章

1331瀏覽量

84869 -

管腳

+關(guān)注

關(guān)注

1文章

230瀏覽量

32645

發(fā)布評論請先 登錄

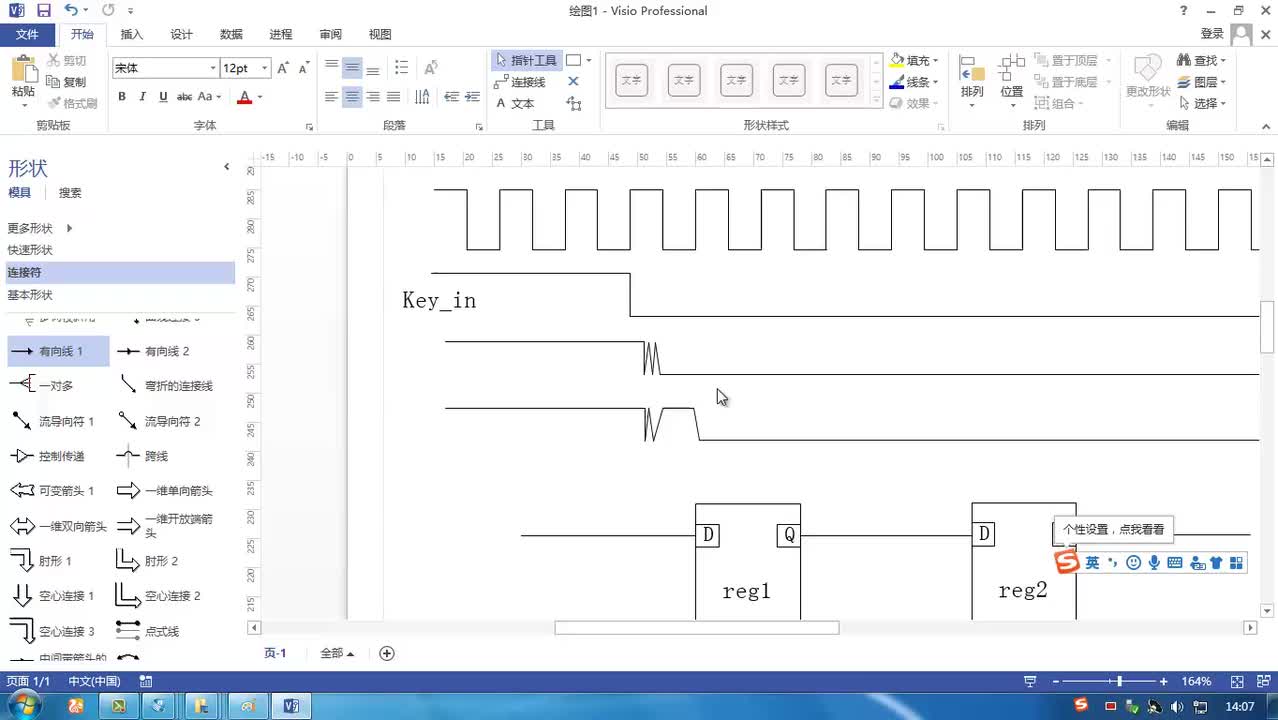

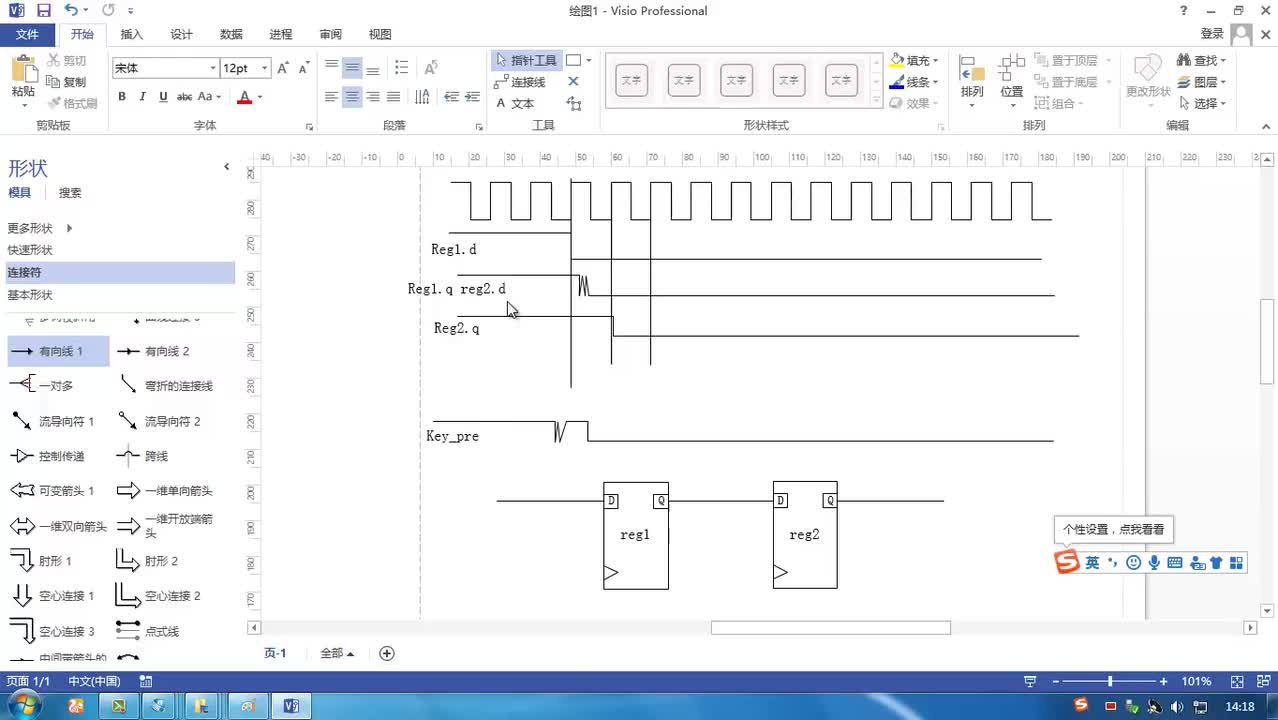

#硬聲創(chuàng)作季 #FPGA Xilinx入門-16 亞穩(wěn)態(tài)現(xiàn)象原理與解決方案-1

#硬聲創(chuàng)作季 #FPGA Xilinx入門-16 亞穩(wěn)態(tài)現(xiàn)象原理與解決方案-2

#硬聲創(chuàng)作季 #FPGA Xilinx入門-16 亞穩(wěn)態(tài)現(xiàn)象原理與解決方案-3

#硬聲創(chuàng)作季 #FPGA Xilinx入門-16 亞穩(wěn)態(tài)現(xiàn)象原理與解決方案-4

#硬聲創(chuàng)作季 #FPGA Xilinx入門-16 亞穩(wěn)態(tài)現(xiàn)象原理與解決方案-5

xilinx ddr2硬核管腳問題

用于 Xilinx FPGA Zynq 7 的電源解決方案

xilinx,ddrmig文件中管腳分配

化PCIe應(yīng)用中的時鐘分配方法

怎么使用一個多點信號來分配PCIe時鐘?

怎么使用一個多點信號分配PCIe時鐘?

Xilinx FPGA是否有任何選項或可能的解決方案?

PCIE高速傳輸解決方案FPGA技術(shù)XILINX官方XDMA驅(qū)動

基于Core的動態(tài)內(nèi)存分配方案

Xilinx PCIE core管腳分配錯誤的解決方案

Xilinx PCIE core管腳分配錯誤的解決方案

評論