圍繞 3D異構集成(3DHI:heterogeneous integration )的活動正在升溫,原因是政府的支持不斷增加、需要向系統中添加更多功能和計算元素,以及人們普遍認識到,除了將所有內容都封裝到單個 SoC 中之外,還有更好的前進道路。相同的進程節點。

在過去的幾年里,芯片設計的前沿發生了巨大的變化。國際競爭正在推動對在岸上或友好地點設計、制造和封裝的更先進芯片的投資。DARPA 微系統技術辦公室剛剛宣布了其下一代微電子制造 ( NGMM ) 計劃,旨在通過建立國內開放式原型設計和試驗線中心來推進最先進的 3DHI 微電子技術,該中心可供美國用戶使用學術界、政府和工業界。熟悉該計劃的人士表示,它正在刺激整個半導體生態系統建立新的合作伙伴關系。

這只是最終將影響整個芯片行業的復雜、多層次轉變的一個方面。全球的設計團隊才剛剛開始理解半導體設計的新未來,這需要深入了解 3D 異構設計中的權衡和不斷增加的可用選項。

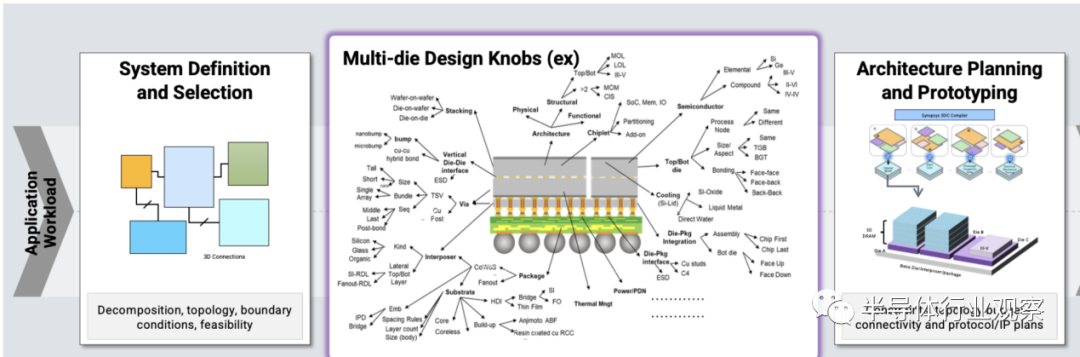

“您嘗試進入 3DHI 的原因是因為您有一些 PPA 目標,或者說您想要擁有的成本優勢,”Synopsys 產品管理高級總監 Shekhar Kapoor說道。“重點是什么是最優化的設計。它從前面開始。說“我要分解”很容易。但你如何決定呢?如果這樣做,整個 IC 設計范式很快就會轉變為系統設計范式。在這個層面上,通過軟件/硬件設計,您將處理哪些工作負載?您需要什么小芯片?那里沒有小芯片的市場。即使您使用從其他地方可用的子系統,它如何適合您所考慮的總體范圍?”

成本仍然是每個人最關心的問題,但在系統環境中存在更大的靈活性。“成本始終很重要,” Cadence定制 IC 和 PCB 部門產品管理小組總監 John Park 說道。“但在過去,封裝的目的就是成本最低。人們現在愿意為封裝多付一點錢,尤其是大批量的產品。”

3DHI 還為外形尺寸的更大靈活性打開了大門,這反過來又可以對整體設計產生重大影響。

“例如,如果您要將某些東西放入智能手機中,則需要更薄、更輕的外形,”Park 指出。“如果它是放在架子上的東西,也許你不需要相同類型的配置文件。如果存在內存帶寬問題,您必須找出最佳內存以及將其組合在一起的最佳 DRAM 策略。有很多不同的選擇,包裝仍然是狂野的西部。有些人會認為包裝的選擇太多,但產品有很多不同。如果你要在衛星中放置一些東西,那么它必須非常堅固,并且必須能夠持續 50 年并且更加可靠。這取決于你正在設計什么,你的最終產品是什么,然后通常會得出成本,以及外形尺寸、尺寸、重量和功率,以及隨之而來的所有其他因素。”

西門子 EDA產品營銷經理 Keith Felton將其分為兩個領域。“首先是設備之間的機械集成,”他說。“它們會與基板、封裝或其他芯片/小芯片連接嗎?是否需要微凸塊,還是需要直接或混合鍵合?封裝平臺技術將決定其中的一些,就像您互連的芯片/小芯片一樣。”

第二個領域是通信協議——UCIe、BoW、AIB 等。“如果涉及 HBM,您將需要一個硅中介層或橋作為 PHY 之間的機械接口,這將部分決定機械集成技術,”Felton說。“如果您的架構需要直接芯片到芯片集成(晶圓上芯片或晶圓上晶圓),那么很可能需要直接或混合鍵合。集成將影響芯片/小芯片的設計和引腳輸出,因此使用支持參數化、自生成引腳區域的設計工具可以讓設計人員/架構師以最小的努力或成本探索多種集成場景。”

架構選擇很重要

與過去不同的是,許多設計決策都是連續且孤立的,3DHI 需要更廣泛地了解所有部分如何組合在一起。設計工程師必須成為系統工程師,他們必須處理各種需要與具有不同專業知識的工程師合作的問題,例如機械工程或軟件專業知識。

“如果你把它分解成太多的小部分,不僅封裝的集成真的很難做到,而且這些互連也會帶來開銷——額外的功率開銷,以及增加的一點延遲,”是德科技高速數字仿真技術產品經理 Stephen Slater說。“你必須根據重要的功能來挑選它。”

Slater指出,開發大型 ASIC 的芯片制造商知道自己的良率是多少,也知道自己的目標是什么。改變的是,他們現在必須弄清楚要分解哪些部分,以及他們愿意犧牲哪些部分來增加額外的 PHY 和復雜的高級封裝所需的功率。

“(行業)清楚的一件事是,沒有其他出路,”他說。“確實只有這個辦法了。已經有人在向墻壁開槍了。它們已經達到了巨大的標線尺寸。他們不能做得更大。這就是前進的方向。對于其他人來說,轉折點將是在他們未來的 ASIC 中,他們擔心收益率會是多少。從那時起他們就開始考慮分手。”

但 3DHI 增加了一個全新的復雜性軸。數據將如何流經該系統(該系統可能是使用不同工藝技術開發的 2D 和 3D 元素的組合)?還有很多事情會出錯,從機械問題到片上網絡死鎖(deadlocks)。

Arteris產品管理和戰略營銷高級總監 Guillaume Boillet 表示:“這些死鎖是可怕的小錯誤,它們會阻止數據包流動并導致整個系統停止運行。”他指出,這些死鎖有兩種類型:拓撲死鎖和協議死鎖( topology and protocol deadlocks)。“雖然拓撲死鎖特征在小芯片中通常是基本的,但只需要一個端口就可以形成環。

如果兩個不同的供應商對規范的解釋存在分歧,那么它很可能會出現錯誤。在協議死鎖方面,人們正在努力簡化跨小芯片的數據流的性質。盡管如此,新生的規范仍然很復雜,基于文本,因此可以進行解釋。正如我們過去所看到的,每次橋接協議時,都存在未涵蓋極端情況的風險。”

在宏觀層面上,Cadence的Park 相信每個人對于 3DHI 都有或多或少相同的目標。但確定優先級可能很棘手。“如果你想節省成本,那么成本就成為了你的目標。如果您希望獲得最高性能,那么性能會優先于它。熱量開始發揮作用。如果您在服務器場中使用可以進行液體冷卻的設備,請全力以赴地提高性能。如果你要在智能手機中放入某些東西,最好不要太熱,以免在觸摸手機時燙傷你的手。”

隨著選擇數量的增加,封裝的權衡變得更加混亂。

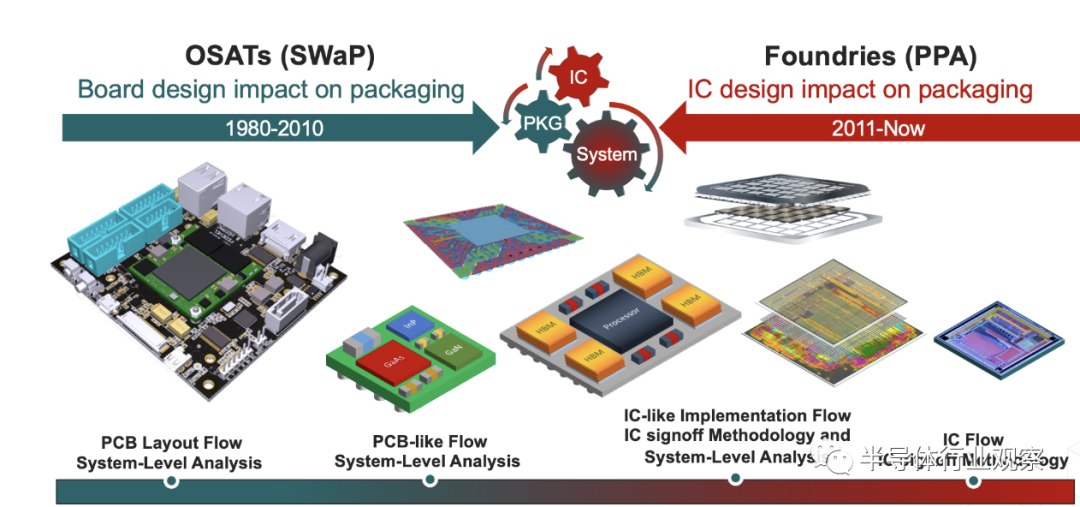

“在過去的半導體時代,每隔幾年我們就會得到一個新節點,就是這樣,”Park說。“封裝在不斷發展——尤其是現在晶圓廠已經進入世界各地。因此,我們每年可能會獲得六到十幾種新的封裝技術。隨著代工廠和現在的 OSAT 不斷增加其封裝選項組合,這是一個不斷發展的事情。它曾經是相當有限的。它主要是基于層壓板的基板,但現在有了將原廠和 3D 堆疊,您就有了所有這些不同的選擇。有了中介層,我會變成玻璃嗎?我要選擇硅嗎?我應該使用薄膜 RDL 中介層嗎?薄膜層壓板?每個封裝層都會增加成本和復雜性,具體取決于您計劃做什么。如果我今天能給你一些選擇,明天它就會改變,因為有人會想出另一種新方法。你有代工廠,有 OSAT,然后是這些封裝技術公司——像 Deca 這樣的公司,推出了一種新的封裝方式。”

封裝對 3DHI 系統中設備之間接口的技術規范有直接影響。

“如果你只是談論物理引腳間距,如果我有超密集、高帶寬類型的設計,我通常需要使用硅類型的基板,”Park 解釋道。“這意味著如果我采用硅基板(又名高級封裝),我可以采用 45 微米或 35 微米的凸塊間距。如果我繼續使用層壓板,則間距為 125 微米。因此,封裝決定了引腳的密度,這當然會影響其他因素,例如帶寬。”

這里發揮作用的其他考慮因素包括通信接口,它指的是 UCIe、BoW、AIB 等。

“有了這些通信接口,事情就變得一樣了,”Park 說。“UCIe 有標準封裝(間距約為 130 微米)和高級封裝(間距更像是 40 微米)。然后它會變得更加復雜,因為你有橋,并且與橋連接的芯片部分可以具有非常小的節距,而位于層壓板其余部分上的部分必須具有更大的節距。因此,您會看到這些多間距芯片和小芯片開始采用它們所采用的封裝技術。就是這樣確定的。對于層壓板,我們只能做到這么小,而對于硅,我們可以做得更小,這樣我們就可以將引腳放置得更近。”

探索選項

模擬對于理解所有這些細節至關重要。Keysight 的 Slater 指出,對于高速數字,必須徹底模擬與 UCIe 的高速互連。射頻微波也是如此。

“在射頻微波領域,我們看到某些公司談論射頻小芯片的未來前景,”Slater說。“雖然這可能是以后的發展,但您在射頻微波市場中確實看到的一件事是,在一個模塊中,您有不同的芯片,不同的基板技術被組裝在一起使用。因此,異構集成在射頻模塊設計中已經出現多年。現在有新的方法能夠以更簡化的方式堆疊各個基板技術。曾幾何時,你必須按層次結構來做這件事。您必須將一項技術集成到另一項技術中,然后集成第三種技術。現在,我們可以將所有單獨的技術組合成一項,從而使設計層次結構扁平化,并使設計變得更加容易。既然您正在談論所有這些不同的接口和所有這些不同的層,從一種技術連接到另一種技術,您需要能夠跟蹤信號并分析信號路徑在所有這些邊界上的行為方式”。

勞動力問題

隨著整合而來的是勞動力問題。如今,芯片、封裝、驗證和測試工程師通常處于責任和專業知識的孤島中。這需要改變。

“連續的‘跨界’方法不適合跨學科的協同設計和協同優化,”西門子的Felton說。“參與 HI 設計的設計師和設計團隊需要能夠更早地了解集成和架構選擇的影響,并在設計進入詳細實施之前做出決策和權衡。這通常稱為“左移”,需要將設計方法更改為imec 定義的系統技術協同優化 (STCO)。當然,勞動力教育/賦能是未來勞動力的關鍵,美國政府正在通過 NGMM、Cornerstone 等項目解決這一問題。”

芯片公司成功的基礎之一是設計團隊的長壽和凝聚力。這對于先進封裝尤其重要。

“如果我去航空航天和國防客戶那里,他們就去過那里,這就是他們所知道的,這就是他們做事的方式,”Park說。“你去一家大型商業公司,都是一樣的。他們一直都在那里。他們就是這樣做事的。我很少看到有人離開航空航天和國防領域并決定加入這家制造手機芯片的公司。人們通常會留在自己關注的領域。設計這些東西的專業知識不只是一個人的。

但現在,隨著系統和 IC 的融合,這意味著需要更多的人員。您請信號完整性專家來看看,“如果您將這個小芯片從中介層移到層壓板上,是否仍能提供我想要的帶寬?” 或者,你讓熱學人員進來問,“如果我將這兩件事疊加在一起,從熱學角度來看這可行嗎?” 現在這是一個巨大的團隊努力。您無法將芯片設計和封裝設計者分開。他們都與設計和驗證工程師一起負責封裝、布局、散熱、信號完整性、電磁學、布局布線、簽核——所有這些不同的人都需要聚集在一起。”

代工廠在 3DHI 中的作用

3DHI 的基礎是半導體代工廠作為整個項目的推動者。

“沒有代工廠,你就無法進行異構分離,”Park 說。“它們是所有正在發生的事情的推動者,從 3D 堆疊到異構集成,再到超高密度 RDL。這是因為代工廠已經認識到整個世界正在走向多芯片、多芯片——這就是未來。因此,他們現在需要做后端并集成所有這些晶圓,而不僅僅是設計這些晶圓。這意味著他們現在正在與 OSAT 競爭,但 OSAT 和代工廠之間的競爭總是好的。”

例如,臺積電的 3DBlox 和三星的 CODE 是巨大的推動者,特別是對于剛接觸封裝設計的人來說。

“這是這組文件。將這些讀入您的工具中,它就會為您的設計建立整個 3D 平面圖,”Park 說。“順便說一句,我們保證它建立的 3D 平面圖可以按照這種方式制造。這是代工廠帶來的巨大推動力。鑄造廠帶來了正式的設計結構,而不是非常非正式的包裝世界。為了提高產量、降低價格,鑄造廠將這種正式感帶入了包裝中。其中一些開始滲透到包裝中,因此我們可以開始制定更正式的 OSAT 設計流程,這對行業來說都是好事。”

西門子的 Felton 指出,代工廠、OSAT 和基板供應商可以在減少 HI 采用障礙方面發揮重要作用。“第一步是幫助客戶確保 DRC/PDK 的簽署和流程合規性。下一個領域是提供設計工具支持,例如設計模板、技術塊、使用標準的裝配規范。除此之外,一些 OSAT 和基板供應商正在為其客戶提供增值服務,例如脫氣和阻抗匹配,這減輕了客戶可能面臨的所需工作量和技能。”

Chiplet 問題

3DHI 仍然被許多人認為是狂野的西部,而 Chiplet 是這個尚未被馴服的世界中不斷增長的一部分。

Expedera營銷副總裁 Paul Karazuba 表示:“當我們談論來自多個供應商的小芯片時——AMD 或英特爾的小芯片,情況就不同了。” “這只是制造設計的選擇。這幾乎不是您在不同小芯片供應商那里面臨的供應鏈問題。”

雖然商業小芯片正在取得進展,但互連標準仍然不存在。

“UCIe 一年前引起了很大的轟動,”卡拉祖巴說。“今天我不一定會看到同樣多的噪音。這可能只是人們正在開發它的一個因素。UCIe 提供了很多承諾,并且確實提供了很多承諾。我們需要完成這件事。”

但小芯片仍然存在一些業務問題。

“誰為設備提供保修?這一切將如何處理?是否會有通用的信賴標準?我們如何測試這些小芯片是否會有通用標準?實際上,這可能會通過多芯片模塊外部的名稱來設置,因為我們需要為組裝的小芯片提供一個更好的名稱,”Karazuba 說。“盒子外面的名字很可能就是決定這一切的人,但這些如何相互作用仍然是一個懸而未決的問題。

對于像“實際上如何物理連接所有這些”這樣簡單的問題,當今封裝單片硅上的互連在不同位置、不同節點等方面仍然有很大不同。因此,仍有大量工作需要完成必須要做。但半導體行業 70 年來一直擅長的一件事就是解決極其復雜的問題,并讓事情看起來如此簡單,而實際上并非如此。”

審核編輯:劉清

-

soc

+關注

關注

38文章

4204瀏覽量

219113 -

芯片設計

+關注

關注

15文章

1028瀏覽量

55010 -

3D芯片

+關注

關注

0文章

52瀏覽量

18467 -

ASIC芯片

+關注

關注

2文章

92瀏覽量

23856 -

chiplet

+關注

關注

6文章

434瀏覽量

12632

原文標題:3D芯片,怎么辦?

文章出處:【微信號:晶揚電子,微信公眾號:晶揚電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SciChart 3D for WPF圖表庫

騰訊混元3D AI創作引擎正式發布

騰訊混元3D AI創作引擎正式上線

DMD芯片在3D打印中的創新應用

3D集成電路的結構和優勢

3D封裝熱設計:挑戰與機遇并存

裸眼3D筆記本電腦——先進的光場裸眼3D技術

3D芯片,怎么辦?

3D芯片,怎么辦?

評論