避免RP和RP之間的直接路徑

假定設(shè)計(jì)中存在兩個(gè)RP,分別為RP1和RP2,那么就要避免出現(xiàn)RP1輸出直接連接到RP2或者相反從RP2輸出直接連接到RP1的路徑。因?yàn)檫@時(shí)RP邊界信號(hào)(連接RP1和RP2的net)的負(fù)載都在動(dòng)態(tài)區(qū),從而必然形成Partition Pin,由于邊界信號(hào)沒有經(jīng)過靜態(tài)區(qū)邏輯單元,這些PartitionPin最終會(huì)有相應(yīng)的PPLOC,這其實(shí)就增加了后續(xù)的布線壓力。這種情況下,最好將其優(yōu)化為RP1->FF -> RP2。其中FF在靜態(tài)區(qū)。

避免多個(gè)RP輸出連接到同一個(gè)靜態(tài)區(qū)的負(fù)載邏輯單元上

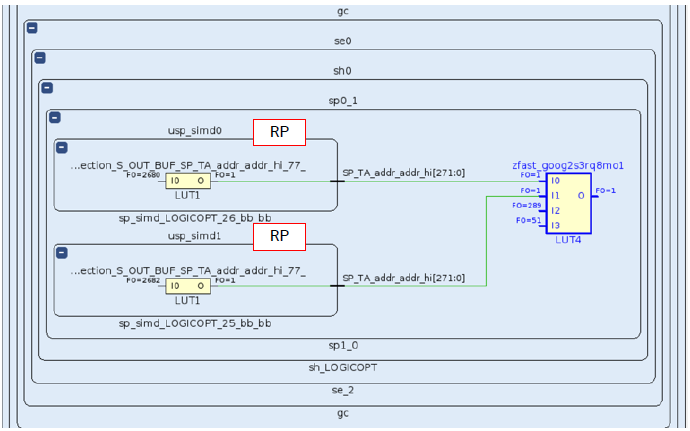

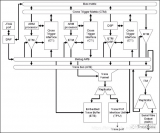

只有當(dāng)與邊界信號(hào)連接的靜態(tài)區(qū)負(fù)載落在擴(kuò)展的布線區(qū)域時(shí)才會(huì)觸發(fā)PPLOC縮減。如果一個(gè)靜態(tài)區(qū)的負(fù)載連接多個(gè)RP,那么顯然這個(gè)靜態(tài)區(qū)負(fù)載只可能落在其中一個(gè)RP的擴(kuò)展布線區(qū)域,那么另一個(gè)RP就會(huì)形成PPLOC,如下圖所示,兩個(gè)RP的輸出分別連接到靜態(tài)區(qū)負(fù)載LUT4的I0和I1端口,這樣就會(huì)形成PPLOC。

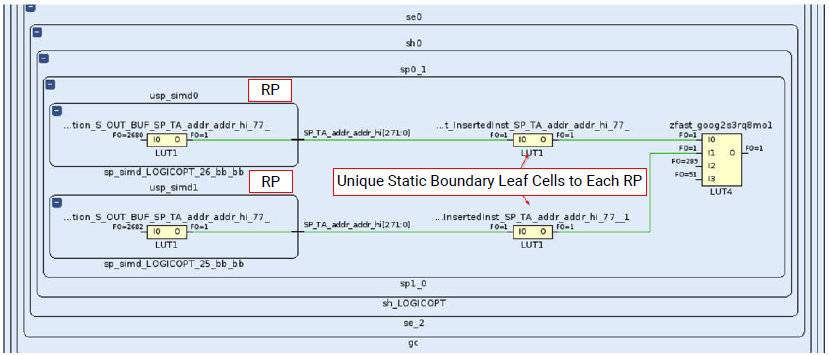

可將其優(yōu)化為如下圖所示方式,這樣每個(gè)RP的輸出都有獨(dú)立的靜態(tài)區(qū)負(fù)載,從而可能觸發(fā)PPLOC縮減。

復(fù)制靜態(tài)區(qū)寄存器驅(qū)動(dòng)多個(gè)RP

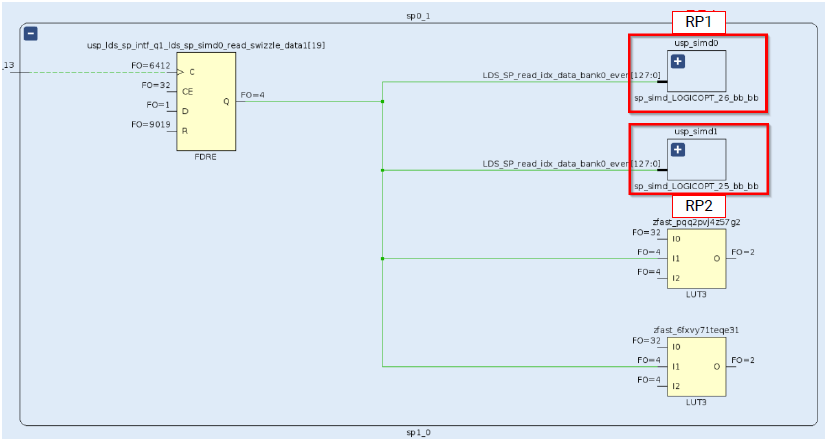

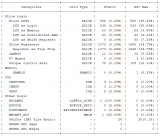

為了保證靜態(tài)區(qū)邊界負(fù)載對每個(gè)RP而言是獨(dú)立的,那么就要避免同一個(gè)靜態(tài)區(qū)觸發(fā)器驅(qū)動(dòng)多個(gè)RP。這種情況命令report_methodology會(huì)給報(bào)告出來。如下圖所示,靜態(tài)區(qū)觸發(fā)器扇出為4,同時(shí)驅(qū)動(dòng)了RP1和RP2。

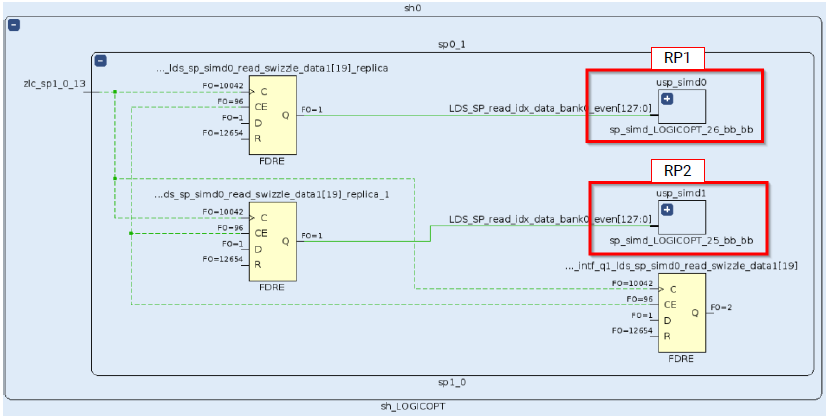

可對該觸發(fā)器進(jìn)行復(fù)制,如下圖所示,這樣就保證了每個(gè)RP有自己獨(dú)立的靜態(tài)區(qū)邊界負(fù)載。

對RM的輸入/輸出進(jìn)行寄存

AMD建議確保所有RM的輸入是寄存器輸入,而輸出也都是寄存器輸出。這樣,時(shí)序路徑就被隔離開來,即靜態(tài)區(qū)到RP邊界、RP內(nèi)部、RP邊界到靜態(tài)區(qū)。對布局布線是有利的,自然對時(shí)序收斂也是有益的。同時(shí),如果使用AbstractShell流程,這樣還可以有效減少Abstract Shell的大小,從而可進(jìn)一步縮短編譯時(shí)間。

避免靜態(tài)區(qū)的走線跑到動(dòng)態(tài)區(qū)

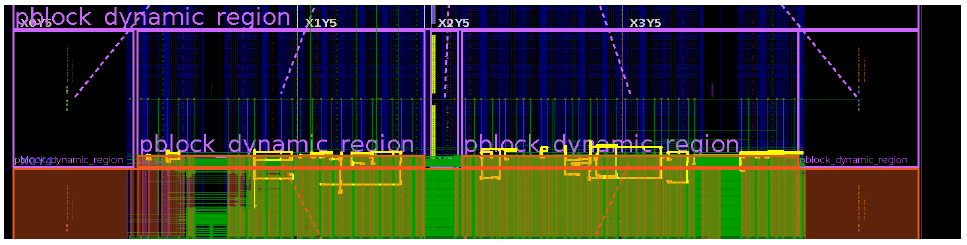

默認(rèn)情況下,DFX設(shè)計(jì)中靜態(tài)區(qū)的net是可以使用整個(gè)芯片的布線資源,自然也包括動(dòng)態(tài)區(qū)的布線資源,正因此,就可能出現(xiàn)靜態(tài)區(qū)布線跑到了動(dòng)態(tài)區(qū)。盡管從功能角度而言是允許的,但這會(huì)給動(dòng)態(tài)區(qū)布線帶來壓力。因此,如果出現(xiàn)動(dòng)態(tài)區(qū)布線擁塞時(shí),可以檢查一下是否存在上述情況。對于上述情況,我們可以對靜態(tài)區(qū)設(shè)置相應(yīng)的Pblock,將其屬性CONTAIN_ROUTING設(shè)置為true。下圖顯示了靜態(tài)區(qū)布線跑到動(dòng)態(tài)區(qū)的情形,圖中黃色走線即為靜態(tài)區(qū)走線,有部分跑到了動(dòng)態(tài)區(qū)。設(shè)置CONTAIN_ROUTING為true之后,可以看到這種情況就被消除了。

盡可能使Pblock形狀為矩形

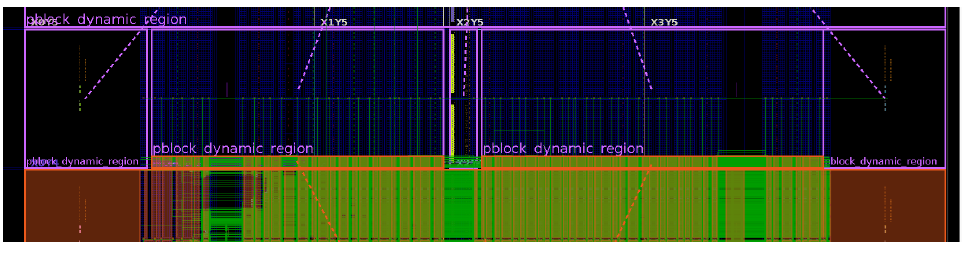

一旦將Pblock屬性CONTAIN_ROUTING設(shè)置為true時(shí),對于Pblock的拐角處工具布線難度就會(huì)顯著增大,如下圖左側(cè)所示。Pblock形狀不是標(biāo)準(zhǔn)的矩形,在拐角處形成布線擁塞,圖中白色高亮部分,擁塞等級(jí)為6。將其修正為標(biāo)準(zhǔn)矩形,如下圖右側(cè)部分所示,此時(shí)擁塞程度降低(圖中白色高亮部分),降至5。

審核編輯:湯梓紅

-

寄存器

+關(guān)注

關(guān)注

31文章

5402瀏覽量

122924 -

端口

+關(guān)注

關(guān)注

4文章

1011瀏覽量

32660 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2029瀏覽量

61780 -

DFx

+關(guān)注

關(guān)注

0文章

35瀏覽量

10764

原文標(biāo)題:優(yōu)化DFX設(shè)計(jì)

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

如何對傳統(tǒng)的非DFX設(shè)計(jì)進(jìn)行調(diào)試呢?

什么是DFX技術(shù)?DFX設(shè)計(jì)一定要執(zhí)行設(shè)計(jì)規(guī)則檢查嗎?

DFX設(shè)計(jì)如何分析

采用UltraScale/UltraScale+芯片的DFX設(shè)計(jì)注意事項(xiàng)

招兼職dfx、dfm培訓(xùn)講師

電源優(yōu)化方法是什么

優(yōu)化Unity程序的方法

優(yōu)化AutoCAD系統(tǒng)的方法

簡述DFX理念與產(chǎn)品研發(fā)(一)

簡要分析DFX實(shí)施流程

HarmonyOS對DFX能力的要求

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

優(yōu)化DFX設(shè)計(jì)的方法

優(yōu)化DFX設(shè)計(jì)的方法

評(píng)論