在功率半導(dǎo)體市場上,碳化硅(SiC)正逐步獲得重視,特別是在電動汽車領(lǐng)域,它越來越受歡迎,但由于成本過高,許多應(yīng)用場景仍然乏力涉足。

我們對碳化硅的優(yōu)點已經(jīng)十分熟悉,但直到最近,由于它仍是一種較為特定的技術(shù),沒有受到足夠的投資。隨著對能適應(yīng)高電壓應(yīng)用的芯片需求的逐漸增長,碳化硅得到了更多深入的關(guān)注。與其他可能的硅功率器件替代品相比,碳化硅享有熟悉性的優(yōu)勢。

碳化硅是最早被商業(yè)化的半導(dǎo)體之一,最早被應(yīng)用于晶體收音機(jī)的檢測二極管。自2008年以來,商業(yè)碳化硅結(jié)型場效應(yīng)晶體管(JFETs)已經(jīng)上市并在電子設(shè)備中得到廣泛應(yīng)用,特別是在極端環(huán)境下。2011年,碳化硅金屬氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFETs)也開始商業(yè)化。這種材料提供了中等的帶隙,其擊穿電壓是硅的10倍。

然而,碳化硅頗難制造。日立能源全球產(chǎn)品管理副總裁Tobias Keller解釋,標(biāo)準(zhǔn)的Czochralski (CZ)生長方法是不可行的。CZ生長法在1500°C左右將硅融化在硅耳坩堝內(nèi),但碳化硅的熔點超過2700°C。

一般來說,碳化硅晶體通過Lely方法生長。在氬氣環(huán)境中,將碳化硅粉末加熱到2500°C以上,在種晶上進(jìn)行升華。這種方法生產(chǎn)的結(jié)果是可行的,但是層疊錯位和其他缺陷導(dǎo)致它缺陷重重且難以控制。工程師在檢查來料的碳化硅的晶圓時,顯而易見,由于堆疊錯位和其他缺陷,找出很多“死區(qū)”。碳化硅器件是在定制的外延器件層上進(jìn)行優(yōu)化以適應(yīng)預(yù)期的工作電壓的。較厚的表皮層可以承受更高的電壓,但也會有更多的缺陷。

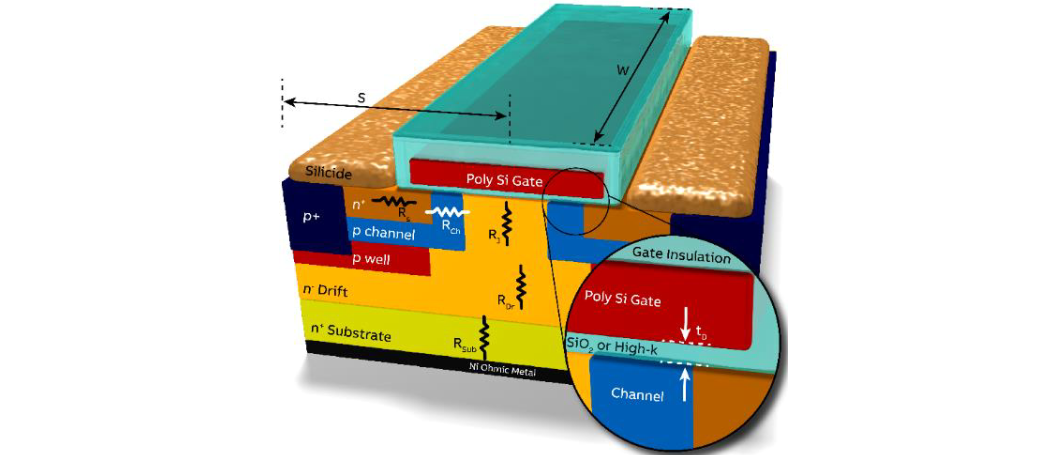

碳化硅MOSFETs還受到氧化物/碳化物表面通常質(zhì)量較差的限制。來自日本京都和大阪大學(xué)的研究員T. Kimoto及其同事在去年12月份的IEEE電子器件會議(IEDM)上提出,表面產(chǎn)生碳-碳缺陷是由于碳化硅的直接氧化造成的。這些缺陷位置靠近碳化硅的導(dǎo)帶邊緣,它們增加了導(dǎo)通通道電阻,導(dǎo)致設(shè)備中閾值電壓的漂移。

作為避免碳化硅氧化的方法,Kimoto的團(tuán)隊首先用氫等離子體蝕刻了表面,然后通過化學(xué)氣相沉積法(CVD)沉積二氧化硅,并對接面進(jìn)行氮化。這個過程降低了缺陷密度,并將電子遷移率提高了一倍以上,在10V的柵偏壓下達(dá)到80 cm2/V-sec。

日立能源(前ABB半導(dǎo)體)的Stephan Wirths和他的同事演示了一個未命名的高介電常數(shù)化合物,它能與碳化硅形成低缺陷表面, 不需要SiO2必需的鈍化步驟。正如在硅器件中一樣,對碳化硅金屬氧化物半導(dǎo)體場效應(yīng)管使用高介電常數(shù)介質(zhì)也會增加在給定電容下的物理厚度,從而減少漏電流。

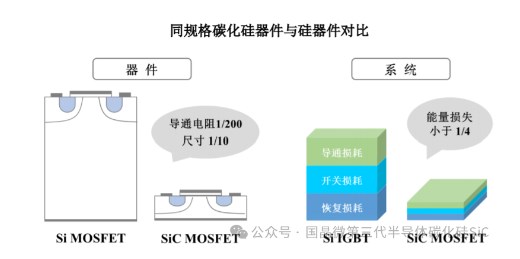

碳化硅的載流子遷移率較低,這給設(shè)備設(shè)計師帶來了一個新的挑戰(zhàn)。即使經(jīng)過幾十年的優(yōu)化,通過改進(jìn)介質(zhì)的載流子遷移率表現(xiàn)最好的碳化硅產(chǎn)品遷移率仍然比硅少10倍。因此,相關(guān)通道電阻較硅高出10倍。

對于功率器件,低遷移率限制了其性能和耐久性。器件的電阻和開關(guān)損失直接影響電動汽車的續(xù)航等參數(shù)。盡管植入型摻雜劑和器件結(jié)構(gòu)的改進(jìn)可以降低通道電阻,但如Sonrisa Research的總裁James Cooper所指出,這同時也導(dǎo)致了電流密度增加并降低短路耐受時間。

短路耐受時間是衡量功率器件安全性的重要參數(shù)。如果設(shè)備因故發(fā)生短路,那么它需要擁有足夠的壽命以保證保護(hù)電路反應(yīng)。失敗可能會對電負(fù)載產(chǎn)生永久性損壞,甚至可能導(dǎo)致用戶受傷、火災(zāi)和財產(chǎn)損失。對于具體要求,依賴于保護(hù)電路的設(shè)計,但通常時間在5到10微秒之間。隨著電流密度的增加,短路狀態(tài)下的溫度也會隨之升高,而耐久時間則會減少。

相比于同等評級的硅器件,碳化硅MOSFET的市場接受度較低,這部分原因是這些設(shè)備往往具有較短的耐受時間。因此,設(shè)計者們期望改變通道電阻和電流密度之間的關(guān)系。我們是否有辦法降低電阻,而不將電流密度提高到危險的水平呢?

可能的解決方案是降低電極偏壓并減小氧化物厚度。Cooper解釋道,薄氧化物提高了對通道的控制——要知道在硅MOSFET中就運(yùn)行在低電壓下。這種解決方案需要對制造過程進(jìn)行微調(diào)。雖然關(guān)于薄介質(zhì)碳化硅器件的研究較少,但硅器件使用的氧化物厚度薄達(dá)到5nm,且沒有引發(fā)過多的隧道效應(yīng)。如上所述,使用高介電常數(shù)適宜可以在保持物理厚度的同時提供更好的通道控制。

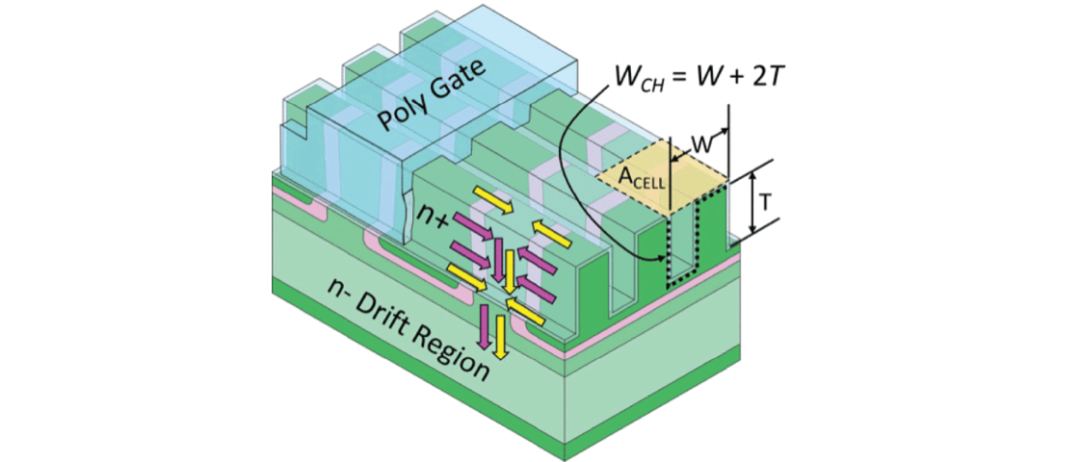

SUNY理工學(xué)院的Dongyoung Kim和Woongje Sung提出了另一種解決方案,他們嘗試通過增加有效通道寬度來降低電流密度。他們沿 SiC晶格方向使用離子引導(dǎo),以4°的傾斜角植入深P井。這種方法只需要微小的改動即可應(yīng)用于制造過程中,因為深井摻雜和常規(guī)井使用的掩蔽材料相同。最終所得的器件可以減小最大漏電流約2.7倍,同時將耐受時間提高了4倍。

針對類似的問題,硅工業(yè)則轉(zhuǎn)向了如今無所不在的FinFET。通過在特定電流下增加通道面積,可以降低電流密度。普渡大學(xué)的研究人員展示了一個具有多個亞微米fin的碳化硅三柵金屬氧化物半導(dǎo)體場效應(yīng)管,并實現(xiàn)了對特定通道電阻的3.6倍降低。

雖然目前還不清楚功率設(shè)備行業(yè)會以多快的速度采納像FinFET這樣的顛覆性架構(gòu),但碳化硅的高擊穿電壓無疑是一大吸引力。希望實現(xiàn)這一優(yōu)勢的制造商需要找到解決低遷移率和高電流密度問題的辦法。

-

電動汽車

+關(guān)注

關(guān)注

156文章

12427瀏覽量

234636 -

功率半導(dǎo)體

+關(guān)注

關(guān)注

23文章

1312瀏覽量

44161 -

碳化硅

+關(guān)注

關(guān)注

25文章

3066瀏覽量

50500

發(fā)布評論請先 登錄

碳化硅晶圓特性及切割要點

碳化硅功率器件有哪些特點

碳化硅薄膜沉積技術(shù)介紹

碳化硅的耐高溫性能

碳化硅在半導(dǎo)體中的作用

產(chǎn)SiC碳化硅MOSFET功率模塊在工商業(yè)儲能變流器PCS中的應(yīng)用

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

碳化硅在新能源領(lǐng)域的應(yīng)用 碳化硅在汽車工業(yè)中的應(yīng)用

碳化硅的應(yīng)用領(lǐng)域 碳化硅材料的特性與優(yōu)勢

碳化硅襯底,進(jìn)化到12英寸!

碳化硅功率器件的工作原理和應(yīng)用

碳化硅功率器件的優(yōu)點和應(yīng)用

碳化硅的挑戰(zhàn)與機(jī)遇

碳化硅的挑戰(zhàn)與機(jī)遇

評論