01

襯底

碳化硅襯底是第三代半導體材料中氮化鎵、碳化硅應用的基石。

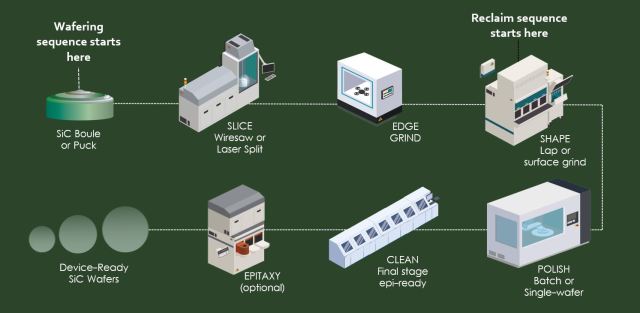

碳化硅襯底以碳化硅粉末為主要原材料,經過晶體生長、晶錠加工、切割、研磨、拋光、清洗等制造過程后形成的單片材料。

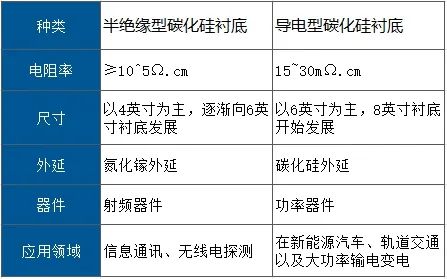

按照電學性能的不同,碳化硅襯底可分為兩類:一類是具有高電阻率(電阻率≥10^5Ω·cm)的半絕緣型碳化硅襯底,另一類是低電阻率(電阻率區間為15~30mΩ·cm)的導電型碳化硅襯底。

02

外延

在碳化硅襯底上,主要使用化學氣相沉積法(CVD法)在襯底表面生成所需的薄膜材料,即形成外延片,進一步制成器件。

其中,在導電型碳化硅襯底上生長碳化硅外延層制得碳化硅同質外延片,可進一步制成肖特基二極管、MosFET、IGBT等碳化硅功率器件,這些器件應用于新能源汽車的充電系統、光伏發電的逆變器、軌道交通的牽引系統、數據中心的電源管理、智能電網和航空航天等下游領域。

在半絕緣型碳化硅襯底上生長的GaN異質外延層制得碳化硅基氮化鎵(GaN-on-碳化硅)外延片,可制成HEMT等微波射頻器件。這些器件主要應用于5G通信的基站和終端設備、車載通信的智能互聯系統、國防應用的雷達和電子對抗設備、數據傳輸的高速通信網絡以及航空航天的飛行器電子系統等領域。

相比襯底,外延材料厚度、摻雜濃度均勻性好、片間一致性優、缺陷率低,有效提高了下游產品的一致性和良率。

目前的外延生產工藝,一般在碳化硅拋光片上生產外延層。依據不同器件的設計,所需的外延參數也不同。一般而言,外延的厚度越大,器件能夠承受的電壓也就越高。針對600V~6500V的應用,碳化硅外延層的厚度一般在1~40μm。目前國產6英寸碳化硅外延產已經實現商用化,8英寸量產產品正在推進中。

03

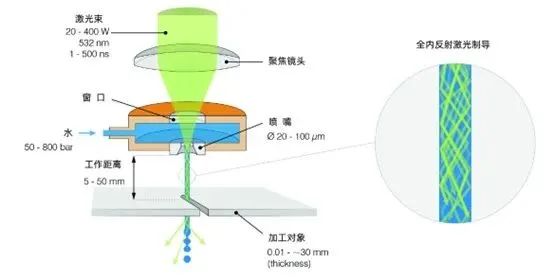

切割要點

碳化硅是強共價鍵化合物(約88%共價性),具有類似金剛石的密排四面體結構,其莫氏硬度高達 9.2-9.5(僅次于金剛石10),在所有半導體材料中最高。

摻雜會引起局部晶格應變或缺陷,重摻雜可能會導致位錯密度升高或微區應力集中,使材料在機械應力下更易產生裂紋。

同時,導電型碳化硅,在切割時劃片刀摩擦可能產生局部放電(微小電火花),加劇磨粒磨損或引起熱沖擊裂紋。而半絕緣碳化硅因為無放電效應,切割過程中不會有這方面的擔憂。

切割碳化硅晶圓的核心挑戰始終是其超高硬度和脆性,選擇切割工藝時,除了重點關注碳化硅晶圓的厚度、晶體質量和減薄后的表面狀態外,還可以關注不同導電類型襯底的細微差別。

詳細切割方案請咨詢西斯特硬刀應用團隊。

西斯特科技

深圳西斯特科技有限公司 (簡稱西斯特SST) ,以“讓一切磨削加工變得容易”為主旨,倡導磨削系統方法論,2015年金秋創立于深圳,根植于技術創新的精神,屹立于創造價值、追求夢想的企業文化。

基于對應用現場的深度解讀、創新性的磨具設計和磨削系統方法論的實際應用,西斯特秉承先進的磨削理念,踐行于半導體、汽車零部件等行業,提供高端磨具產品以及“切、磨、鉆、拋”系統解決方案,在晶圓與封裝基板劃切、微晶玻璃和功能陶瓷磨削、汽車零部件精密磨削等領域應用廣泛。

西斯特科技曾先后獲得國家高新技術企業、深圳市專精特新企業等稱號,始終以先進的技術、創新的產品、優質服務的理念,引領產業革命,創造無限可能。

-

半導體材料

+關注

關注

11文章

572瀏覽量

30093 -

碳化硅

+關注

關注

25文章

3064瀏覽量

50451

發布評論請先 登錄

碳化硅的歷史與應用介紹

碳化硅深層的特性

傳統的硅組件、碳化硅(Sic)和氮化鎵(GaN)

碳化硅晶圓生長,難在哪里?

改進碳化硅晶圓工藝

碳化硅晶圓特性及切割要點

碳化硅晶圓特性及切割要點

評論