時鐘是芯片驗證過程中最基本也是最重要的決定因素,一個精確的時鐘產(chǎn)生對時鐘敏感的電路來說至關(guān)重要。

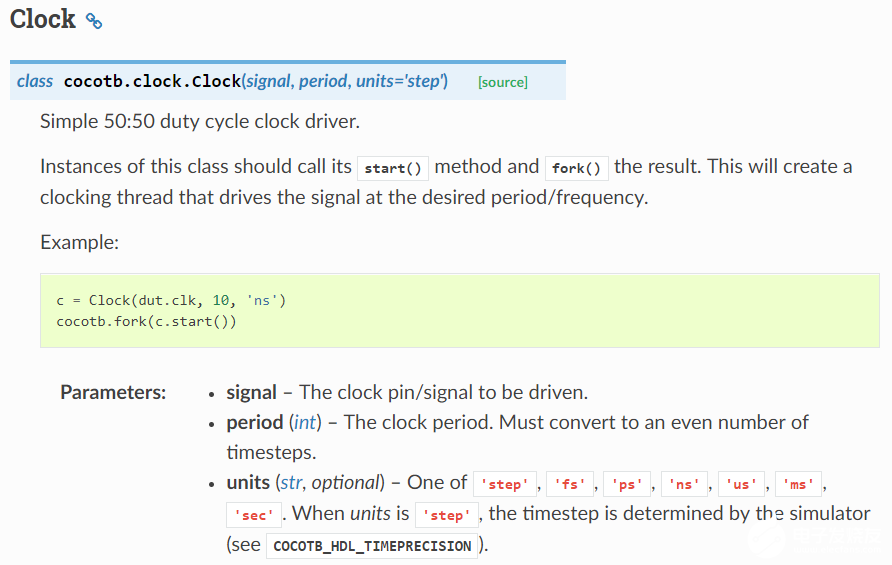

Cocotb平臺中內(nèi)建了時鐘產(chǎn)生的函數(shù)Clock()。Clock函數(shù)在官網(wǎng)上的描述如下:

Clock函數(shù)一共有三個形參,分別為:

signal:驅(qū)動的時鐘信號,如dut.clk

period:時鐘周期,必須為偶數(shù)個時間單位

units:時間單位,可以為“飛秒”、“皮秒”、“納秒”、“微秒”、“毫秒”、“秒”等時間單位;同時支持“時間步”,此時則協(xié)同“COCOTB_HDL_TIMEPRECISION”來決定具體的時間單位。

Clock的構(gòu)造實例如下:

方式一:c = Clock(dut.clk, 10, 'ns')

cocotb.fork(c.start())

方式二:cocotb.fork(Clock(dut.clk, 10, units='ns').start())

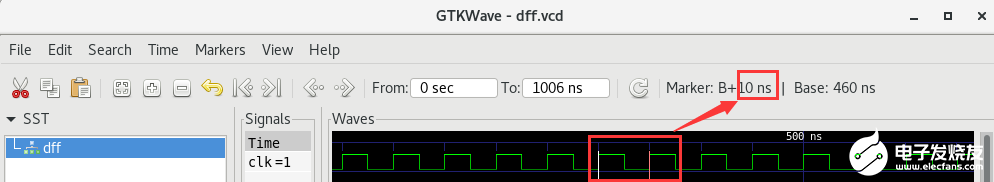

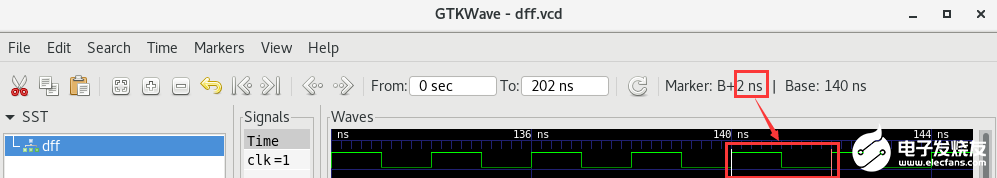

產(chǎn)生的效果如下:

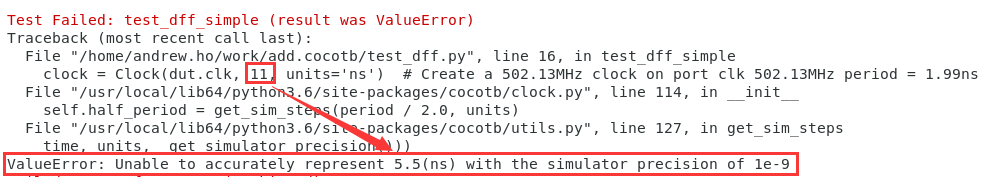

當(dāng)時鐘周期為奇數(shù)時則會報相關(guān)系統(tǒng)錯誤

當(dāng)希望產(chǎn)生一個520.13MHz頻率的時鐘時,時鐘周期為1.922596274008421ns,為了產(chǎn)生精度較高的520.13MHz時鐘時,可以采用不同的時間單位來構(gòu)造該時鐘。

1、采用時間單位為“ns”,時鐘周期四舍五入取值為2ns

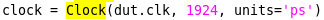

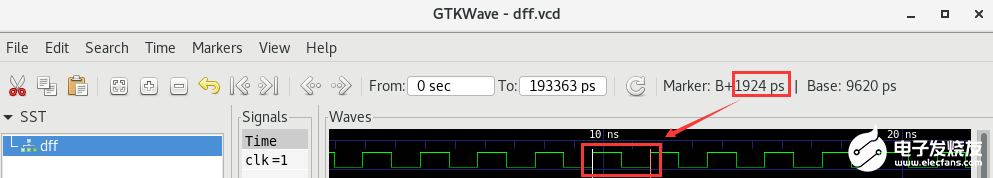

2、采用時間單位為“ps”,時鐘周期四舍五入取值為1923ps,周期要求偶數(shù)則取值為1924ps

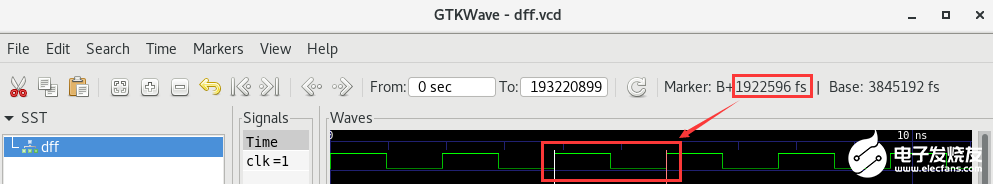

3、采用時間單位為“fs”,時鐘周期四舍五入取值為1922596fs

Clock函數(shù)采用不同的時間單位時需要確保與代碼的timescale匹配,也就是說Clock函數(shù)的時間單位應(yīng)大于等于timescale的時間單位。

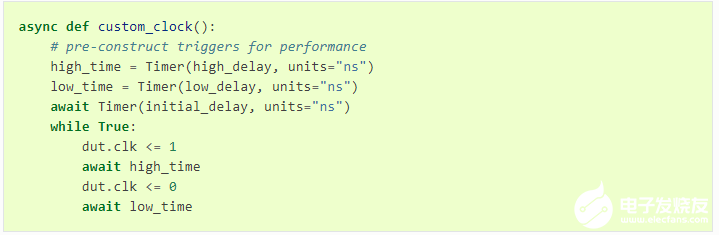

以上產(chǎn)生的時鐘均為占空比1:1的時鐘,當(dāng)用戶需要產(chǎn)生占空比非1:1的時鐘時,可以參考如下代碼的實現(xiàn):

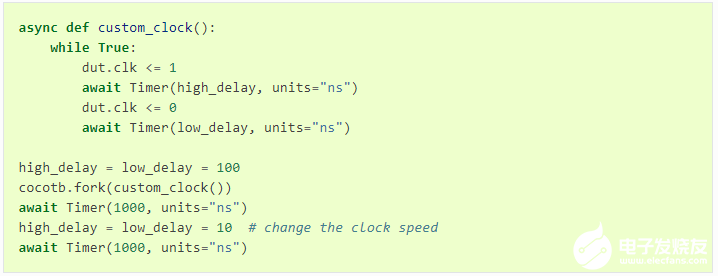

當(dāng)用戶需要做時鐘的動態(tài)調(diào)整時,可以參考如下的代碼實現(xiàn):

審核編輯:黃飛

-

芯片

+關(guān)注

關(guān)注

459文章

52205瀏覽量

436457 -

時鐘

+關(guān)注

關(guān)注

11文章

1884瀏覽量

132856 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4371瀏覽量

64230 -

時鐘信號

+關(guān)注

關(guān)注

4文章

465瀏覽量

29083

發(fā)布評論請先 登錄

SoC驗證平臺的FPGA綜合怎么實現(xiàn)?

驗證方法簡介

Python硬件驗證——摘要

基于FPGA的NoC驗證平臺的構(gòu)建

基于PCI接口的IP驗證平臺

基于System Verilog的可重用驗證平臺設(shè)計及驗證結(jié)果分析

基于python的用于構(gòu)建仿真及測試用例的lib庫cocotb

cocotb中的基礎(chǔ)語法

cocotb的安裝、python tb文件的寫法

基于Simulink代碼生成的FPGA信號處理系統(tǒng)仿真驗證平臺

移動SoC的時鐘驗證

Cocotb驗證平臺時鐘的產(chǎn)生代碼

Cocotb驗證平臺時鐘的產(chǎn)生代碼

評論