Chiplet,又稱芯片堆疊,是一種模塊化的半導(dǎo)體設(shè)計和制造方法。由于集成電路(IC)設(shè)計的復(fù)雜性不斷增加、摩爾定律的挑戰(zhàn)以及多樣化的應(yīng)用需求,Chiplet技術(shù)應(yīng)運(yùn)而生。該技術(shù)通過將功能專一的小芯片組合成整體,提高了設(shè)計靈活性、降低了制造成本,并促進(jìn)了半導(dǎo)體產(chǎn)業(yè)的創(chuàng)新。

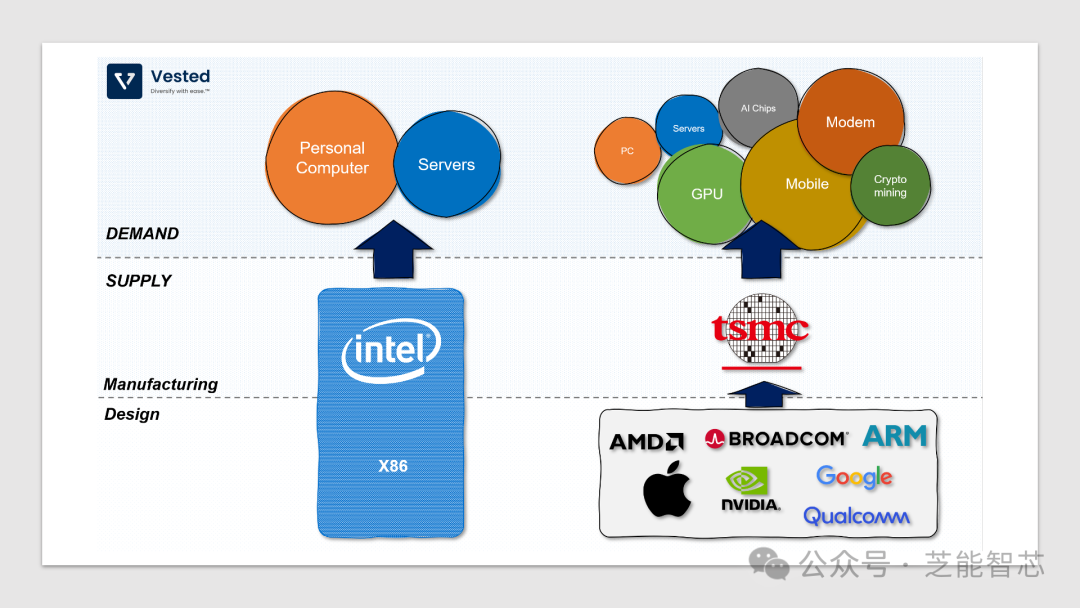

Chiplet技術(shù)的興起標(biāo)志著半導(dǎo)體行業(yè)面臨的一場顛覆性革命,對于英特爾和臺積電而言,這一技術(shù)趨勢產(chǎn)生了深遠(yuǎn)的影響。

不同的應(yīng)用需要專門的組件和功能,而小芯片則提供了一種不同的方式,不再試圖滿足所有需求,而是允許創(chuàng)建可以以混合搭配方式組合的專用組件。在考慮成本和上市時間的因素時,開發(fā)新的半導(dǎo)體工藝技術(shù)變得昂貴且耗時。Chiplet技術(shù)應(yīng)運(yùn)而生,提供了一種方法,可以利用某些組件現(xiàn)有的成熟流程,同時專注于特定功能的創(chuàng)新。

此外,小芯片還有助于新工藝技術(shù)的發(fā)展,因?yàn)樾酒叽绾蛷?fù)雜性只是單片芯片的一小部分,從而簡化了制造和產(chǎn)量的流程。

隨著組件之間距離的增加,傳統(tǒng)的單片設(shè)計面臨著互連性方面的挑戰(zhàn)。

小芯片通過提高模塊化性并簡化互連性,有效地解決了這一問題。此外,小芯片還支持異構(gòu)集成,即將不同的技術(shù)、材料和功能集成在一個封裝上,從而有助于實(shí)現(xiàn)更好的整體性能。小芯片的開發(fā)通常涉及到半導(dǎo)體行業(yè)中不同公司和行業(yè)參與者之間的合作。標(biāo)準(zhǔn)化工作,例如通用Chiplet互連快速聯(lián)盟(UCIe)等組織領(lǐng)導(dǎo)的用于Chiplet集成的標(biāo)準(zhǔn)化工作,成為推動這一領(lǐng)域進(jìn)展的關(guān)鍵。

總的來說,小芯片的出現(xiàn)是為了解決半導(dǎo)體行業(yè)日益增加的復(fù)雜性、成本、上市時間和人員壓力所帶來的挑戰(zhàn)。基于小芯片的設(shè)計的模塊化和靈活特性允許更高效和可定制的芯片集成,有助于推動半導(dǎo)體技術(shù)的不斷進(jìn)步,而且更不用說其多源芯片的能力了。

Part 1

對英特爾的影響

英特爾充分利用Chiplet技術(shù),成為其IDM 2.0戰(zhàn)略的關(guān)鍵組成部分。

具體表現(xiàn)在以下兩個方面:

●工藝節(jié)點(diǎn)交付加速: 英特爾承諾在四年內(nèi)交付五個工藝節(jié)點(diǎn),這標(biāo)志著IDM 2.0戰(zhàn)略的重要里程碑。通過使用Chiplet,英特爾能夠更加靈活地應(yīng)對工藝升級,避免了為復(fù)雜的CPU或GPU執(zhí)行完整工藝所需的困難。

●外包制造合作: 英特爾與臺積電簽署了歷史性的Chiplet外包協(xié)議,使其能夠充分利用多源代工業(yè)務(wù)模式。這為英特爾在業(yè)務(wù)需要時,將制造外包給臺積電提供了靈活性,打破了傳統(tǒng)的單一芯片制造來源的束縛。

英特爾通過Chiplet技術(shù)在FPGA產(chǎn)品領(lǐng)域取得領(lǐng)導(dǎo)地位,已經(jīng)成功出貨超過1000萬個Chiplet。

英特爾在Chiplet的應(yīng)用上擁有悠久的歷史,尤其在利用嵌入式多芯片互連橋(EMIB)封裝技術(shù)方面表現(xiàn)出色。自2016年首款英特爾 Stratix 10 FPGA推出以來,英特爾一直在其產(chǎn)品中使用Chiplet和EMIB技術(shù),如最先進(jìn)的英特爾 Agilex FPGA系列。

Chiplet為英特爾的可編程邏輯器件帶來三大優(yōu)勢:加快下一代技術(shù)的上市時間、靈活地混合和匹配最佳IP、代工和工藝技術(shù),以滿足不同產(chǎn)品功能的需求,以及構(gòu)建比單片技術(shù)更高容量的半導(dǎo)體。

通過EMIB封裝技術(shù),英特爾成功推動了一系列產(chǎn)品的創(chuàng)新,包括英特爾 Stratix FPGA系列的多個變體,英特爾 Agilex FPGA系列以及模擬的英特爾 FPGA Direct-RF系列。這些產(chǎn)品展現(xiàn)了英特爾小芯片和EMIB技術(shù)的引領(lǐng)地位,實(shí)現(xiàn)了一系列行業(yè)“第一”,如支持PCIe 5.0、CXL接口功能等。

英特爾計劃繼續(xù)擴(kuò)大在Chiplet技術(shù)方面的領(lǐng)先地位,尤其通過通用Chiplet Interconnect Express(UCIe)標(biāo)準(zhǔn)的推廣。英特爾在Chiplet生態(tài)系統(tǒng)的發(fā)展中起到關(guān)鍵作用,該生態(tài)系統(tǒng)涵蓋了來自多個代工廠的功能廣泛的小芯片,為英特爾的FPGA、結(jié)構(gòu)化ASIC和全定制ASIC產(chǎn)品提供更多功能。通過UCIe聯(lián)盟的標(biāo)準(zhǔn),英特爾預(yù)計將實(shí)現(xiàn)更廣泛的開放式小芯片生態(tài)系統(tǒng),促進(jìn)整個行業(yè)的產(chǎn)品開發(fā)。

Part 2

對臺積電的影響

對于臺積電而言,Chiplet技術(shù)帶來了新的挑戰(zhàn)和機(jī)遇:

●避免壟斷: 通過采用Chiplet,臺積電避免了傳統(tǒng)的壟斷模式,使客戶理論上能夠從多個來源獲得其芯片。這增加了客戶的選擇自由度,促使了更加競爭激烈的市場環(huán)境。

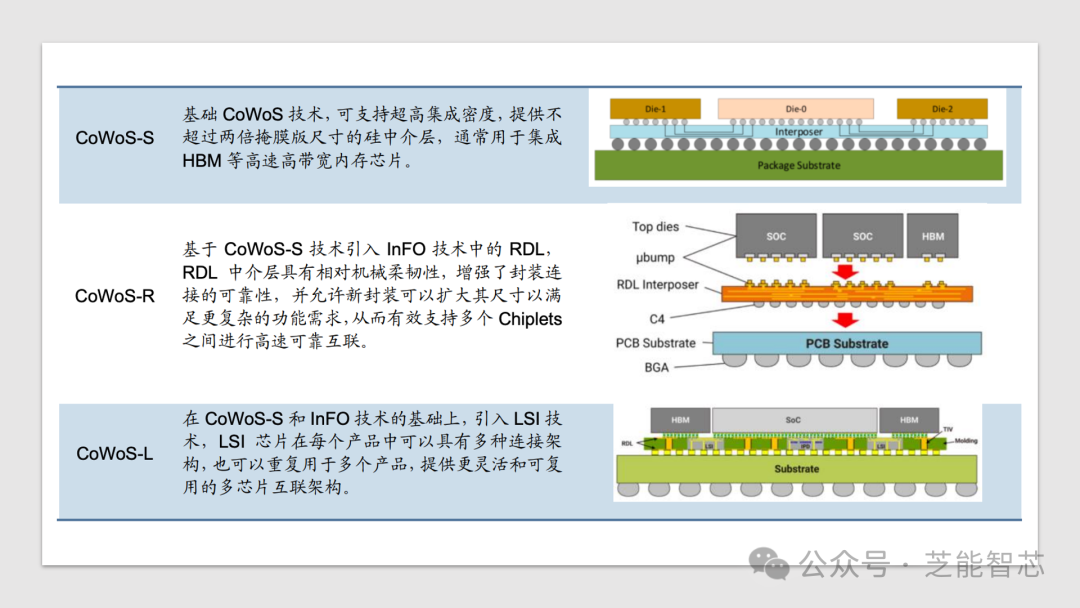

●生態(tài)系統(tǒng)支持: 臺積電通過其3D硅堆疊和先進(jìn)封裝技術(shù)快速響應(yīng)Chiplet技術(shù),并致力于構(gòu)建強(qiáng)大的Chiplet生態(tài)系統(tǒng)。這為臺積電提供了在新興技術(shù)領(lǐng)域中保持領(lǐng)先地位的機(jī)會。

CoWoS-S基礎(chǔ)技術(shù)支持超高集成密度,提供不超過兩倍掩膜版尺寸的硅中介層,主要用于集成HBM等高速高帶寬內(nèi)存芯片;CoWoS-R在CoWoS-S技術(shù)基礎(chǔ)上引入InFO技術(shù)中的RDL,通過具有相對機(jī)械柔韌性的RDL中介層增強(qiáng)封裝連接可靠性,同時允許封裝尺寸擴(kuò)大以滿足更復(fù)雜功能需求,有效支持多個Chiplets之間進(jìn)行高速可靠互聯(lián);CoWoS-L在CoWoS-S和InFO技術(shù)的基礎(chǔ)上引入LSI技術(shù),使LSI芯片在每個產(chǎn)品中具備多種連接架構(gòu),同時可復(fù)用于多個產(chǎn)品,提供更靈活和可復(fù)用的多芯片互聯(lián)架構(gòu)。

結(jié)語

Chiplet技術(shù)的崛起標(biāo)志著半導(dǎo)體行業(yè)進(jìn)入了一場顛覆性的革命,為全球的代工工廠和IDM代工廠提供了分得芯片制造市場的機(jī)會。我們正處于自FinFET以來從未見過的制造顛覆的開端,將推動半導(dǎo)體技術(shù)的進(jìn)步,提高設(shè)計靈活性,同時也挑戰(zhàn)著傳統(tǒng)的制造模式,將成為未來半導(dǎo)體行業(yè)演變的關(guān)鍵驅(qū)動因素。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614574 -

集成電路

+關(guān)注

關(guān)注

5420文章

11971瀏覽量

367369 -

英特爾

+關(guān)注

關(guān)注

61文章

10177瀏覽量

174039 -

臺積電

+關(guān)注

關(guān)注

44文章

5741瀏覽量

169048 -

chiplet

+關(guān)注

關(guān)注

6文章

453瀏覽量

12888

原文標(biāo)題:Chiplet技術(shù)對英特爾和臺積電有何影響?

文章出處:【微信號:QCDZSJ,微信公眾號:汽車電子設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

博通與臺積電或有意瓜分英特爾

英特爾18A與臺積電N2工藝各有千秋

博通與臺積電或考慮接手英特爾業(yè)務(wù)

博通臺積電或聯(lián)手瓜分英特爾

美推動英特爾拆分制造部門與臺積電合資

英特爾或與臺積電合作,計劃轉(zhuǎn)讓晶圓廠運(yùn)營權(quán)

詳細(xì)解讀英特爾的先進(jìn)封裝技術(shù)

半導(dǎo)體三巨頭格局生變:英特爾與三星面臨挑戰(zhàn),臺積電獨(dú)領(lǐng)風(fēng)騷

Chiplet技術(shù)對英特爾和臺積電有哪些影響呢?

Chiplet技術(shù)對英特爾和臺積電有哪些影響呢?

評論