DDR5已經(jīng)開始商用,但是有的產(chǎn)品還在使用DDR4,本文將分享一些DDR4的測試內(nèi)容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以達到 3200Mb/s,這樣高速的信號,對信號完整性的要求就更加嚴格,JESD79‐4 規(guī)范也對 DDR4 信號的測量提出了一些要求。

ChrentDDR4的特性

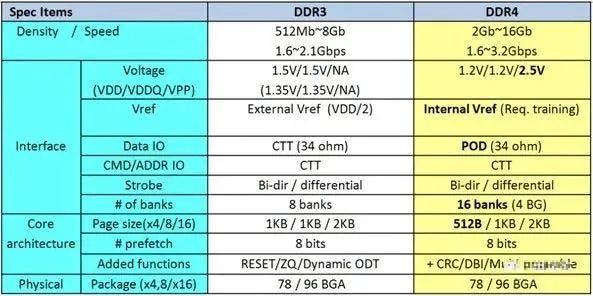

DDR4 相比 DDR3,有很多新的變化,首先它的帶寬提高了近一倍,最高達到 3200Mb/s,而且運行在更低的電壓下,VDD 電壓是 1.2V,這樣可以在帶寬提高的同時,不會提高系統(tǒng)的功耗。采用了新的顆粒架構,可以在單條內(nèi)存上做到 16 個內(nèi)存顆粒,內(nèi)存封裝和 DIMM 類型不變,但是內(nèi)存的 Pin 腳數(shù)量有所變化。

DDR4 的 Pin 腳數(shù)達到 288Pin,Pin 腳間距更加小,更詳細的對比,見下圖:

Fig.1 DDR4 和 DDR3 對比圖

ChrentDDR4信號完整性測試要求

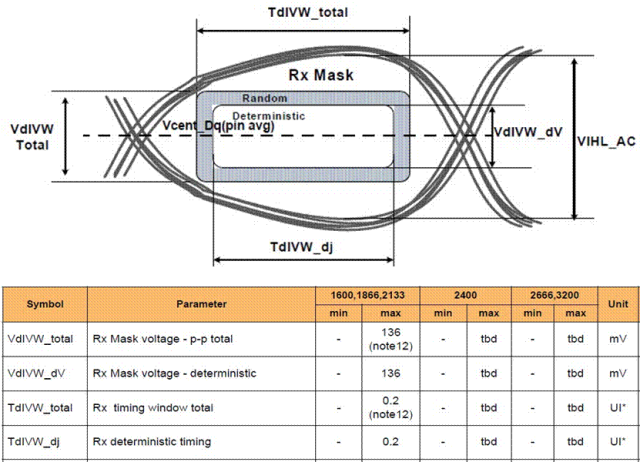

在 DDR4 規(guī)范 JESD79‐4 中,對物理層信號測試要求有:DQ 眼圖模板測試、抖動分析、電氣特性測試,時序測試。相比 DDR3,DDR4 對眼圖測試和抖動測試提出了新的要求。

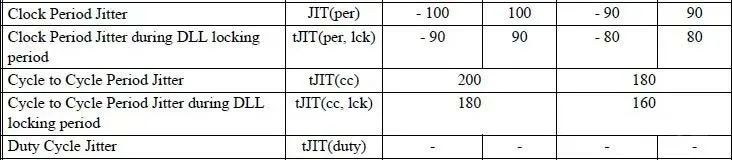

在 DDR3 的測試中,對 Clock 的抖動的測試要求是:Period Jitter、Cycle‐Cycle Jitter、 Duty Cycle Jitter。DDR3 的 Spec 中做了這樣的推算:如果你的內(nèi)存滿足了規(guī)范要求的所有電氣特性和時序特性,就可以一直正常的運行。現(xiàn)實狀況下,這是沒有考慮其他因素的理想情況,像隨機抖動等也會影響產(chǎn)品的工作,而 DDR3 都沒有對這些進行測試。

Fig.2 DDR3 Clock 抖動測試

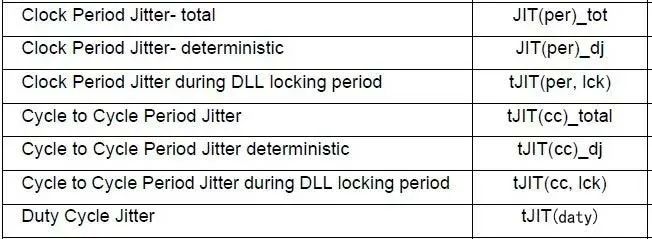

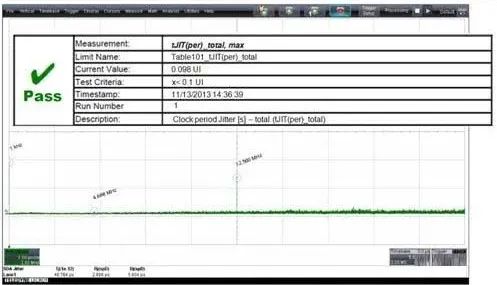

在 DDR4 的規(guī)范中,采用了更實際的方法來考慮這些因素,測試要求包含了隨機抖動 Rj 和確定性抖動 Dj,在規(guī)范中,總體抖動 Tj 被定義為在一定誤碼率下的確定性抖動 Dj 和隨機性抖動 Rj 的和,對抖動做了分解。Fig.5 是測試結果。

Fig.4 DDR4 Clock Jitter 要求

Fig.5 Lecroy Qualiphy‐DDR4 Jitter 測試結果

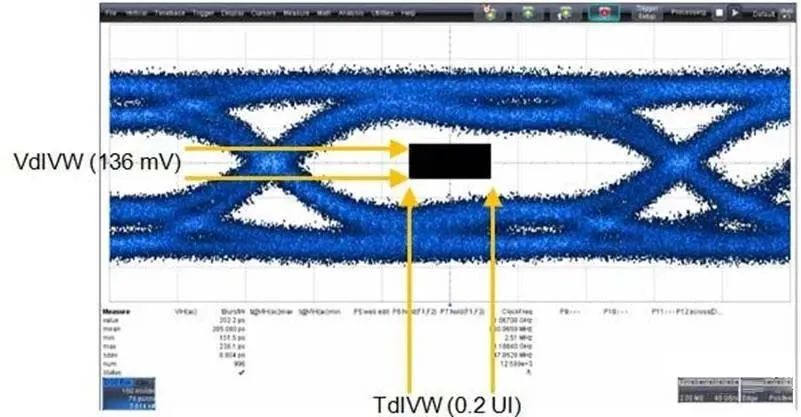

Chrent眼圖模板測試

在 DDR3 測試中,眼圖只是作為一個 Debug 的手段,不是強制要求測試,而且沒有模板。但是在 DDR4 中,要求進行 DQ 輸入接收端眼圖模板測試,F(xiàn)ig.6 是眼圖模板的定義,在 DDR4‐2133 及以下頻率,TdIVW_total 和 TdIVW_dj 相等 VdIVW_total 和 VdIVW_dV 相等,從本質(zhì)上,現(xiàn)在還沒有在模板中定義隨機成分。

Fig.6 DDR4 眼圖模板定義

Fig.7 DDR4 DQ 眼圖

ChrentDDR4 測試探測挑戰(zhàn)

DDR4 的速率提升一倍,同時信號電壓降低也接近一倍,這對測試探測技術提出了更高的要求。DDR4 規(guī)范中的所有測試都是定義在 BGA 或者 DIMM 的管腳處, 但是在很多時候,我們很難直接探測到 BGA 管腳處,這樣測出來的結果誤差會非常大,解決方案是使用 Interposer 夾具或者虛擬探測技術,探測到理想點的波形。

-

測試

+關注

關注

8文章

5641瀏覽量

128382 -

DDR

+關注

關注

11文章

731瀏覽量

66441 -

DDR4

+關注

關注

12文章

329瀏覽量

41564

發(fā)布評論請先 登錄

SiC SBD的靜態(tài)特性和動態(tài)特性

SiC MOSFET的參數(shù)特性

特性阻抗是什么意思,特性阻抗計算公式

N32G4FR系列芯片關鍵特性,定貨型號及資源,封裝尺寸等信息

BNC 4芯接頭應用指南:關鍵特性與行業(yè)應用

傳感器的動態(tài)特性和靜態(tài)特性參數(shù)介紹

什么是IPV4?什么是IPV6?

放大電路的頻率特性包括

DDR4的基本概念和特性

摻雜對PN結伏安特性的影響

控制閥的理想流量特性有哪些

4芯M16接口及其特性

ChrentDDR4的特性

ChrentDDR4的特性

評論