1.$width語法

在verilog中,$width是時序檢查函數,用于檢查脈沖的位寬是否符合要求。

$width ( reference_event , timing_check_limit , threshold [ , [ notify_reg ] ] ) ;

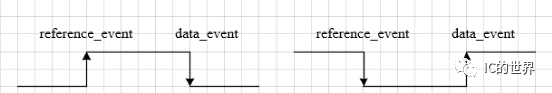

reference_event代表一個上升沿(下降沿)觸發事件。

語法中隱形地表達了data_event。

data event = reference event signal with opposite edge。

如果reference_event為上升沿,則最近的一個下降沿是data_event,兩者的時間間隔為脈沖寬度。

如果reference_event為下升沿,則最近的一個上降沿是data_event,兩者的時間間隔為脈沖寬度。

圖1:event示意圖[1]

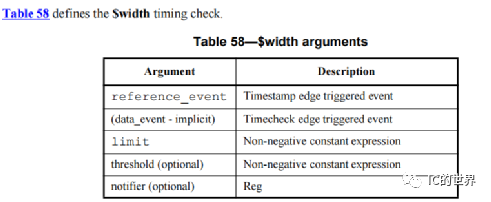

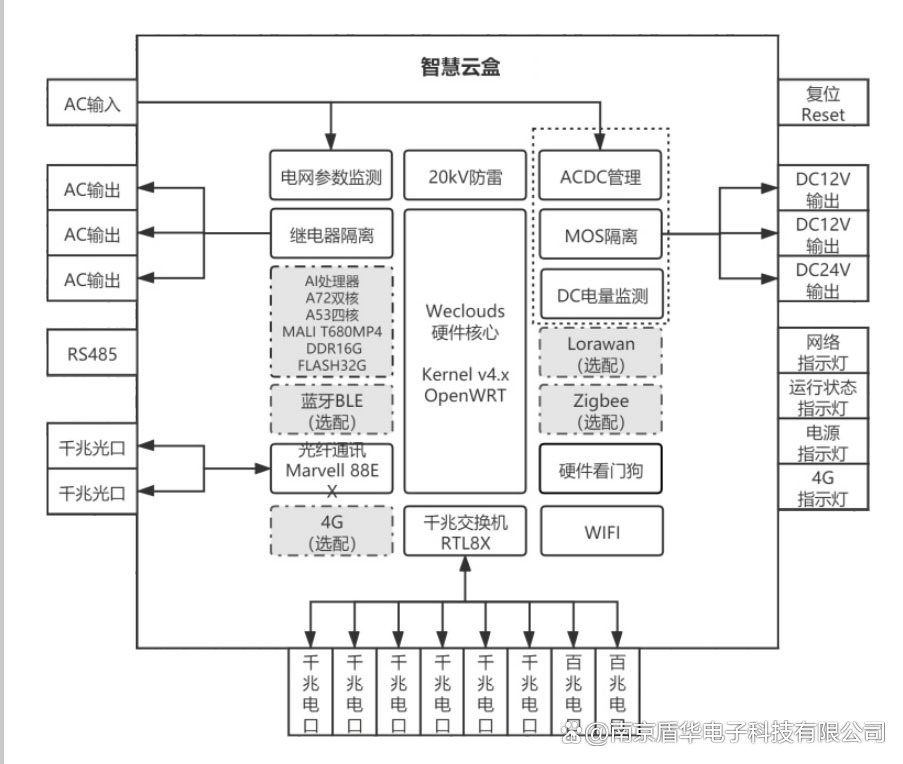

圖2:參數說明[2]

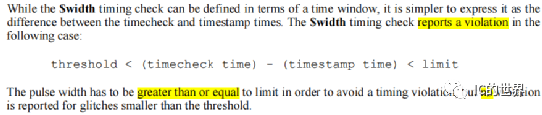

?期望的場景:脈沖寬度 >= limit

?不期望的場景:

?產生timing violation場景的:threshold < 脈沖寬度< limit

?不產生timing violation場景的:脈沖寬度

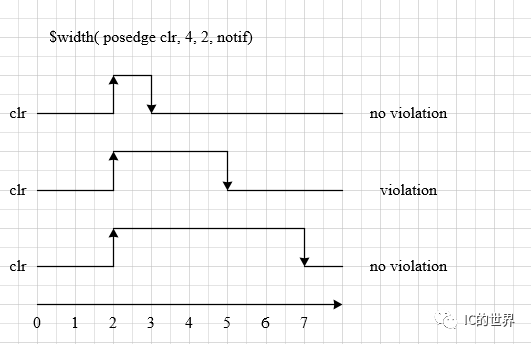

圖2:width檢測時序示意圖[1]

NOTE:很多時候threshold的值為0.

2.案例說明

此案例中,使用的仿真工具為VCS,limit為 6000ps。小于6000ps的脈沖位寬均產生了Timing violation。

threshold為2000ps,位寬小于threshold的脈沖也產生了Timing violation,此處檢查比協議要求得更加嚴格。

"/auto/asic/design/try/top/rtl/width_tb.v", 34: Timing violation in width_tb $width( posedge clk:1000, : 2000, limit: 6000 ); "/auto/asic/design/try/top/rtl/width_tb.v", 34: Timing violation in width_tb $width( posedge clk:5000, : 10000, limit: 6000 ); $finish called from file "/auto/asic/design/try/top/rtl/width_tb.v", line 10. $finish at simulation time 100000 V C S S i m u l a t i o n R e p o r t

module width_tb;

reg clk;

initial begin

$fsdbDumpfile("width_tb.fsdb");

$fsdbDumpvars(0, width_tb);

#100;

$finish;

end

initial begin

clk = 1'b0;

#1;

clk = 1'b1;

#1;

clk = 1'b0;

#3;

clk = 1'b1;

#5;

clk = 1'b0;

#5;

clk = 1'b1;

#10;

clk = 1'b0;

#5;

clk = 1'b1;

#15;

clk = 1'b0;

end

specify

$width(posedge clk,6,2);

endspecify

endmodule

-

Verilog

+關注

關注

29文章

1366瀏覽量

111909 -

VCS

+關注

關注

0文章

80瀏覽量

9858 -

CLK

+關注

關注

0文章

127瀏覽量

17543 -

時序仿真

+關注

關注

0文章

14瀏覽量

7510

原文標題:網表時序仿真,淺說$width

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

什么是Modelsim的功能仿真和時序仿真?

請問用什么語法可以實現這個max=val?

視覺模塊OpenMV淺說LED燈

時序計算和Cadence仿真結果的運用

Modelsim的功能仿真和時序仿真

modelsim仿真詳細過程(功能仿真與時序仿真)

基于ModelSim使用modelsim手動時序仿真教程

時序分析概念min pulse width介紹

網表時序仿真案例:淺說$width語法

網表時序仿真案例:淺說$width語法

評論