首先哪些因此會導致時鐘skew過大呢?

不合理的時鐘結構

時鐘同時驅動I/O資源和Slice資源

時鐘跨die

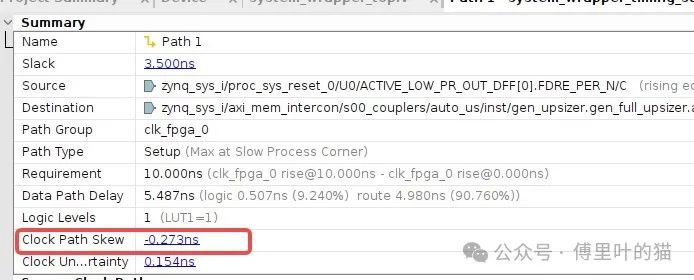

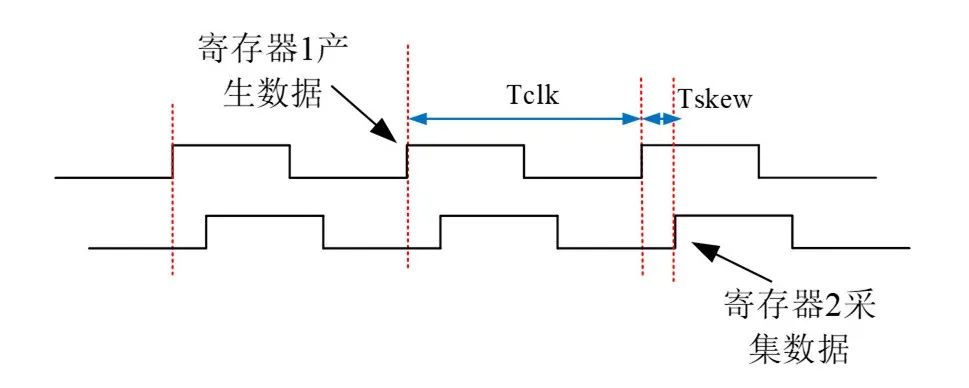

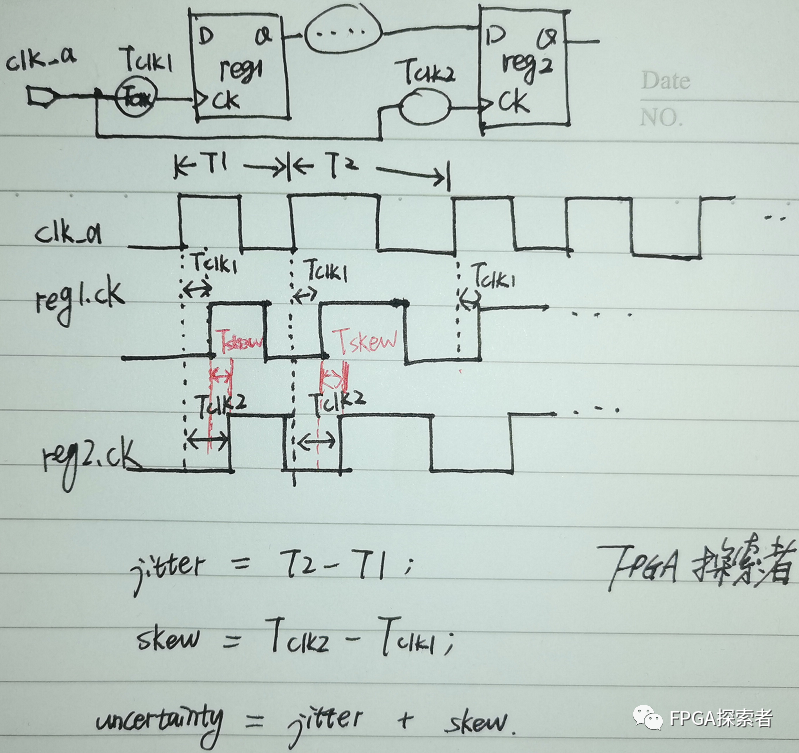

在時序報告中,會顯示出clock path skew,如果時鐘偏移超過0.5ns,就需要額外關注了。

書中列舉了幾個優化skew的方法:

移除時鐘路徑上多余的時鐘buffer,如果出現了級聯時鐘Buffer,勢必會導致時鐘路徑上的延遲增大。

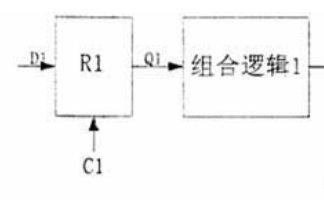

移除時鐘路徑上的組合邏輯,一旦時鐘路徑上出現了組合邏輯,就意味著時鐘布線采用了“常規布線資源+專用布線資源”的組合形式,從而顯著增大了時鐘延遲且時鐘skew無法預測。同時,相比于專用時鐘布線資源,常規布線資源對噪聲更加敏感,這會使時鐘質量下降。

輸入時鐘從clock capable的管腳輸入,否則還是會出現“常規布線資源+專用布線資源”的組合形式。

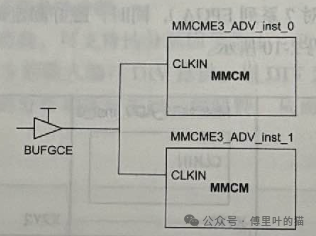

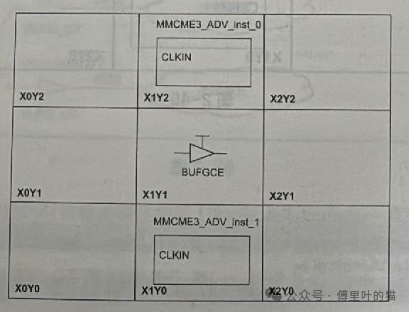

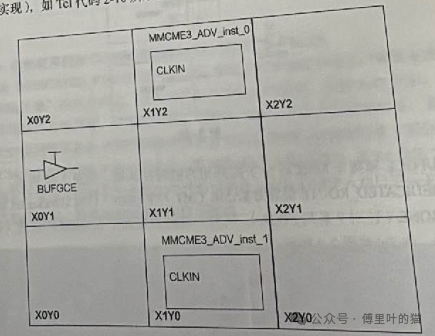

如果設計中出現并行的MMCM/PLL時,應合理設置CLOCK_DEDICATED_ROUTE的值。

如果BUFGCE和兩個MMCM位于同列相鄰的時鐘區域,那么應為約束為SAME_CMT_COLUMN或BACKBONE,同時將MMCM的位置固定下來:

#FORUltraScale/UltraScale+ set_propertyCLOCK_DEDICATED_ROUTESAME_CMT_COLUMN[get_nets-of[get_pinsBUFG_inst/O]] #FOR7series set_propertyCLOCK_DEDICATED_ROUTEBACKBONE[get_nets-of[get_pinsBUFG_inst/O]] set_propertyLOCMMCM3_ADV_X1Y2[get_cellsMMCM3_ADV_inst_0] set_propertyLOCMMCM3_ADV_X1Y0[get_cellsMMCM3_ADV_inst_1]

如果BUFGCE和兩個MMCM位于不同列但相鄰的時鐘區域,那么應該設為ANY_CMT_COLUMN和FALSE。

#FORUltraScale/UltraScale+ set_propertyCLOCK_DEDICATED_ROUTEANY_CMT_COLUMN[get_nets-of[get_pinsBUFG_inst/O]] #FOR7series set_propertyCLOCK_DEDICATED_ROUTEFALSE[get_nets-of[get_pinsBUFG_inst/O]] set_propertyLOCMMCM3_ADV_X1Y2[get_cellsMMCM3_ADV_inst_0] set_propertyLOCMMCM3_ADV_X1Y0[get_cellsMMCM3_ADV_inst_1]

對于7系列FPGA,避免使用BUFIO/BUFR/BUFH來驅動分散在不同時鐘域內的邏輯。要評估設計中區域時鐘緩沖器負載的個數,以保證這些負載可以被放置在一個時鐘區域內。

對于UltraScale/UltraScale+和Versal的FPGA,避免使用MMCM/PLL對來自BUFG_GT的輸出時鐘執行簡單的分頻,可以使用BUFGCE_DIV、MBUFG這些帶有分頻功能的時鐘BUFFER來代替。

對于UltraScale/UltraScale+和Versal的FPGA,對關鍵的同步跨時鐘域路徑添加CLOCK_DELAY_GROUP約束。什么是同步跨時鐘域路徑呢,比如MMCM輸出的兩個同步時鐘。

對于UltraScale/UltraScale+的FPGA,修改時鐘根節點的位置。Vivado在布局階段會自動給每個時鐘分配根節點的位置,以獲取最佳的時序性能。通常情況下,時鐘根節點位于其驅動負載的中心位置,如果不是,可以使用USER_CLOCK_ROOT調整。

避免關鍵路徑穿越SLR或輸入輸出列。

對于UltraScale/UltraScale+的FPGA,使用CLOCK_LOW_FANOUT屬性使時鐘網線驅動的負載位于同一個時鐘區域內。

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614596 -

時鐘緩沖器

+關注

關注

2文章

142瀏覽量

51256 -

Vivado

+關注

關注

19文章

831瀏覽量

68313

原文標題:FPGA中降低時鐘skew的幾種方法

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Skew definitions

Skew Correction Using Delay Li

時序分析之useful skew的作用分析

同步電路設計中CLOCK SKEW的分析說明

哪些因此會導致時鐘skew過大呢?FPGA中降低時鐘skew的幾種方法

哪些因此會導致時鐘skew過大呢?FPGA中降低時鐘skew的幾種方法

評論