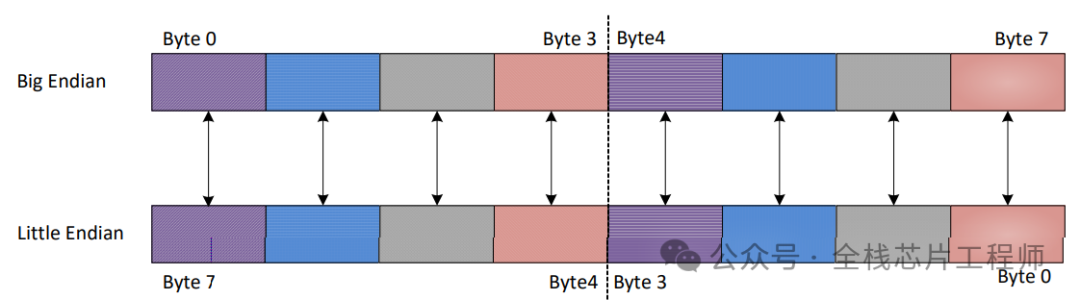

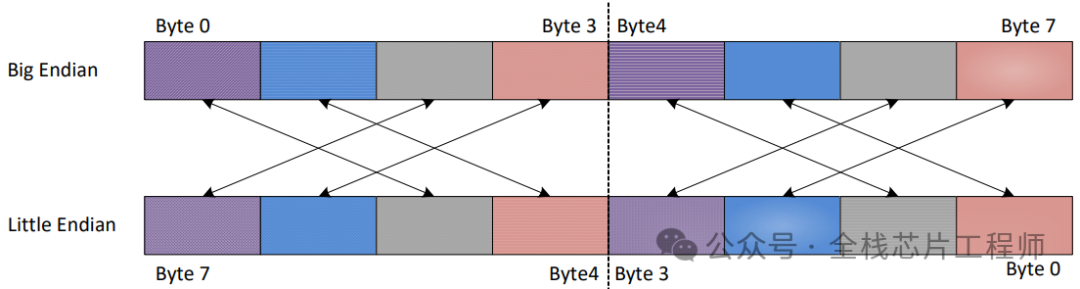

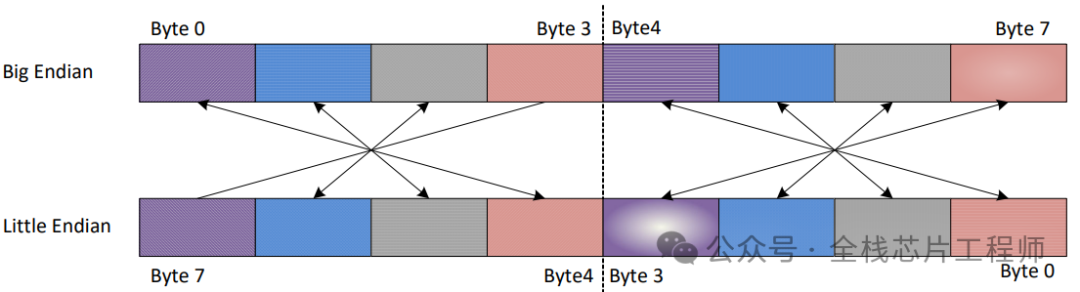

大端,最高字節(jié)存儲(chǔ)在最低的內(nèi)存地址,小端則是最低有效字節(jié)存儲(chǔ)在最低的內(nèi)存地址。在Verilog中實(shí)現(xiàn)大端(Big-Endian)和小端(Little-Endian)之間的轉(zhuǎn)換通常涉及到對(duì)多字節(jié)數(shù)據(jù)的操作。

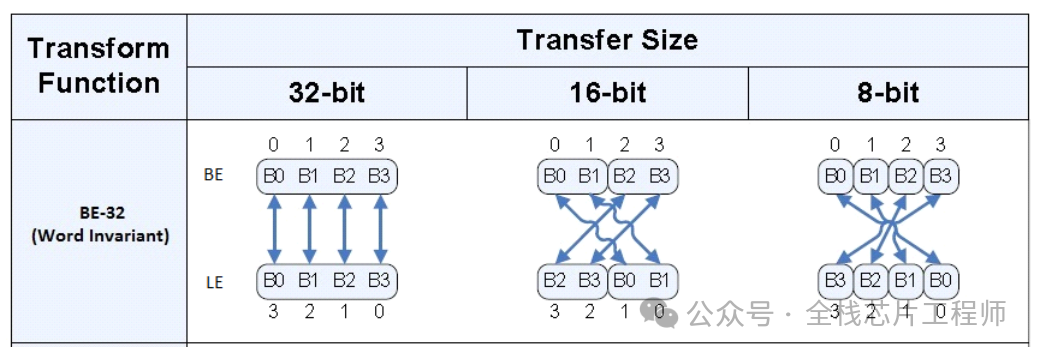

按照word傳輸不變的要求,一般我們可以分為三種:

第一種:word傳輸不變,Word access的處理。

第二種:word傳輸不變,half Word access的處理。

第三種:word傳輸不變,Byte access的處理。

以下是一個(gè)簡(jiǎn)單的Verilog代碼示例,展示了如何在大端和小端之間進(jìn)行轉(zhuǎn)換。這個(gè)例子中,我們假設(shè)要轉(zhuǎn)換的數(shù)據(jù)是一個(gè)32位的數(shù)字。

module endian_converter(

input wire clk, // 時(shí)鐘信號(hào)

input wire [31:0] data_in, // 輸入數(shù)據(jù),假設(shè)為大端格式

input wire [2:0] mode, // 模式選擇信號(hào),2'b00為大轉(zhuǎn)小,2'b01為小轉(zhuǎn)大

output reg [31:0] data_out // 輸出數(shù)據(jù)

);

// 根據(jù)模式選擇信號(hào)進(jìn)行字節(jié)序轉(zhuǎn)換

always @(*) begin

case (mode)

2'b00: begin // 大端轉(zhuǎn)小端

data_out[7:0] = data_in[31:24];

data_out[15:8] = data_in[23:16];

data_out[23:16] = data_in[15:8];

data_out[31:24] = data_in[7:0];

end

2'b01: begin // 小端轉(zhuǎn)大端

data_out[7:0] = data_in[7:0];

data_out[15:8] = data_in[15:8];

data_out[23:16] = data_in[23:16];

data_out[31:24] = data_in[31:24];

end

default: data_out = 32'b0; // 無效模式,輸出清零

endcase

end

endmodule

這個(gè)模塊在每個(gè)時(shí)鐘上升沿觸發(fā)時(shí)執(zhí)行轉(zhuǎn)換。根據(jù)mode的值,數(shù)據(jù)會(huì)被重新排列。對(duì)于大端轉(zhuǎn)小端(2'b00),最高有效字節(jié)(MSB)被移動(dòng)到最低有效字節(jié)(LSB)的位置,而最低有效字節(jié)被移動(dòng)到最高有效字節(jié)的位置。對(duì)于小端轉(zhuǎn)大端(2'b01),數(shù)據(jù)保持不變,因?yàn)槲覀兗僭O(shè)輸入已經(jīng)是按照預(yù)期的格式排列的。

審核編輯:黃飛

-

內(nèi)存

+關(guān)注

關(guān)注

8文章

3117瀏覽量

75143 -

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

112083

原文標(biāo)題:字傳輸不變的3種大小端處理方式

文章出處:【微信號(hào):全棧芯片工程師,微信公眾號(hào):全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

無鉛PCB的設(shè)計(jì)方法和表面處理方式選擇等介紹

基于android采用異步處理方式開發(fā)移動(dòng)護(hù)理程序的設(shè)計(jì)

介紹學(xué)習(xí)一種模擬信號(hào)的處理方式:對(duì)數(shù)處理

【經(jīng)驗(yàn)分享】系統(tǒng)常用 (電磁兼容)EMC處理方式

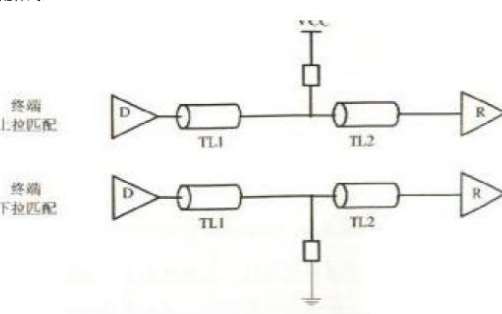

阻抗匹配的四種處理方式

AMT變速箱常見的故障及故障的處理方式

字傳輸不變的3種大小端處理方式

字傳輸不變的3種大小端處理方式

評(píng)論