3D NAND絕對(duì)是芯片制程的天花板,三星,海力士,英特爾,長(zhǎng)江存儲(chǔ)等都有3D NAND的產(chǎn)線,代表了一個(gè)國(guó)家的芯片制造水平。今天,我們就來(lái)剖析一下3D NAND的主要制作流程。

1,基底準(zhǔn)備:選擇12寸特定晶向的硅片。

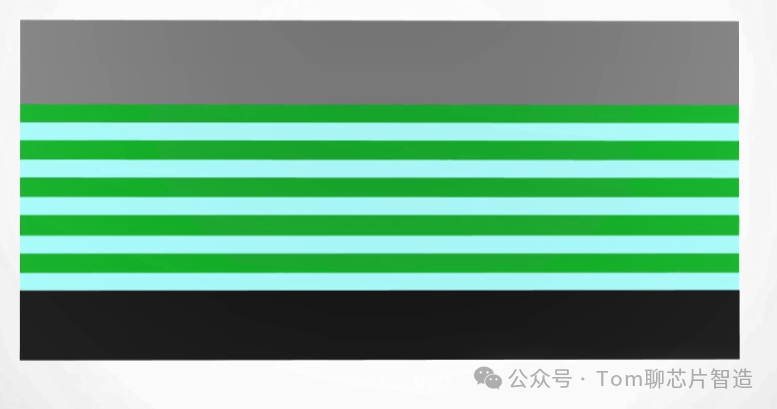

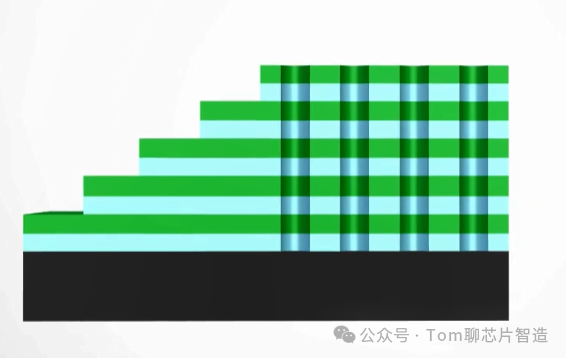

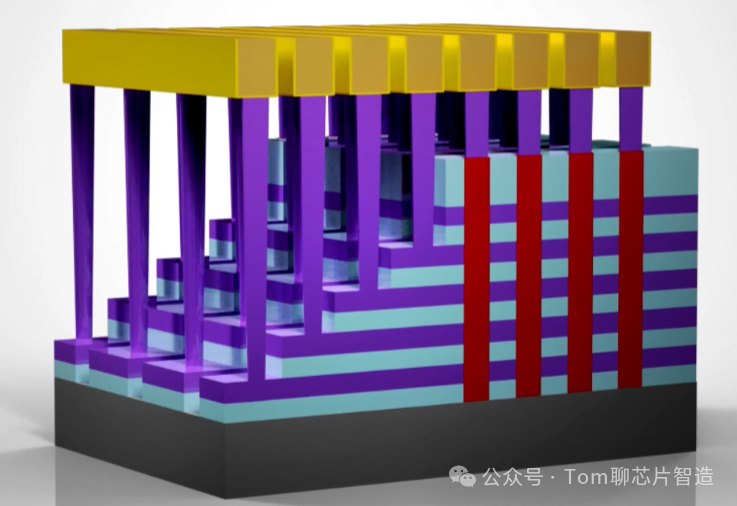

2,SiO2與SiNx交替鍍膜,每層膜層在幾十納米左右。根據(jù)產(chǎn)品的不同,膜層的層數(shù)也不同。圖中只是示意圖,只有幾層。但實(shí)際有64,128,400層等層數(shù)。

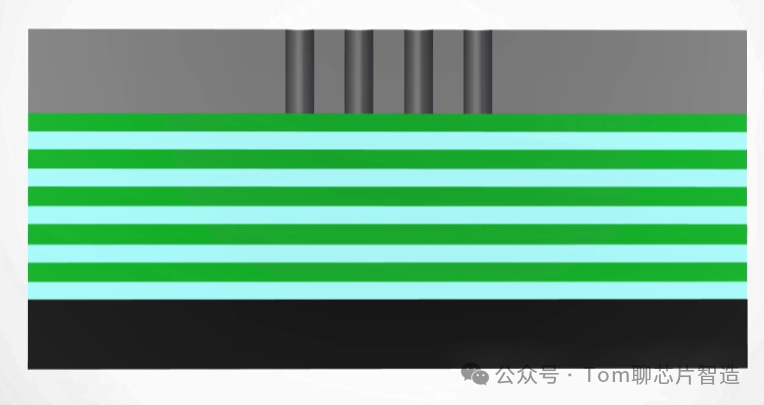

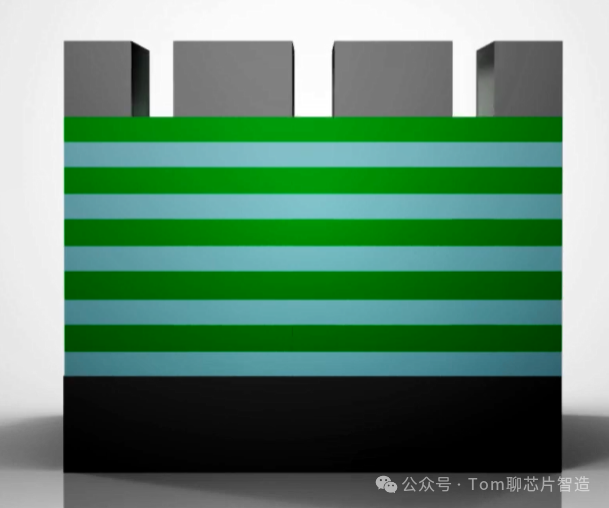

3,沉積無(wú)定形硅碳膜,這個(gè)是用來(lái)做溝道刻蝕的硬掩模。

4,硬掩模刻蝕,將硬掩模開口,以便于刻蝕堆疊的SiO2與SiNx材料

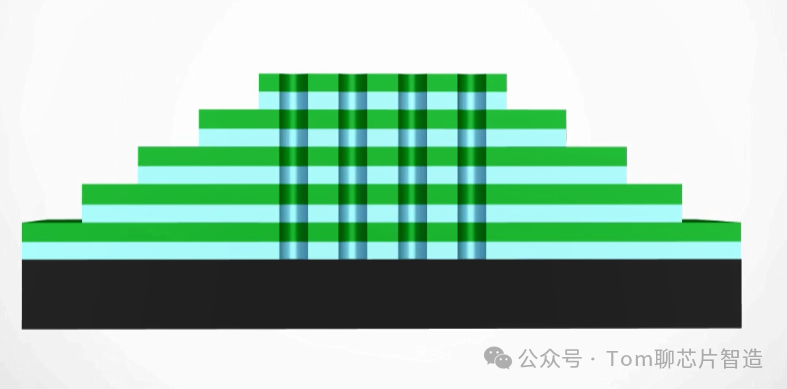

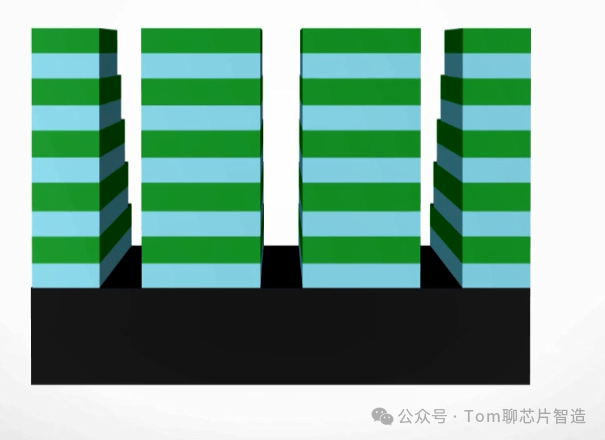

5,溝道通孔刻蝕

6,臺(tái)階刻蝕,見文章:

《3D NAND的臺(tái)階蝕刻(刻蝕)》

7,沉積無(wú)定形硅硬掩模,圖片為側(cè)視圖

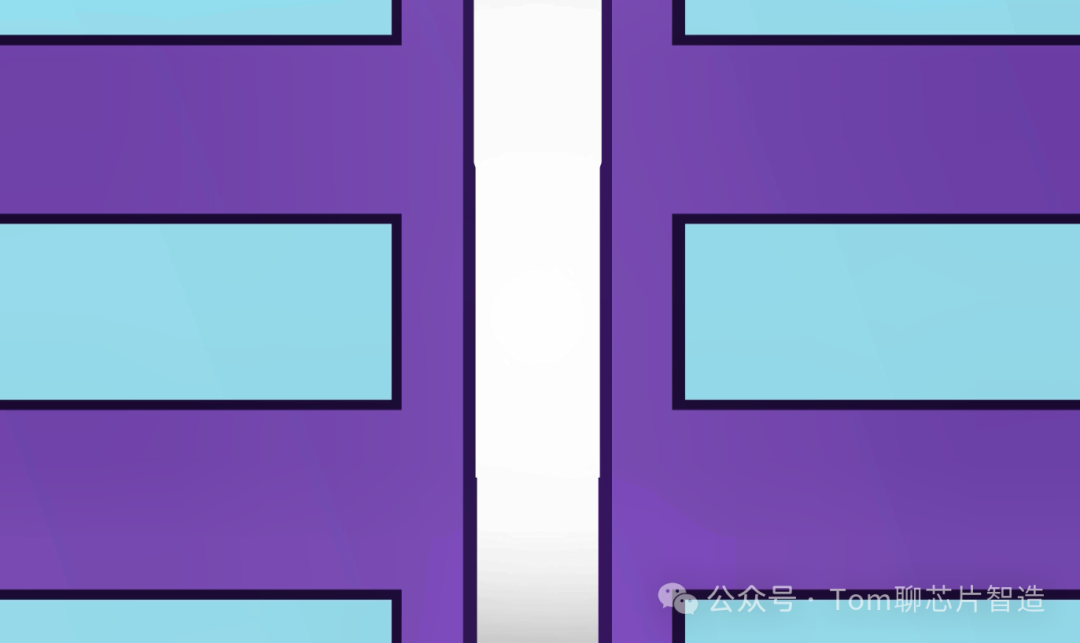

8,將硬掩模開孔

9,slit etch:將SiO2與SiNx的堆疊層刻蝕為一個(gè)個(gè)溝槽,

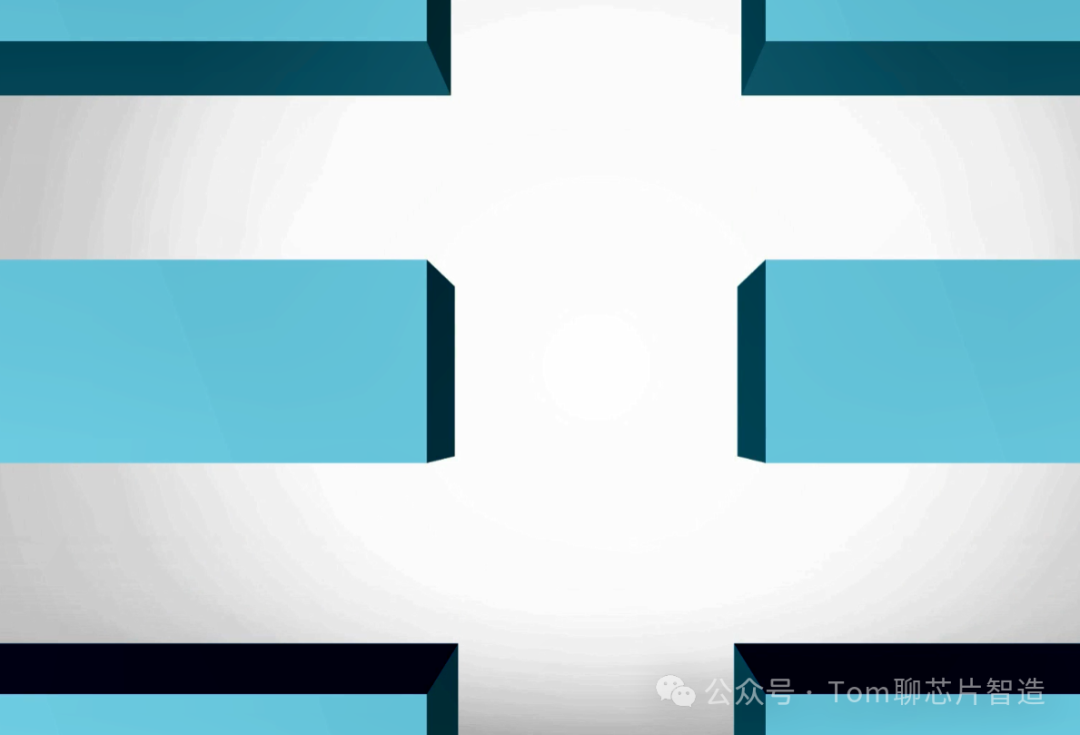

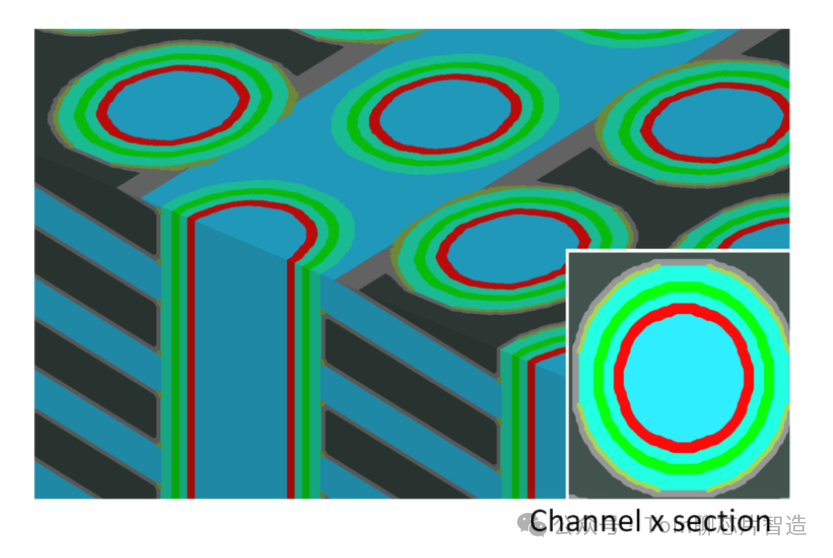

10,將堆疊層中的SiNx刻蝕掉,填充TiN,鎢(W)等,即word line fill工藝。

11,刻蝕掉多余的鎢,之后需要對(duì)溝道通孔進(jìn)行填充,因此需依次沉積阻擋氧化層,Charge Trap SiN (電荷陷阱氮化硅),Tunnel Oxide (隧道氧化物),Poly Si (多晶硅),Core SiO2 (硅基體)。功能區(qū)主體結(jié)構(gòu)完成。

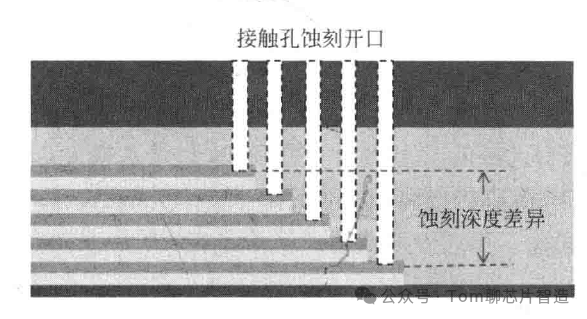

12,沉積介質(zhì)層,并用CCP-RIE進(jìn)行接觸孔蝕刻。

13,用金屬填充接觸孔,并制作出連接接觸孔的金屬導(dǎo)線-Bit line,3D NAND的整個(gè)制程結(jié)束。

文中精簡(jiǎn)了比較多的重復(fù)步驟,實(shí)際工藝在數(shù)百步以上。

注:轉(zhuǎn)載至 網(wǎng)絡(luò) 文中觀點(diǎn)僅供分享交流,不代表貞光科技立場(chǎng),如涉及版權(quán)等問題,請(qǐng)您告知,我們將及時(shí)處理

-

芯片

+關(guān)注

關(guān)注

459文章

52252瀏覽量

436909 -

NAND

+關(guān)注

關(guān)注

16文章

1719瀏覽量

137857 -

3D

+關(guān)注

關(guān)注

9文章

2953瀏覽量

109910 -

長(zhǎng)江存儲(chǔ)

+關(guān)注

關(guān)注

5文章

325瀏覽量

38271

發(fā)布評(píng)論請(qǐng)先 登錄

3D NAND的主要工藝流程

3D NAND的主要工藝流程

評(píng)論