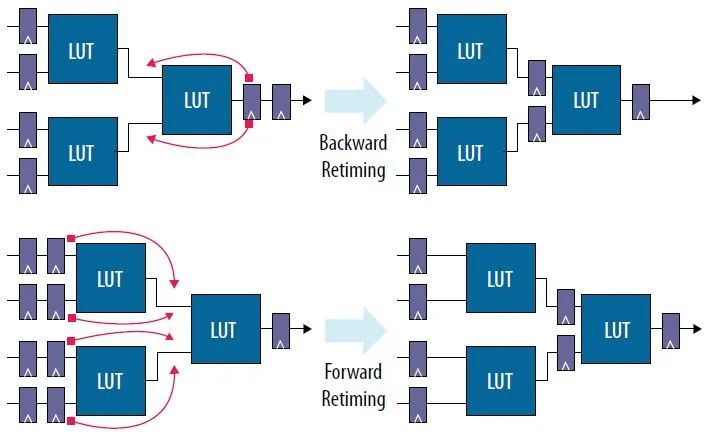

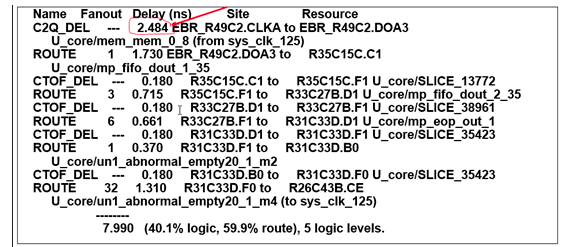

對于邏輯級數較大的路徑,常用的時序收斂的方法之一就是采用Retiming(中文翻譯為重定時)。Retiming到底是怎么回事呢?我們可以通過下圖理解。圖中通過搬移觸發器的位置減小了關鍵路徑的邏輯級數。無論是把觸發器向前搬移還是向后搬移,搬移后整個路徑的Latency和搬移前的Latency保持一致。可以看到Retiming的前提是相鄰路徑有可供搬移的觸發器,換言之,相鄰路徑的時序裕量較為“富余”,從這些“富余”中拿出一部分給時序較為緊張的路徑。這樣,時序緊張的路徑其邏輯級數降低了,而相鄰的時序“富余”的路徑邏輯級數增加了,達到整體邏輯級數的平衡。

Vivado提供了多種方法實現Retiming。在綜合選項設置界面提供了-retiming,如下圖所示。在這里,它是一個全局選項,作用于設計中的所有模塊。除此之外,Vivado還提供了模塊級綜合技術,可針對關鍵模塊使用Retiming,此時需要借助屬性BLOCK_SYNTH.RETIMING實現。顯然,這個綜合屬性是針對指定模塊的,所以這是一種更精細的設置方法。實踐證明往往全局選項-retiming加上模塊級Retiming能獲得更好的效果。

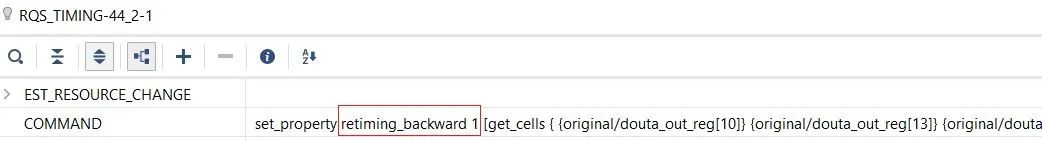

上述兩種方法人工干預度都較低,如果用戶能夠判定哪些路徑上的觸發器可搬移以改善相鄰路徑的時序,那么就可以使用Vivado提供的綜合屬性RETIMING_BACKWARD或RETIMING_FORWARD,直接將其作用于指定的觸發器。另外,在PSIP階段還可以使用屬性PSIP_RETIMING_BACKWARD或PSIP_RETIMING_FORWARD實現Retiming。對用戶而言,這一過程還是有一定難度的,好在Vivado提供了另外一種方式就是QoR建議,有時該報告就會包含Retiming的相關設置,如下圖所示。這樣用戶只需將該建議添加到工程中直接使用即可。

此外,phys_opt_design還提供了-directive AddRetime,既可在布局之后執行也可在布線之后執行。本質是是因為phys_opt_design提供了選項-retime。

審核編輯:黃飛

-

RAM

+關注

關注

8文章

1392瀏覽量

117503 -

觸發器

+關注

關注

14文章

2039瀏覽量

62141 -

Vivado

+關注

關注

19文章

835瀏覽量

68749

原文標題:如何對Block RAM使用Retiming(1)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FIFOPrimitive在Block RAM上有什么優勢?

Block RAM的功耗始終為0mW

請幫助我解決Block RAM問題?

創建Block RAM IP不起作用

請問9K Block RAM設計中那些2 9K Block RAM在哪里?

SPARTAN-3AN怎么使用標準JTAG命令讀取Block RAM內容

用INIT_XX初始化Block RAM的方法有哪些?

為什么Spartan 6 block ram有2個時鐘延遲?

請問分布式RAM和Block RAM的芯片中有menexternalmemory或內存嗎?

怎么使用virtex 5上的Block RAM來實現延遲線?

xilinx 7系列FPGA里面的Block RAM

關于Block RAM的寄存器輸出

如何運用Retiming優化Block RAM的使用

如何運用Retiming優化Block RAM的使用

評論