與通過源漏嵌入 SiC 應變材料來提高NMOS 的速度類似,通過源漏嵌入SiGe 應變材料可以提高PMOS的速度。源漏嵌入 SiGe 應變技術被廣泛用于提高90nm 及以下工藝制程PMOS的速度。它是通過外延生長技術在源漏嵌入SiGe 應變材料,利用鍺和硅晶格常數不同,從而對襯底硅產生應力,改變硅價帶的能帶結構,降低空穴的電導有效質量。

硅的晶格常數是5.431A,鍺的晶格常數是5.653A,硅與鍺的不匹配率是4.09%,從而使得 SiGe 的晶格常數大于純硅。圖2-10 所示為在硅襯底上外延生長 SiGe 應變材料外延。SiGe 應變材料會對橫向的溝道產生壓應力,從而使溝道的晶格發生形變,晶格變小。

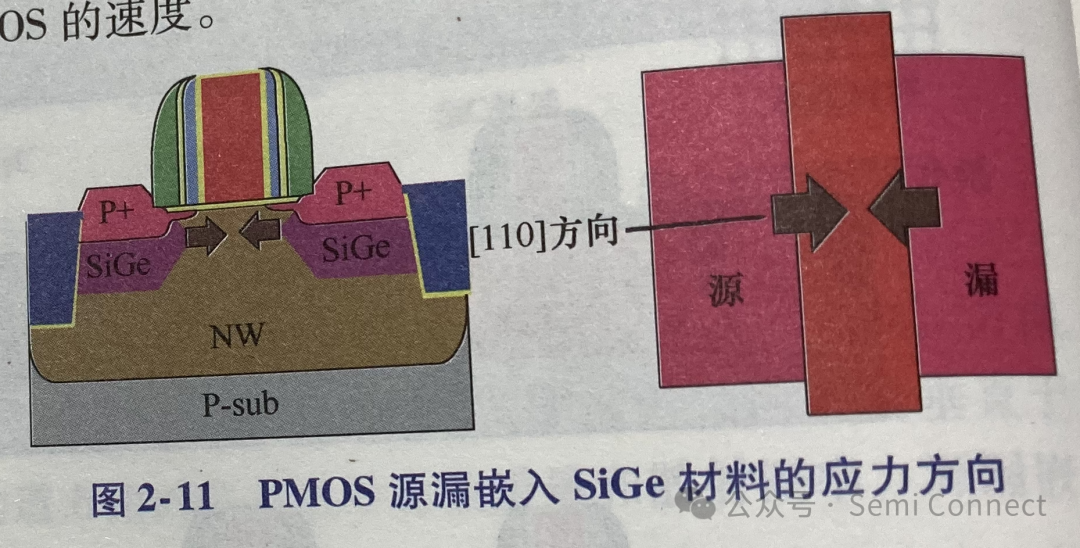

在 PMOS的源漏嵌入SiGe 應變材料,如圖2-11所示,PMOS 的溝道制造在[110]方向上,SiGe 應變材料會在該方向產生單軸的壓應力,該壓應力可以使價帶能帶發生分裂,重空穴帶離開價帶頂,輕空六帶占據價帶頂,從而減小溝道方向的空穴的電導有效質量,最終源漏嵌入 SiGe 應變材料可以有效地提高 PMOS 的速度。

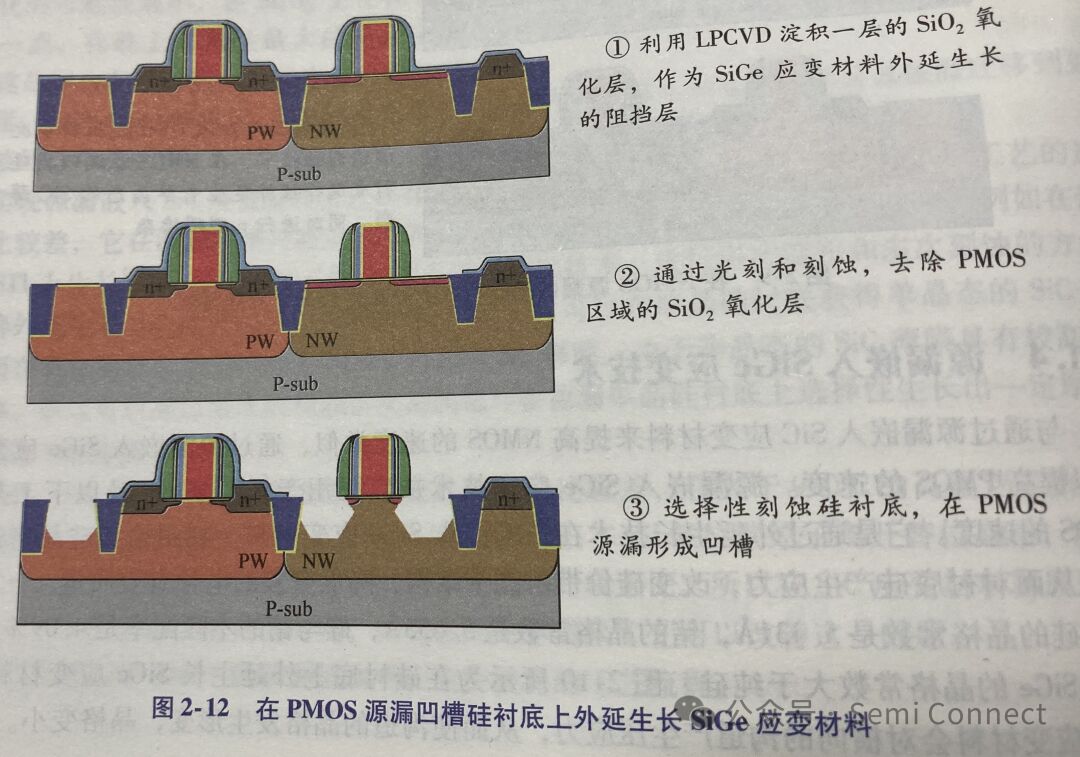

源漏嵌入 SiGe 應變材料也是利用選擇性外延技術生長的。源漏嵌入 SiGe 應變材料的工藝的硅源有SiCl4,SiHCl3,SiH2Cl3和SiH4,鍺源有GeH4,硅源中的氯原子(或者HCI)可以提高原子的活性,氯原子的數目越多,選擇性越好,這是因為氯可以抑制Si在氣相中和掩膜層表面成核。鍺含量是 SiGe 應變材料外延工藝的一個重要參數,鍺的含量越高,應力越大。但是,鍺含量過高容易造成位錯,反而降低了應力的效果。

圖2-12所示為PMOS 的源漏嵌入 SiGe應變材料的工藝流程。

-

SiGe

+關注

關注

0文章

99瀏覽量

23836 -

PMOS

+關注

關注

4文章

265瀏覽量

30249 -

晶格

+關注

關注

0文章

95瀏覽量

9422

原文標題:源漏嵌入 SiGe 應變技術

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

金屬電阻應變片工作原理簡介

基于分布式光纖應變傳感器技術的山體滑坡在線監測預警方案

漏源電壓VDS相關資料下載

SiGe技術提高無線前端性能

PNP與NPN哪個是“源”與”漏“的渾水

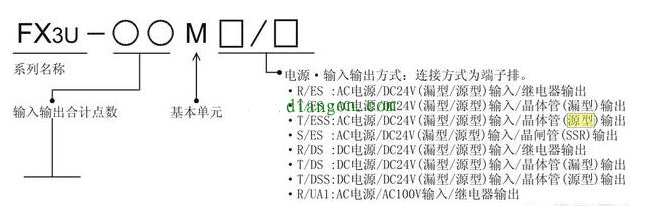

三菱PLC源型和漏型的區別

嵌入式源漏選擇性外延(Embedded Source and Drain Selective Epitaxy)

柵極源極漏極怎么區分?漏極 源極 柵極相當于三極管的哪極?

mos芯片源極漏極柵極在哪 mos管怎么判斷漏柵源極

SiGe外延工藝及其在外延生長、應變硅應用及GAA結構中的作用

源漏嵌入SiGe應變技術簡介

源漏嵌入SiGe應變技術簡介

評論