文章來源:老千和他的朋友們???

原文作者:孫千???

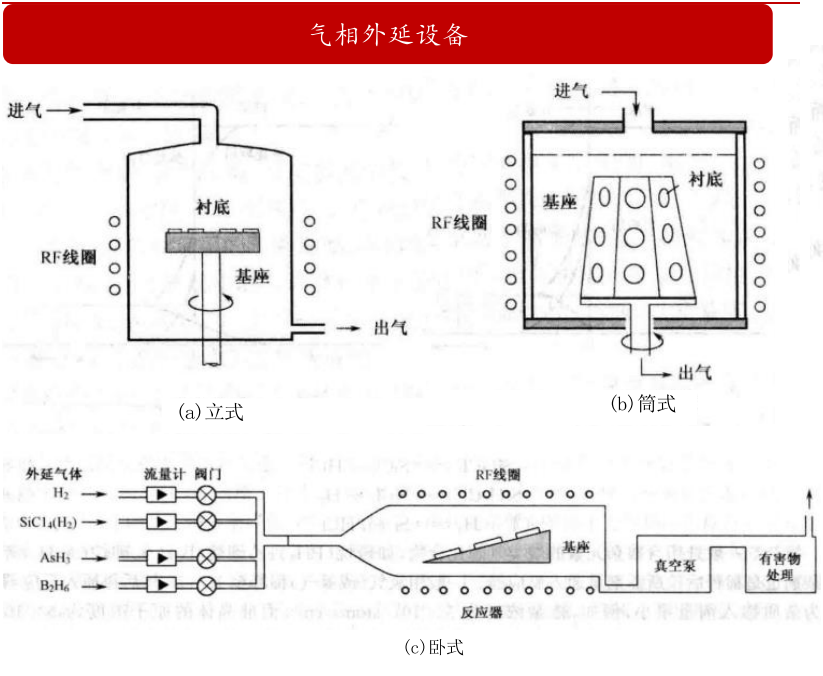

選擇性外延生長(SEG)是當今關鍵的前端工藝(FEOL)技術之一,已在CMOS器件制造中使用了20年。英特爾在2003年的90納米節點平面CMOS中首次引入了SEG技術,用于pMOS源/漏(S/D)應力器。它結合了抬升源/漏技術、凹槽刻蝕源/漏結形成技術以及硅鍺(SiGe)局部溝道應變技術。然而,有關SEG的首次報道可追溯至61年前,即1962年德州儀器的Joyce和Baldrey在《自然》雜志上發表的文章。

引言????

20世紀80年代,有超過120篇關于SEG(也稱為選擇性硅生長(SSG))在雙極性、CMOS、BiCMOS和電荷耦合器件(CCD)新型器件結構中各種研發應用的出版物。應用材料公司的Borland在1987年IEEE國際電子器件會議(IEDM)和1987年10月電化學學會(ECS)化學氣相沉積(CVD)-X研討會上報道了SEG器件應用的綜述。

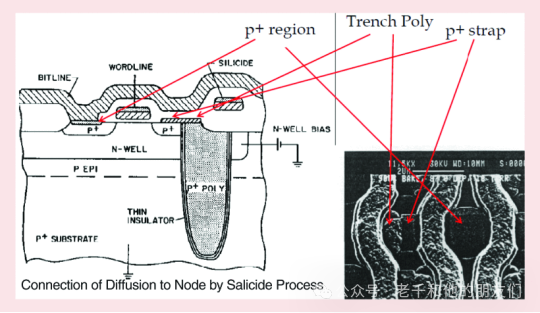

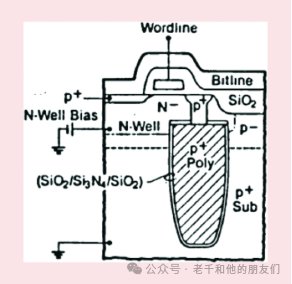

SEG首次大規模制造應用是由IBM/Burlington在1987年用于0.7微米技術節點的4兆動態隨機存取存儲器(DRAM)。如圖1所示,SEG工藝是一種選擇性硅表面帶,連接DRAM多晶硅溝槽電容器與晶體管。

圖1.1987年IBM 4兆位DRAM的選擇性硅帶

那年夏天,作者在佛蒙特州度過了一周美好時光,致力于SEG工藝研究。0.7微米技術節點的壽命很短,因為0.5微米節點的16兆DRAM在1988年就問世了,采用垂直側壁多晶硅連接溝槽電容器。

直到16年后,SEG的第二次大規模制造應用才出現,那就是英特爾2003年的90納米節點,它引入了局部應變硅技術,并使用凹槽刻蝕選擇性SiGe抬升源/漏技術用于pMOS,如Ghani等人所報道的。eSiGe源/漏應力器技術在2011年22納米節點的3D鰭式場效應晶體管(FinFET)中得以延續。

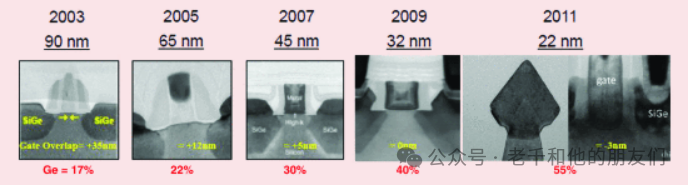

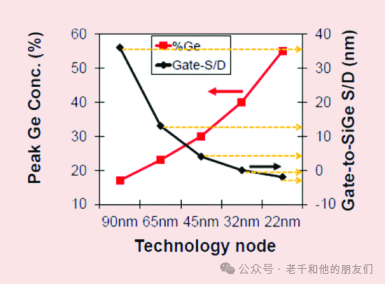

Borland在2016年11月日本學術振興會第七屆硅材料先進科學技術國際研討會上的特邀報告"智能手機市場推動7納米和5納米節點3D器件和堆疊器件"展示了凹槽刻蝕選擇性SiGe pMOS源/漏結構的透射電子顯微鏡(X-TEM)截面演變,從平面90納米節點(17% SiGe,柵極重疊控制+35納米)到鰭式22納米節點(55% SiGe,柵極重疊控制-3納米),如圖2所示。

圖2.從90納米至22納米節點的凹槽刻蝕選擇性硅鍺源/漏結構的X-TEM分析

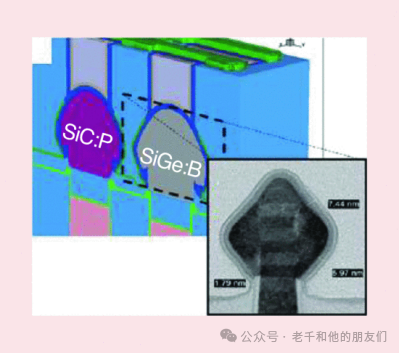

二十年后,選擇性源/漏結構繼續成為主流前端工藝,并演變為3納米以下節點3D CMOS環繞柵極(GAA)納米片器件的環繞接觸(WAC),如IBM聯盟的Loubert等人所報道,如圖3所示。

圖3.三維納米薄片的選擇性WAC

選擇性WAC預計將使SEG技術在2030年代再延續十年,應用于3D堆疊CMOS器件,同時進行新材料改性研究以降低接觸電阻。下面按照各個十年回顧SEG技術的一些關鍵開創性文章。

按十年代劃分的SEG發展

1960年代

德州儀器的Joyce和Baldrey在1962年《自然》雜志上發表的題為"硅的選擇性外延沉積"的文章中首次報道了使用SiCl?在1200°C大氣壓下通過氧化物掩膜進行SEG。三年后,1965年,Jackson報道了向SiCl?同時注入HCl,抑制在氧化物表面上的硅沉積。

1970年代

20世紀70年代有12篇SEG出版物,報道了其他用于選擇性硅的源氣體,包括SiH?和硅-碘。Dumin在其文章"使用硅烷和鍺烷的選擇性外延"中報道了使用GeH?源氣體在800°C進行選擇性鍺生長;他報道在700°C時是非選擇性的。西屋電氣研發中心的研究人員Rai-Choudhury和Schroder報道了選擇性砷化鎵(GaAs)沉積。

1980年代

20世紀80年代的SEG出版物增加了10倍,達到120多篇,其中使用降低壓力的CVD外延系統在較低溫度下進行SEG的材料質量取得了突破。1982年,日本電氣公司(NEC)的Tanno等人報道了在低于1000°C和80托壓力下使用SiH?Cl?+HCl添加劑進行SEG以改善選擇性。

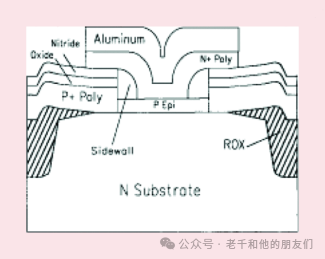

當時,工業界也正從雙極性向CMOS和BiCMOS技術過渡。然而,IBM大型機仍然基于高速雙極性技術。來自IBM約克鎮高地的Burghartz等人在1988年5月《電子器件快報》(EDL)上報道了SEG首次用于雙多晶硅自對準結構中的基極形成,題為"選擇性外延基極晶體管(SEBT)",如圖4所示。

圖4.IBM用于高速雙極型的選擇性外延基極晶體管

IBM選擇了Meyerson的超高真空/CVD外延方法。麻省理工學院的O等人在1987年5月ECS會議上報道了使用另外兩個掩膜步驟與SEG的其他BiCMOS設計,將垂直NPN和PNP雙極性晶體管插入p阱CMOS工藝流程。

CMOS的引入面臨的關鍵挑戰之一是pMOS和nMOS器件隔離和閂鎖效應預防。Borland在IEDM-1987的特邀演講中回顧了SEG新型器件結構:1)橫向器件隔離,2)用于n型和p型硅結構的選擇性摻雜,3)抬升源/漏,4)接觸填充,以及5)絕緣體上硅(SOI)的形成。

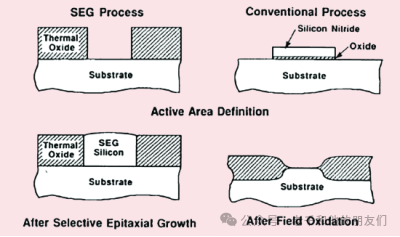

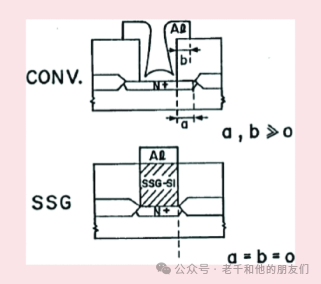

橫向器件隔離:Borland和Drowley在應用材料公司和惠普實驗室于1985年8月發表的《固態技術》文章中,回顧了替代局部硅氧化的先進介電隔離技術,包括SEG隔離,如圖5所示。

圖5.用于先進介質隔離的SEG

SEG側壁面形成和缺陷出現在(110)側壁上;然而,在(100)氧化物側壁上實現了無面和無缺陷的SEG。SEG隔離工藝流程類似于今天我們所稱的"鰭后工藝"(而非"鰭先工藝"),通過SEG在硅晶圓表面上方創建抬升的硅臺結構。

淺溝槽隔離(STI)工藝在20世紀80年代末0.5微米技術節點引入,是相反的"鰭先"類工藝,通過臺面刻蝕硅晶圓創建抬升的硅結構。它避免了在刻蝕損傷的硅表面上生長高質量SEG的困難、界面雜質和側壁面形成/缺陷。

為了將SEG面形成/缺陷限制在n阱區域并將CMOS的橫向隔離極限推至<0.25微米,來自NEC的Kasai等人在IEDM-1985上報告了一種4微米深、0.25微米寬的高縱橫比SEG窄隔離結構,用于n阱CMOS,如圖6所示。

圖6.采用SEG的CMOS窄隔離間距

垂直側壁上的氧化物厚度成為窄隔離寬度。單阱CMOS,無論是n阱(使用p型晶圓最常見)還是p阱(使用n型晶圓),主導了CMOS技術;只有少數公司使用雙阱CMOS,如AT&T,提供了使用p型或n型晶圓的靈活性。將n型晶圓用于CMOS,特別是n/n+ epi晶圓,由于內在吸雜能力差而存在問題。

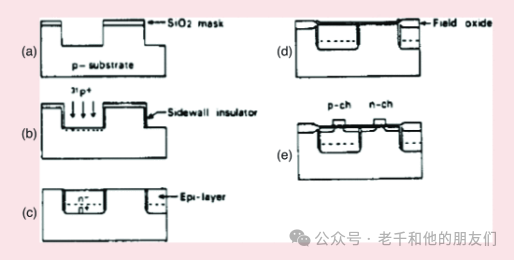

選擇性摻雜:Manoliu和Borland在IEDM-1987上發表了一篇聯合仙童研究和應用材料公司的論文,報告了用于n阱和p阱的有源區選擇性摻雜,用于亞微米雙阱CMOS,展示了優異的閂鎖特性,無需深溝槽,如圖7所示。雙掩埋層形成了雙阱逆向摻雜阱,并使用鈦(Ti)進行硅化物接觸。

圖7.雙埋層雙阱CMOS

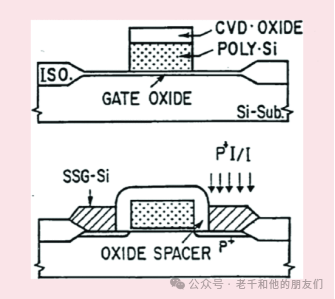

抬升源/漏:對于硅外延質量不重要的非有源器件區域,使用選擇性硅或多晶硅沉積形成抬升源/漏結構。來自東芝的Hashimoto在1988年12月應用材料公司第三屆年度先進器件結構外延技術創新研討會上,展示了無摻雜SSG隨后進行B注入的抬升源/漏,如圖8所示。源/漏結是通過從注入的抬升源/漏結構中p+硼擴散形成的。

圖8.東芝抬升源/漏結構

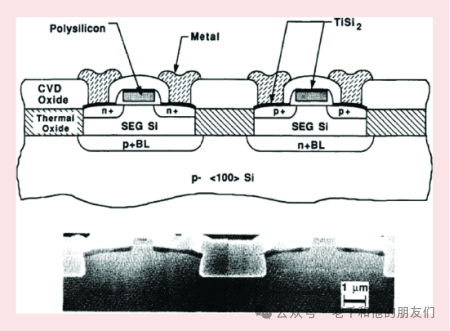

接觸填充:Shibata等人來自東芝在1987年VLSI技術研討會上報告了原位n+磷摻雜SEG用于接觸填充。由于這是非有源器件區域,硅外延質量不重要,他們制造了1-Mb靜態隨機存取存儲器(SRAM),具有平坦的金屬接觸,沒有不共形金屬鍵孔結構,用于改進自對準接觸(SAC),如圖9所示。

圖9.用于平面SAC的原位摻雜n+ SSG

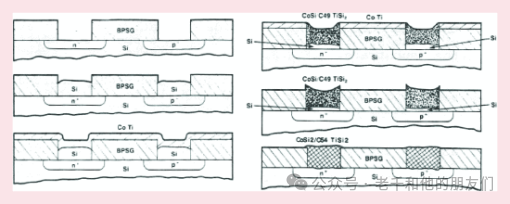

Wei等人在1989年ECS超大規模集成科學和技術研討會和VMIC-89上發表了一篇英特爾和應用材料公司的聯合論文,報告了另一種方法,使用接觸硅化。他們報告使用無摻雜選擇性硅插塞用于n+和p+接觸填充,隨后沉積鈷(Co)或鈦(Ti)并進行硅化,如圖10所示。

圖10.選擇性硅接觸填充,隨后形成Co或Ti硅化物

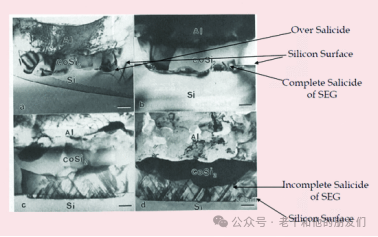

圖11顯示了過度硅化[圖11(a)]、完美硅化[圖11(b)]和不足硅化[圖11(c)和(d)]的X-TEM結果。這種厚硅化物技術將成為21世紀開發的用于高k金屬柵極(HK/MG)的FUSI柵極的前身。

圖11.(a)–(d) SSG-SAC隨后形成鈷硅化物的X-TEM結果

SOI形成:Jastrzebski在1984年12月的《晶體生長雜志》中報告了橫向生長SEG覆蓋氧化物,稱為外延橫向超生長(ELO),形成局部SOI結構,并在圖12中說明了用于雙阱CMOS的應用。使用化學機械拋光(CMP),完全拋光回和SOI層變薄的ELO結構,不含任何表面面形成凹坑,如圖13所示。

圖12通過ELO形成SOI

圖13CMP被用于拋光和減薄由ELO形成的SOI層

SEG DRAM溝槽電容器設計:從1-Mb DRAM 1.0微米技術節點開始,IBM自1985年以來一直使用多晶硅溝槽存儲電容器單元設計。在1987年的4-Mb DRAM 0.7微米技術節點,他們使用選擇性硅表面帶隨后進行硅化作為連接到溝槽存儲電容器的局部互連,如圖1所示。

SSG晶體結構在p+硅晶體管源/漏區域上是單晶的,在p+多晶溝槽電容器單元上方是多晶硅。IBM研究人員在1988年展示了各種設計選項,將SEG納入潛在的0.35微米節點64-Mb DRAM及更高,包括使用溝槽上外延(EOT)設計的埋入式溝槽電容器,該設計結合了ELO和CMP平面化,如圖14所示,由Lu和Bronner在1988年12月應用材料公司第三屆年度先進器件結構外延技術創新研討會上報告。

圖14.選擇性EOT DRAM

20世紀90年代

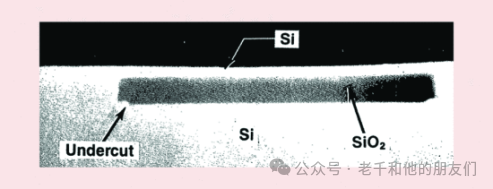

低溫預SEG硅表面清潔和去除等離子體刻蝕損傷和殘留物繼續限制SEG在有源器件區域的應用。許多組織研究了減少厚氧化物刻蝕后殘留刻蝕損傷和表面雜質的方法。犧牲氧化物最好能消耗殘留刻蝕效應,而外延氫氣烘烤步驟導致硅表面遷移/平滑,輕微的氧化物下切,以及氫表面鈍化被證明對本征氧化物生長非常有抵抗力。從H2烘烤/退火步驟中學到的好處將用于其他工藝應用。

東芝陶瓷公司使用高溫H2退火進行氫去核,并作為高質量Hi晶圓銷售給半導體制造商,如1993年5/6月的《日經微器件》所報道。Gardner等人在1994年VLSI技術研討會上發表了AMD和Genus的聯合文章,題為"氫去核用于增強薄氧化物質量、器件性能和潛在外延消除"。

在2010年代,研究發現氫退火還能減少線邊緣粗糙度,在硅側壁刻蝕鰭和硅波導結構后導致硅表面平滑。HF蒸氣刻蝕也被研究用于選擇性氧化物刻蝕,作為獨立和集成集群工具,但留下氟鈍化表面,如Borland在1992年雙極/BiCMOS電路和技術會議上報道和de Larios等人在1993年SSDM上報道。

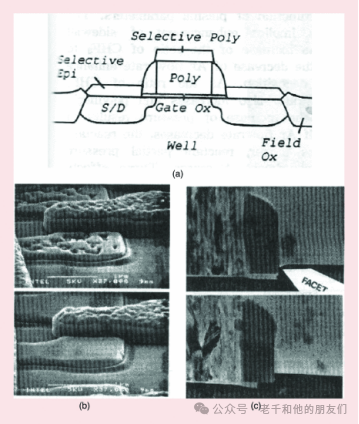

英特爾的Weldon等人在1994年5月ECS會議上報告了"使用選擇性硅沉積的抬升源-漏用于亞半微米CMOS器件"。他們展示了表面預清潔處理對SEG抬升源/漏結構表面粗糙度和面形成的影響,如圖15所示,輕微的源/漏下切消除了側壁面。圖15(a)說明了SEG抬升源/漏結構,顯示源/漏區域上的選擇性外延和柵極上的選擇性多晶硅。圖15(b)顯示了n+源/漏區域的掃描電子顯微鏡表面形貌,對于900°C 1分鐘H2烘烤顯示點狀SEG成核和生長,對于950°C 1分鐘H2烘烤顯示均勻SEG生長。圖15(c)顯示氧化物下切情況下沒有側壁面形成。

圖15(a)–(c)預清洗處理后提高的源/漏(S/D)表面質量。

同時,對超淺結(USJ)形成也存在擔憂。北卡羅來納州立大學(NCSU)的一組研究人員,由Ozturk教授領導,在半導體研究公司-SEMATECH的資金支持下,研究了這些問題,并從1999年開始發表研究成果,展示了SEG用于源/漏工程如何將國家技術路線圖半導體(NTRS)路線圖擴展到亞30納米節點。

他們的第一篇論文由Ban和Ozturk在1999年5月ECS研討會上關于快速熱處理進展的報告,題為"使用選擇性生長的原位硼摻雜硅薄膜的50-70nm CMOS超淺P+-N結",實現了SEG源/漏B水平高達3E21/cm3,比硼在硅中的固體溶解度極限高一個數量級。

一年后的2000年,NCSU研究小組將報告通過添加Ge形成SiGe合金然后添加硅凹槽刻蝕的改進效果。

2000年代

NCSU在2000年的第一篇論文發表于ECS 2000年5月快速熱處理和其他短時間工藝技術研討會上,由Gannavaram和Ozturk撰寫,題為"用于35-70 nm CMOS的選擇性沉積高濃度硼摻雜硅鍺薄膜制備的超淺P+-N結"。他們報告了S/D區域30 nm的凹槽刻蝕,隨后進行原位硼摻雜SiGe(45-75%)。他們報告S/D區域的高SiGe壓縮應變被1-5E21/cm3濃度的小型硼摻雜原子所補償;20% SiGe需要2.5% B,而80% SiGe需要10% B來實現應變補償。

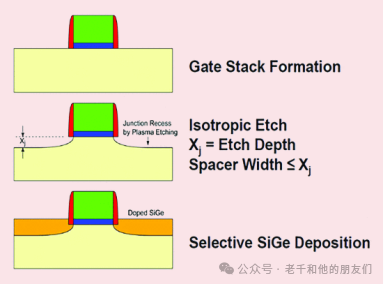

七個月后,在IEDM-2000,Gannavaram等人的論文18.3介紹了一種新的CMOS S/D工藝技術,這一技術最終將摩爾定律延伸了另外二到三十年,直至2025年及以后。他們的論文標題是"用于亞70納米CMOS的低溫(<800°C)凹槽結選擇性硅鍺源/漏技術"。

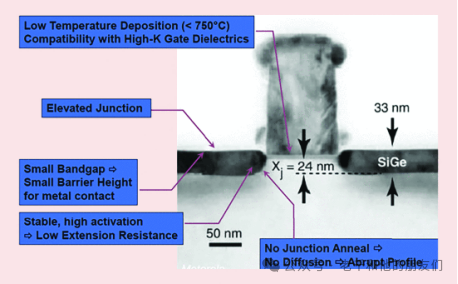

作者認為這是他們關于S/D選擇性外延生長的第一篇開創性論文,因為該論文指出這項新技術滿足NTRS路線圖的要求:1)30納米結的Rs/Xj <100 Ω/sq,2)超低電阻率接觸(1.5×10-8 Ω-cm2),3)優異的反向漏電特性,4)完美的盒形橫向陡峭度,以及5)使用傳統柵極后CMOS工藝流程與HK柵介質的熱集成兼容性。

誰能預見到七年后的2007年,英特爾將推出其45納米節點混合HK先/MG后技術,隨后在32納米節點采用HK/MG后工藝。NCSU提倡單一S/D CMOS晶體管設計,而不是傳統的淺源漏延伸區(SDE)或輕摻雜漏極(LDD)與深S/D結構。凹槽硅刻蝕(等離子體刻蝕)深度將決定淺結深度,達到<30 nm。

為了將原位硼摻雜濃度從硅中2E20/cm3的固溶限提高到7E20/cm3,他們使用了選擇性SiGe合金沉積(45-66%),并提到SiGe引起的壓縮應變被替位硼原子所補償/緩解,導致更高的摻雜劑摻入,正如他們在2000年5月ECS論文中早先報告的那樣。圖16說明了通過等離子體刻蝕的凹槽刻蝕步驟,然后進行選擇性摻雜SiGe S/D。圖17所示的X-TEM分析顯示了用于USJ的24納米凹槽刻蝕。

圖16.源/漏凹槽刻蝕,隨后進行選擇性硅鍺源/漏

圖17凹槽結選擇性硅鍺源/漏的橫截面透射電子顯微鏡圖

兩年后,在2002年10月ECS半導體硅研討會上,Ozturk等人的受邀論文"基于選擇性CVD SiGe合金的30納米以下CMOS技術節點新結技術",我認為這是他們的第二篇開創性論文,因為它描述了在2003年英特爾90納米節點中可以找到的關鍵SiGe SEG工藝步驟。

S/D形成涉及將S/D區域凹槽刻蝕到所需的結深度,隨后進行選擇性SiGe沉積,同時形成抬高的S/D結構以改善接觸形成。他們使用鎳(Ni)形成鍺硅化物以獲得低接觸電阻。該論文還提到,在高溫結形成后需要HK/MG后工藝,這與英特爾在2007年推出的45納米節點混合HK先/MG后工藝非常相似。

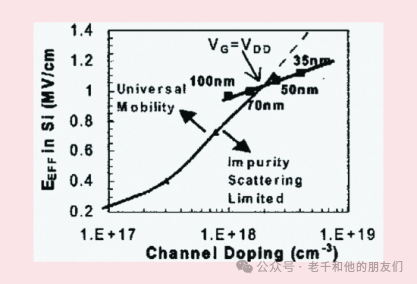

英特爾90納米節點引入了pMOS的eSiGe S/D應力器和nMOS的CVD應力襯墊。正如英特爾的Ghani等人在2000年VLSI技術研討會上報告的,隨著溝道摻雜濃度增加到>2E18/cm3,雜質散射占主導地位,需要溝道遷移率增強,如圖18所示。

圖18.溝道摻雜濃度對雜質散射的影響

因此,圖19顯示了從90納米節點的平面結構到22納米節點的3D FinFET的五代pMOS選擇性SiGe S/D應力器,鍺含量從17%增加到55%,以及最佳柵極重疊/非重疊距離(+35 nm至-3 nm),這需要對英特爾Kuhn等人在IEDM-2012上報告的硅橫向凹槽刻蝕進行關鍵控制。

圖19.SiGe濃度與柵極重疊的關系

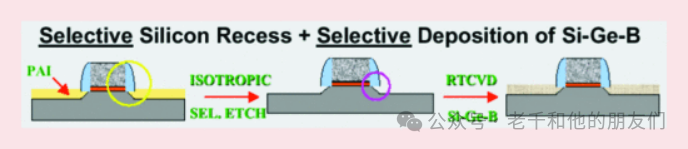

垂直和橫向硅凹槽刻蝕步驟對于優化柵極到S/D在溝道應變上的重疊至關重要。德州儀器的研究人員報告了他們用于SDE應變硅的SEG eSiGe活動。為了控制凹槽刻蝕工藝,Mansoori在2002年Varian年度vTech技術研討會上報告了使用預非晶化注入(PAI)進行各向同性選擇性刻蝕控制,隨后進行選擇性Si-Ge-B沉積,如圖20所示。

圖20.使用PAI注入實現各向同性選擇性刻蝕控制

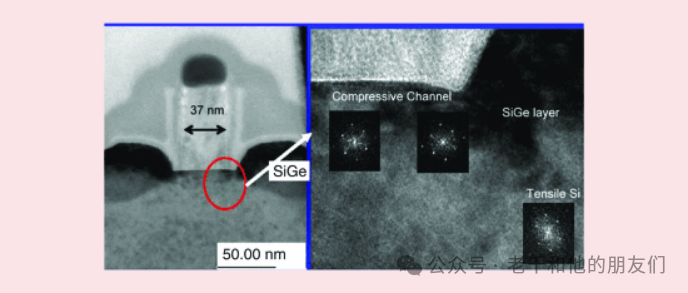

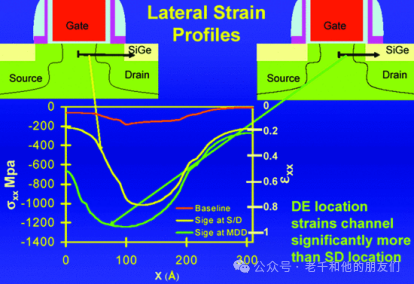

Chidambaran在vTech 2004上展示了高分辨率(晶格成像)X-TEM應變硅分析結果,圖21顯示壓縮溝道區域和拉伸S/D區域。圖22顯示了德州儀器獨特的漏極延伸(DE) eSiGe工藝的橫向應變模擬結果,該工藝比記錄中的S/D eSiGe工藝提供更高的溝道應變。

圖21漏極延伸區SiGe應力層的X-TEM分析

圖22.SiGe DE的橫向應變模擬剖面圖

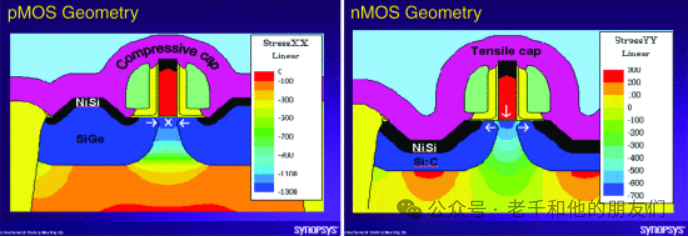

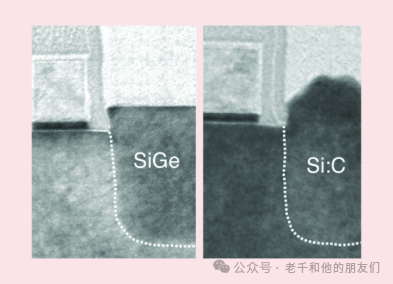

在2005年5月ECS會議上,Synopsys的Moroz報告了用于凹槽刻蝕選擇性外延的應變硅器件模擬,pMOS使用SiGe,nMOS使用SiC,結合CVD應力帽,如圖23所示:pMOS溝道橫向應變高達-1,300 MPa,nMOS溝道橫向應變為+400 MPa。

圖23.應變硅的SiGe源/漏區P型MOS和SiC源/漏區N型MOS的模擬結果

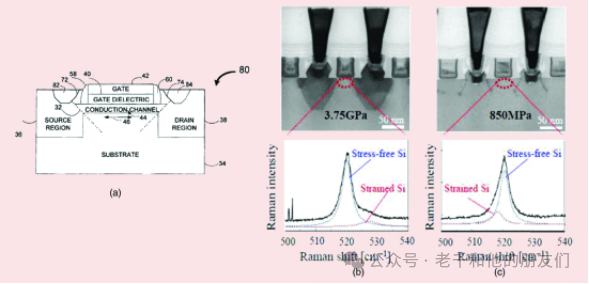

英特爾在32納米節點繼續避免使用選擇性SiC S/D應力器,而是使用作者稱之為堆垛層錯應力器的技術,如圖24(a)所示,由Weber等人在其美國專利申請"增強錯位應力晶體管"中報告。明治大學的Ogura小組告訴我,他們如何從東京秋葉原地區的電子商店購買英特爾32納米芯片,并進行了詳細的X-TEM分析、拉曼應變分析和能量色散X射線(EDAX)化學分析,如圖24(b)、(c)和25所示,分別針對pMOS和nMOS。

圖24.(a)–(c)明治大學對英特爾32納米節點eSiGe型pMOS和堆垛層錯應力源nMOS的應變分析

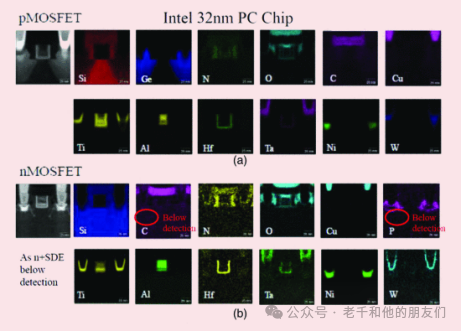

拉曼分析顯示,具有40% eSiGe S/D和0 nm柵極重疊的pMOS溝道應變為3.75 GPa,而他們測量到具有堆垛層錯應力器的nMOS溝道應變為850 MPa,盡管英特爾專利提到了碳化硅材料。EDAX技術要求化學水平>2%至3%才能檢測到,Ge為藍色,Si為紅色,C為紫色,Ti為黃色(圖25)。32納米節點清晰顯示了HK/MG后多化學層組成。直到IBM在IEDM-2012上報告的22納米節點PD-SOI,選擇性SiC-S/D才用于平面CMOS,如圖26所示,它們采用了HK/MG先工藝。

圖25.(a)和(b)英特爾32納米節點的詳細X-TEM和EDAX化學分析

圖26IBM采用雙重硅鍺和碳化硅源/漏應力技術的22納米節點PD-SOI

2010年代

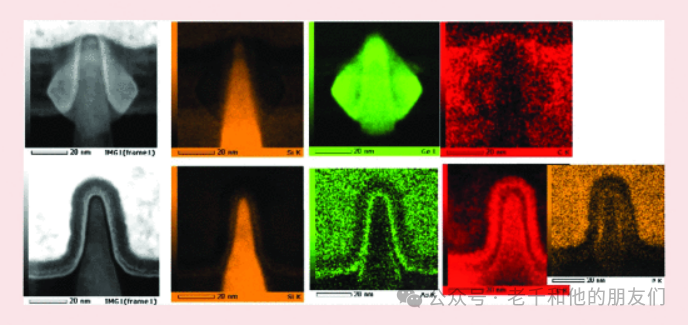

英特爾在2011年以22納米節點引入了3D FinFET器件架構,采用類似STI的鰭先方法,使用刻蝕的硅臺結構和SEG eSiGe S/D應力器,如圖2所示。如前面圖25所示,EDAX用于晶體管的化學分析是一種強大的工具。

2013年,明治大學的Ogura小組檢查了英特爾22納米FinFET,如圖27所示。nMOS鰭區域顯示有As(圖27中的綠色)、P(圖27中的橙色)和C(圖27中的紅色)注入的證據,而pMOS鰭區域顯示綠色的Ge-S/D(圖27)。S/D區域沒有選擇性SiC外延的證據。

圖27. Intel 22納米鰭式場效應晶體管(FinFET)的EDAX化學分析,顯示了用于nMOS的P、As和C元素注入的證據

在FinFET 14納米節點,凹槽刻蝕選擇性外延SiCP S/D用于nMOS終于成為塊狀CMOS技術的主流。圖28中的X-TEM分析顯示了雙SEG S/D應力器,這是由Chipworks的James在2015年Semicon/West AVS-西海岸結技術用戶組會議上報告的。這顯示了三星Galaxy S6中使用的三星Exynos 7420應用處理器;注意選擇性S/D結構是合并的,限制了用于金屬接觸形成的頂部表面。

2020年代

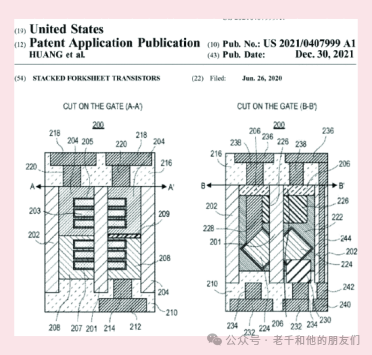

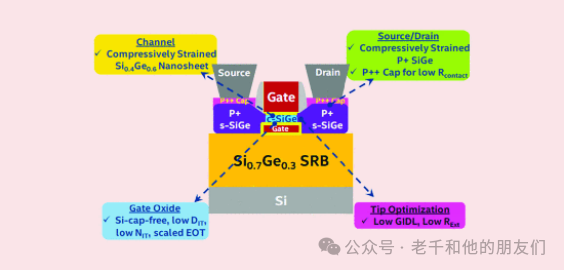

行業計劃在亞3納米節點遷移到3D GAA納米片器件,三星在3納米節點率先采用。對于環繞接觸(WAC),使用SEG eSiGe-B用于pMOS和eSiC-P用于nMOS S/D變得至關重要,如圖3所示。這將持續到下一個十年,正如英特爾的Huang等人在他們的堆疊CMOS叉形片美國專利中報告的那樣,如圖29所示,該專利使用SEG實現了環繞n+和p+接觸。

圖29.英特爾CMOS堆疊叉形片專利,展示SEG-S/D環繞接觸點

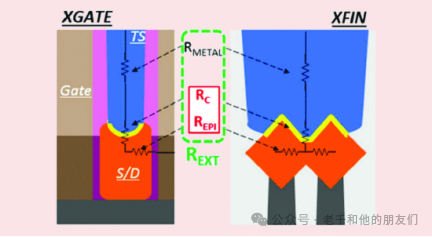

圖29中的"柵極上切割"圖像清晰地顯示了堆疊CMOS納米片器件的菱形SEG-WAC結構。如Gluschenkov等人在2023年國際結技術研討會上報告并在圖30中說明的那樣,接觸電阻變得至關重要,因為在環繞接觸中金屬只接觸SEG-WAC結構的頂部表面。

圖30.改善SEG-S/D的接觸電阻

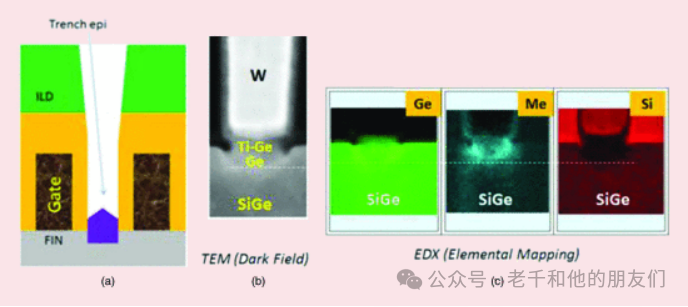

他們報告,金屬到S/D界面的低接觸電阻在堆疊CMOS中將變得更加關鍵和具有挑戰性,需要新的先進退火和表面材料修飾/工程技術。一個例子是他們的選擇性"溝槽"外延工藝,如圖31所示,旨在改善接觸電阻,由Xie等人和Gluschenkov等人在IEDM-2016上報告。

圖31.IBM選擇性溝槽外延優化接觸電阻:(a)鍺選擇性外延生長(Ge-SEG),(b)橫截面透射電子顯微鏡(X-TEM),(c)能量色散X射線光譜(EDX)

圖31(a)說明了在接觸開口底部的選擇性Ge"溝槽"外延;圖31(b)顯示了X-TEM暗場圖像,圖31(c)顯示了EDX元素映射,展示了Ge:III族金屬合金。英特爾的Agrawal等人在他們2020年IEDM論文中為納米片pMOS顯示的圖32中,在選擇性SiGe S/D WAC頂部有一個p++帽層,用于低接觸電阻。注意他們展示了尖端(SDE)優化以獲得低延伸電阻。

圖32.英特爾使用p++帽層以獲得低接觸電阻

結論??

自1962年在《自然》雜志上首次發表以來,硅SEG技術現已有61年歷史。用于CMOS S/D應力器的應用已有20年,于2003年隨英特爾90納米節點技術引入。隨著向3D堆疊CMOS器件的遷移,SEG技術用于環繞接觸的預期壽命應該會延長到2030年代的另一個十年。

-

半導體

+關注

關注

335文章

28386瀏覽量

230451 -

工藝

+關注

關注

4文章

657瀏覽量

29187 -

晶體管

+關注

關注

77文章

9912瀏覽量

140251

原文標題:半導體專題|?選擇性外延生長的歷史回顧:從1962年至今

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體發展的四個時代

半導體發展的四個時代

PCB選擇性焊接技術介紹

PCB選擇性焊接技術詳細

PCB選擇性焊接技術詳細

嵌入式源漏選擇性外延(Embedded Source and Drain Selective Epitaxy)

6.1.1 選擇性摻雜技術∈《碳化硅技術基本原理——生長、表征、器件和應用》

SiGe外延工藝及其在外延生長、應變硅應用及GAA結構中的作用

應力消除外延生長裝置及外延生長方法

半導體選擇性外延生長技術的發展歷史

半導體選擇性外延生長技術的發展歷史

評論