邊沿觸發器(Edge Triggered Flip-Flop)是一種數字電路中的基本存儲單元,它能夠存儲一位二進制信息。邊沿觸發器的特點是只有在時鐘信號的上升沿或下降沿到來時才能改變輸出狀態。這種觸發方式可以有效地減少電路的功耗和提高電路的穩定性。邊沿觸發器有多種類型,下面介紹幾種常見的邊沿觸發器類型。

- D觸發器(Data Flip-Flop)

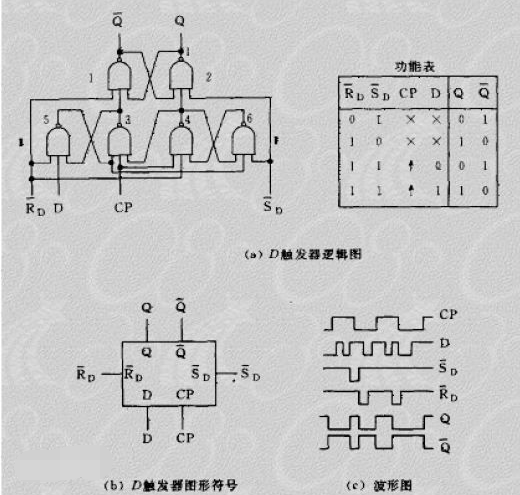

D觸發器是一種最基本的邊沿觸發器,它具有一個數據輸入端(D)、一個時鐘輸入端(CLK)和一個輸出端(Q)。D觸發器的功能是將數據輸入端的二進制信息在時鐘信號的上升沿或下降沿到來時存儲到觸發器中,并在輸出端產生相應的二進制信號。

D觸發器的工作原理如下:

- 當CLK信號為低電平時,無論D輸入端的信號如何變化,Q輸出端的信號保持不變。

- 當CLK信號從低電平跳變到高電平時,Q輸出端的信號將跟隨D輸入端的信號變化。

- 當CLK信號從高電平跳變到低電平時,Q輸出端的信號保持不變。

D觸發器可以用各種邏輯門實現,如與非門、或非門等。D觸發器在數字電路設計中應用廣泛,如寄存器、計數器、移位寄存器等。

- JK觸發器(J-K Flip-Flop)

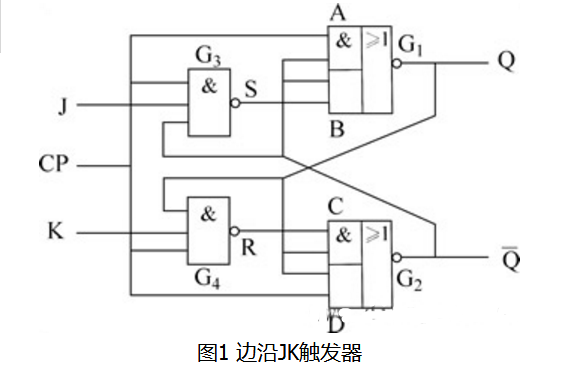

JK觸發器是一種具有兩個輸入端(J和K)的邊沿觸發器。JK觸發器的功能是將J和K輸入端的二進制信息在時鐘信號的上升沿或下降沿到來時進行邏輯運算,并在輸出端產生相應的二進制信號。

JK觸發器的工作原理如下:

- 當CLK信號為低電平時,無論J和K輸入端的信號如何變化,Q輸出端的信號保持不變。

- 當CLK信號從低電平跳變到高電平時,根據J和K輸入端的信號,Q輸出端的信號將按照以下規則變化:

- 如果J=0,K=0,則Q保持不變。

- 如果J=0,K=1,則Q清零。

- 如果J=1,K=0,則Q置位。

- 如果J=1,K=1,則Q取反。

JK觸發器可以用D觸發器實現,也可以使用其他邏輯門實現。JK觸發器在數字電路設計中應用廣泛,如寄存器、計數器、移位寄存器等。

- T觸發器(Toggle Flip-Flop)

T觸發器是一種具有一個輸入端(T)的邊沿觸發器。T觸發器的功能是在時鐘信號的上升沿或下降沿到來時,將輸出端的二進制信號取反。

T觸發器的工作原理如下:

- 當CLK信號為低電平時,無論T輸入端的信號如何變化,Q輸出端的信號保持不變。

- 當CLK信號從低電平跳變到高電平時,Q輸出端的信號將取反。

- 當CLK信號從高電平跳變到低電平時,Q輸出端的信號保持不變。

T觸發器可以用D觸發器和非門實現,也可以使用其他邏輯門實現。T觸發器在數字電路設計中應用廣泛,如寄存器、計數器、移位寄存器等。

- RS觸發器(Set-Reset Flip-Flop)

RS觸發器是一種具有兩個輸入端(S和R)的邊沿觸發器。RS觸發器的功能是將S和R輸入端的二進制信息在時鐘信號的上升沿或下降沿到來時進行邏輯運算,并在輸出端產生相應的二進制信號。

RS觸發器的工作原理如下:

- 當CLK信號為低電平時,無論S和R輸入端的信號如何變化,Q輸出端的信號保持不變。

- 當CLK信號從低電平跳變到高電平時,根據S和R輸入端的信號,Q輸出端的信號將按照以下規則變化:

- 如果S=0,R=0,則Q保持不變。

- 如果S=0,R=1,則Q清零。

- 如果S=1,R=0,則Q置位。

- 如果S=1,R=1,則Q的輸出狀態不確定。

RS觸發器可以用D觸發器和邏輯門實現,也可以使用其他邏輯門實現。RS觸發器在數字電路設計中應用廣泛,如寄存器、計數器、移位寄存器等。

-

存儲單元

+關注

關注

1文章

66瀏覽量

16373 -

數字電路

+關注

關注

193文章

1637瀏覽量

81634 -

時鐘信號

+關注

關注

4文章

466瀏覽量

29100 -

邊沿觸發器

+關注

關注

0文章

34瀏覽量

4140

發布評論請先 登錄

CMOS觸發器在CP邊沿的工作特性研究

邊沿觸發SR觸發器

什么是邊沿觸發器_邊沿D觸發器介紹

常用邊沿觸發器電路結構和工作原理

脈沖和邊沿觸發器區別

邊沿觸發器的類型有哪些

邊沿觸發器的類型有哪些

評論