隨著大數(shù)據(jù)中心、云計(jì)算服務(wù)的不斷增長(zhǎng),對(duì)于系統(tǒng)性能、功能和帶寬的要求也是越來(lái)越高,同時(shí)也驅(qū)動(dòng)通信總線技術(shù)不斷取得新的進(jìn)步。由英特爾提出的第三代高性能I/O總線技術(shù)—PCIE總線解決了PCI總線的不足,它的發(fā)展將取代PCI成為新型的數(shù)據(jù)總線,其提供了更加完善的性能,更多的功能,更強(qiáng)的可擴(kuò)展性和更低的成本。

PCI總線協(xié)議采用的是并行結(jié)構(gòu),也就是說(shuō)總線上所有擴(kuò)展設(shè)備都是共享總線帶寬,而PCIe總線協(xié)議則有所不同,采用的是高速差分總線規(guī)格,并采用端到端的連接方式,即每一條PCIe通信鏈路中只能連接兩臺(tái)設(shè)備,除此之外PCIe還采用了網(wǎng)絡(luò)通信中的一些技術(shù),比如支持多種數(shù)據(jù)路由方式、基于多通路的數(shù)據(jù)傳輸方式以及基于報(bào)文的數(shù)據(jù)傳輸,并且充分考慮并優(yōu)化了數(shù)據(jù)傳輸過(guò)程中的服務(wù)質(zhì)量(QoS,Quality of Service)問(wèn)題。

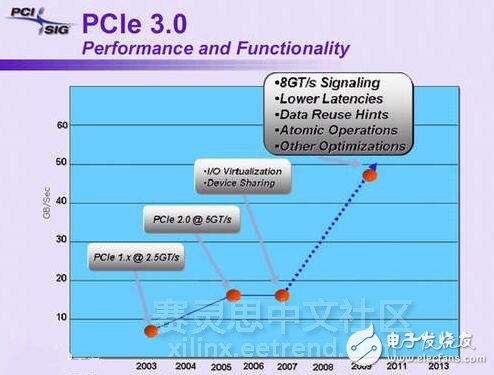

圖1:PCIe高速通信總線標(biāo)準(zhǔn)的發(fā)展歷程

在每個(gè)實(shí)際應(yīng)用中如何最大限度的發(fā)揮PCIe總線的通信速度至關(guān)重要,Xilinx推出了一個(gè)基于高級(jí)FPGA器件和DMA(Direct Memory Access,直接內(nèi)存存取)的參考解決方案:

提升PCIe總線通信速度主要從以下幾方面考慮:

根據(jù)應(yīng)用需求選擇合適的鏈路速度和數(shù)據(jù)帶寬

合理設(shè)定最大有效載荷

通信過(guò)程中最大可能的傳輸數(shù)據(jù)包大小

啟用最大數(shù)量的DMA通道

輪詢操作和中斷操作的選擇(一般輪詢操作效率更高、速度更快)

除此之外我們還要選擇高性能的硬件平臺(tái),Xilinx推出的參考設(shè)計(jì)采用的是KCU105 Kintex UltraScale FPGA開發(fā)套件,它采用的是最高端的Kintex UltraScale All Programmable FPGA器件,具有ASIC級(jí)別的系統(tǒng)性能,集成了時(shí)鐘管理和電源管理等豐富特性,這款開發(fā)套件非常適合中高端類應(yīng)用的系統(tǒng)原型開發(fā),如數(shù)據(jù)中心、無(wú)線通信基礎(chǔ)設(shè)施等。

圖2:Xilinx推出的KCU105 Kintex UltraScale FPGA開發(fā)套件

Xilinx推出的Vivado開發(fā)工具也大大方便了系統(tǒng)的開發(fā),其集成了豐富的IP模塊,如AXI DMA、PCIe Block core等,同時(shí)還提供了IP集成器功能,實(shí)現(xiàn)基于Tcl、圖形化的開發(fā)流程,通過(guò)IP集成器實(shí)現(xiàn)的模塊接口通常采用業(yè)界標(biāo)準(zhǔn)的AXI4接口,支持關(guān)鍵IP接口的智能化自動(dòng)連接,從而不管是在系統(tǒng)設(shè)計(jì)還是在開發(fā)效率上都帶來(lái)了很大提高。

-

通信

+關(guān)注

關(guān)注

18文章

6184瀏覽量

137467 -

PCIe

+關(guān)注

關(guān)注

16文章

1328瀏覽量

84802

發(fā)布評(píng)論請(qǐng)先 登錄

進(jìn)一步提升PCIe總線通信速度的方法

進(jìn)一步提升PCIe總線通信速度的方法

評(píng)論