在FPGA的世界里,設計軟件在整個系統開發過程中發揮著至關重要的作用,它通過先進的功能使端到端編程變得更加容易,從而在充分利用器件功能的同時實現設計的靈活性。

然而,由于基于FPGA的片上系統(SoC)設計是一項多學科的工作,需要硬件架構、嵌入式軟件、系統集成等方面的專業知識,因此非FPGA設計人員或首次使用FPGA的用戶往往需要很高的學習成本。

萊迪思Propel是一款基于圖形用戶界面(GUI)的先進設計環境,旨在通過提供一整套圖形和命令行工具來創建、分析、編譯和調試基于FPGA系統的硬件設計和軟件設計,從而應對以上挑戰。

最新版本的萊迪思Propel(2024.1)進一步簡化了開發周期,改善了軟硬件設計人員的體驗。請繼續閱讀,了解最新更新如何幫助您在幾分鐘內構建基于FPGA的處理器系統。

為開發者賦能的重要工具

最新的萊迪思Propel提供了一個用戶友好的環境,具有拖放IP實例化和“構建即正確”的設計方法,大大增強了易用性。這有助于設計人員快速高效地構建復雜的系統,通過引腳間自動連接、向導式配置和參數化來簡化設計流程,快速集成處理器和外設IP。

Propel還通過圖形和命令行工具提高靈活性,滿足各種技能水平的設計人員的需要。它允許腳本級編輯,以實現細粒度控制和更新現有設計。它還集成了豐富的資源,其強大的IP服務器定期更新,幫助開發人員在快速在基于萊迪思FPGA的設計上實現新的IP。

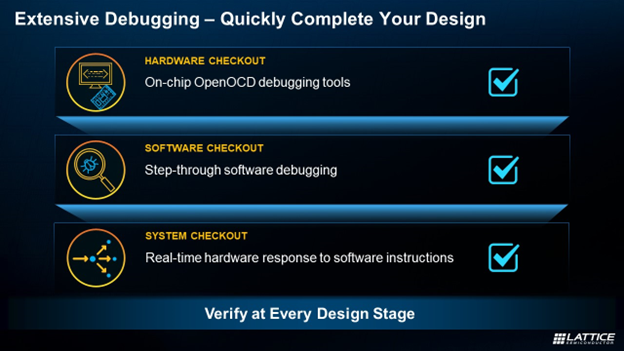

最后,該工具的軟件開發工具包(SDK)提供了一個無縫的軟件開發環境,集成了行業標準的集成開發環境(IDE)和工具鏈、軟件/硬件調試功能、軟件庫和用于Propel定義系統的電路板支持包(BSP)。

這些功能共同構成了一個高效的設計環境,可大大減少嵌入式設計人員的開發時間和復雜性,使他們能夠專注于FPGA處理器系統的創新和優化。

在硬件和軟件環境中提供全方位價值

Propel的最新版本為硬件和軟件設計者帶來了很多價值。它為IP合作伙伴和客戶提供了一個完全腳本化的IP發布和使用流程,為那些包含混合語言設計塊的設計自動生成仿真腳本,從而實現系統驗證的靈活性。

對于嵌入式軟件設計人員,Propel可用于分析其C/C++代碼的性能,并在系統模型上調試代碼,而無需電路板。QuickEMUlator(QEMU)的加入增加了軟件工程師團隊的可擴展性,因為每位工程師都可以在QEMU模型上運行自己的軟件代碼,而無需多個電路板。

Propel全新價值增強功能和特性包括:

★ QuestaSim萊迪思版:在調試功能和提高設計效率方面邁出了一大步。與包含ModelSim的前一版本相比,QuestaSim性能更強,采用了更先進的仿真技術,仿真速度更快,支持多語言開發。該流程是半自動的,Propel為用戶處理了大部分設置工作,用戶可以輕松上手。

★設計創建增強功能(Builder中的SoC和SDK中的C/C++):Propel幫助設計人員在設計流程中快人一步,為各種應用需求提供多種不同的模板。其新的模板創建流程讓用戶更方便辨別哪些模板更容易創建。設計人員可以通過創建跨職能團隊共享的自定義C++項目模板來提高工作效率。

★使用事務控制語言(TCL)實現設計自動化:設計人員可使用Propel自動生成TCL構建腳本,用于從零開始重建設計。這樣,傾向使用預先編寫腳本的僅使用控制臺的用戶就能輕松上手,并繼續使用PropelBuilder進行開發。

★優化設計規則檢查(DRC):PropelBuilder的DRC引擎在此版本中也得到了增強,支持幾種新的設計規則檢查類型。現在它支持幾種新的增強型DRC,用戶能以新的方式開發項目,并在設計流程中更早地發現問題,從而提高易用性。

★顏色定制功能:Propel Builder中的顏色定制功能大大增強,圖形用戶界面中的幾乎所有內容都可以進行顏色定制。組件外觀、組件名稱、組件端口、原理圖背景、圖形用戶界面背景和控制臺文本都支持更多顏色定制。

★支持高速集成電路硬件描述語言(VHDL):設計人員可以開發和導入自己的VHDL代碼,這些代碼可以直接集成到PropelBuilder的SoC設計中。與Verilog類似,Propel 2024.1增強了對VHDL的支持。用VHDL和Verilog編寫的RTL代碼可轉換為膠合邏輯組件,用于系統集成。

簡化FPGA設計流程和仿真

Propel現支持QEMU虛擬平臺,嵌入式設計人員能夠使用Propel和萊迪思的嵌入式設計流程,而無需實際的器件。該流程為用戶處理所有必要的工具鏈和配置設置,幫助他們輕松仿真自己的虛擬RISC-V設計。QEMU是一個多功能虛擬平臺,可為用戶帶來諸多好處,尤其是在軟件開發和測試領域。

FreeRTOS升級:Propel SDK還支持多個新的應用模板,用戶能夠更輕松地使用各種新的設計流程。在這個版本中,我們帶來了兩個新的基于FreeRTOS(實時操作系統)的模板,提供了詳細和簡化示例,演示它如何在用戶的RISC-V系統中運行。此外,我們還支持一個新的時序分析模板,向用戶演示如何使用gprof生成性能數據。

憑借萊迪思Propel的強大功能,FPGA開發人員可以在其應用和系統開發中快速、高效地探索全新可能。無論您是經驗豐富的工程師還是剛剛入門,Propel直觀的界面和全面的功能將助您快速取得設計成功,從簡單的應用到復雜的嵌入式控制和數據處理系統。

-

處理器

+關注

關注

68文章

19671瀏覽量

232630 -

FPGA

+關注

關注

1640文章

21899瀏覽量

611353 -

萊迪思

+關注

關注

2文章

230瀏覽量

39291 -

Propel

+關注

關注

0文章

3瀏覽量

270

原文標題:利用萊迪思Propel賦能基于FPGA的處理器設計

文章出處:【微信號:Latticesemi,微信公眾號:Latticesemi】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

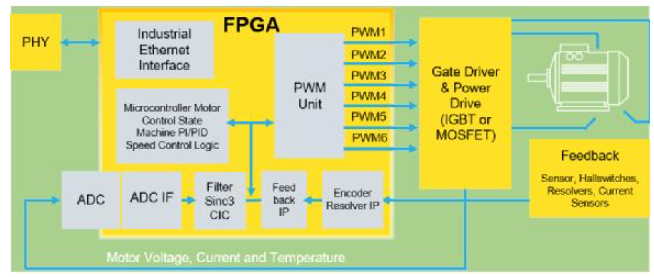

使用萊迪思Automate解決方案集合實現具有預測性維護功能的電機控制

簡單了解萊迪思Propel的強大功能

簡單了解萊迪思Propel的強大功能

評論