聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

封裝

+關注

關注

128文章

8598瀏覽量

144990 -

封裝技術

+關注

關注

12文章

576瀏覽量

68486 -

芯片堆疊

+關注

關注

0文章

19瀏覽量

14707

發(fā)布評論請先 登錄

相關推薦

熱點推薦

芯片封裝測試流程詳解ppt

;?引腳數(shù)。引腳數(shù)越多,越高級,但是工藝難度也相應增加;其中,CSP由于采用了FlipChip技術和裸片封裝,達到了 芯片面積/封裝面積=1:1,為目前最高級的

發(fā)表于 01-13 11:46

汽車電子EMC測試案例分享(52頁PPT)

本帖最后由 Hongliang_sz 于 2015-8-24 11:31 編輯

52頁PPT 汽車電子EMC測試案例分享

發(fā)表于 08-17 16:41

電磁干擾抑制的屏蔽技術(63頁PPT干貨)

`電磁干擾抑制的屏蔽技術(63頁PPT)[hide][/hide]相關課程:http://t.elecfans.com/topic/45.html`

發(fā)表于 08-25 11:27

電磁兼容設計技術講義 經典(203頁PPT)

`相關推薦:http://t.elecfans.com/topic/45.html?elecfans_trackid=bbs_toptxt電磁兼容設計技術講義 經典(203頁PPT)部分文件需要回復后下載[hide][/hide

發(fā)表于 09-01 11:09

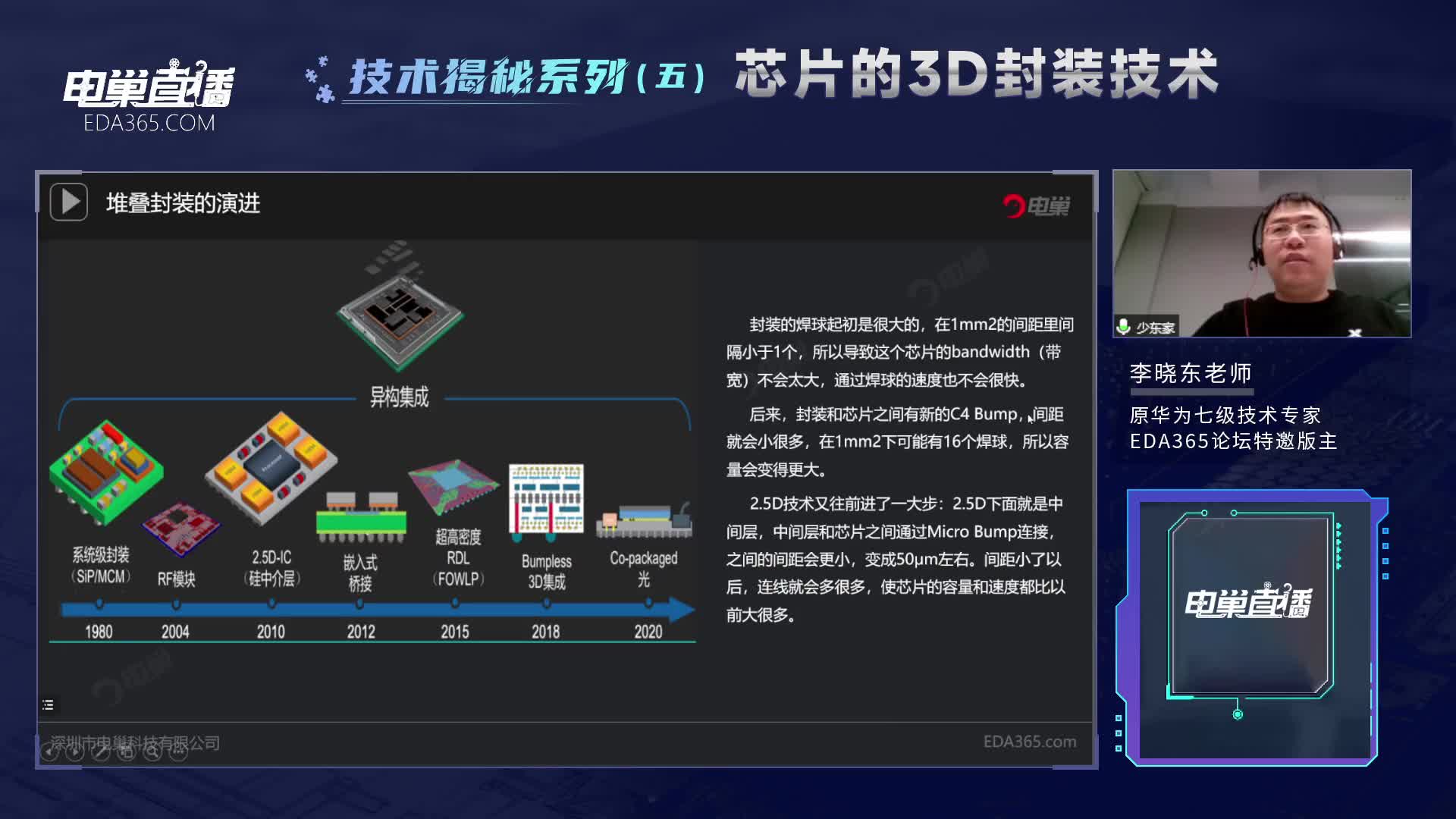

芯片堆疊技術在系統(tǒng)級封裝SiP中的應用存?

為什么芯片可以進行堆疊呢?這里面我們講的主要是未經過封裝的裸芯片。曾經有用戶問我,封裝好的芯片可

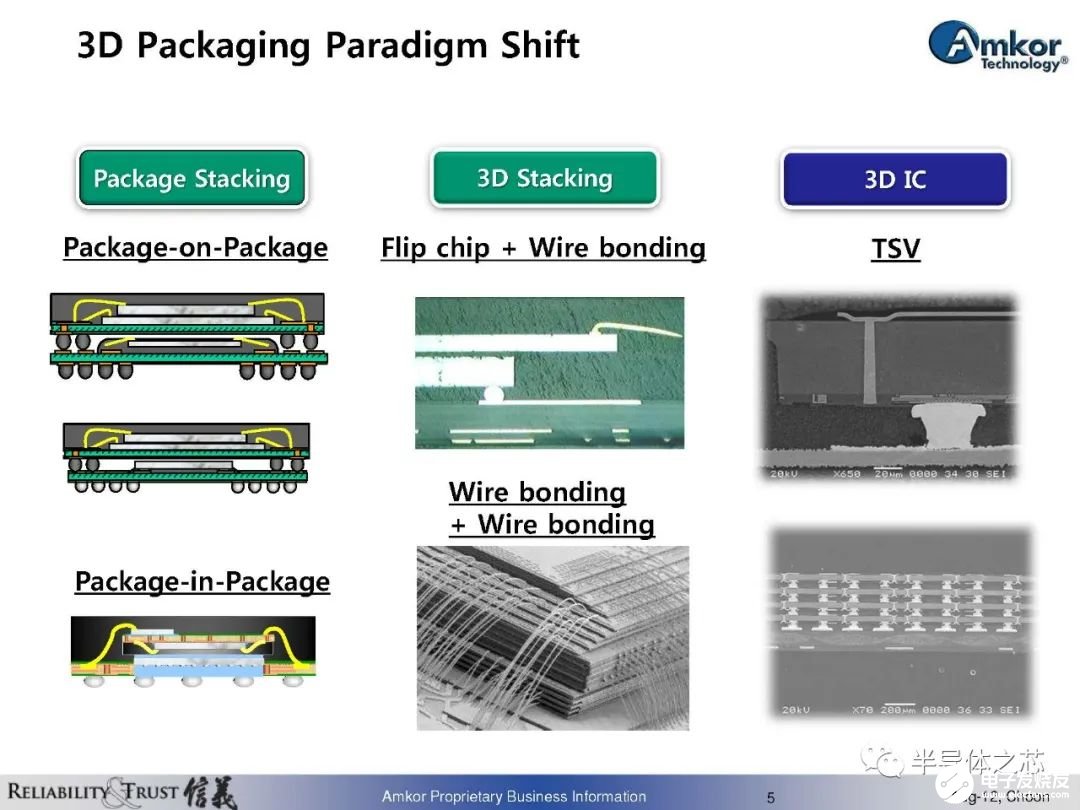

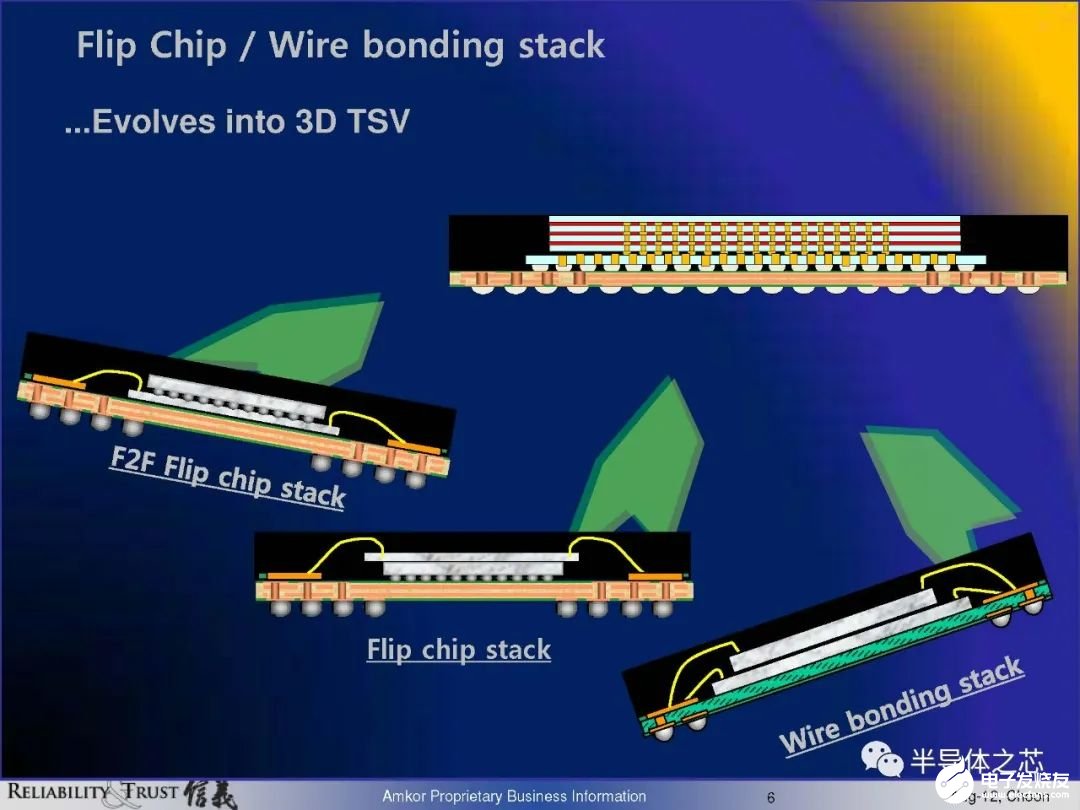

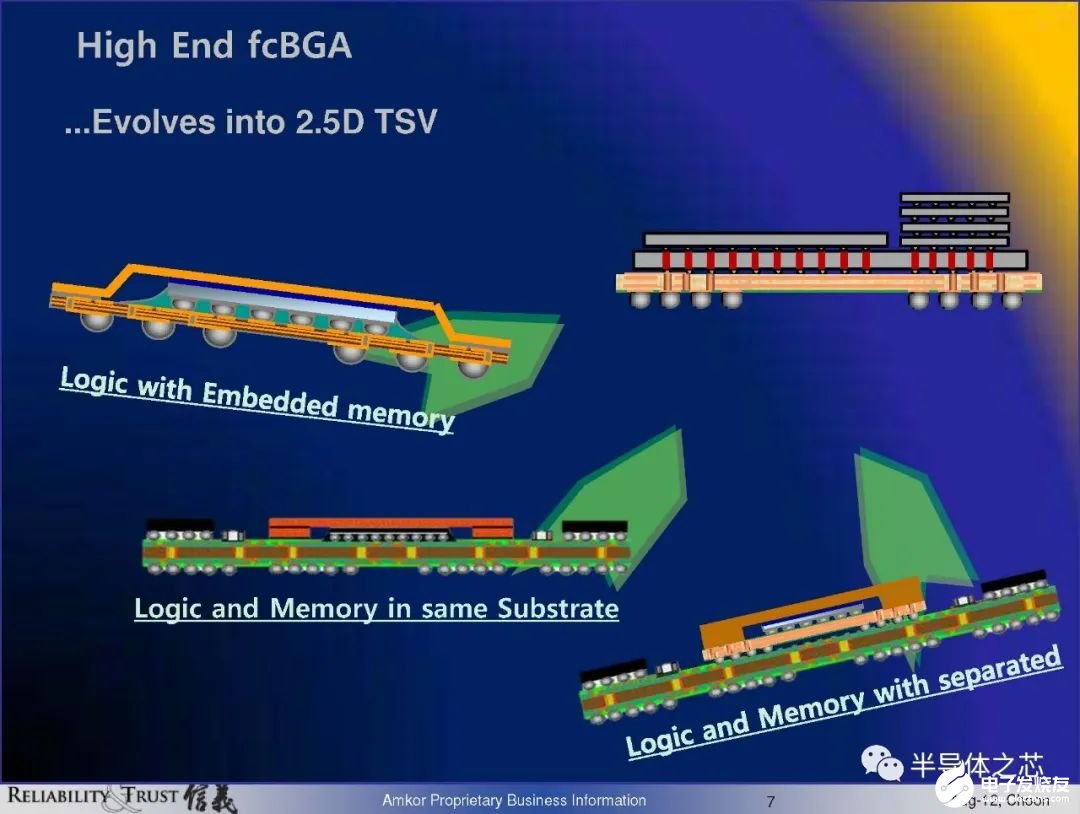

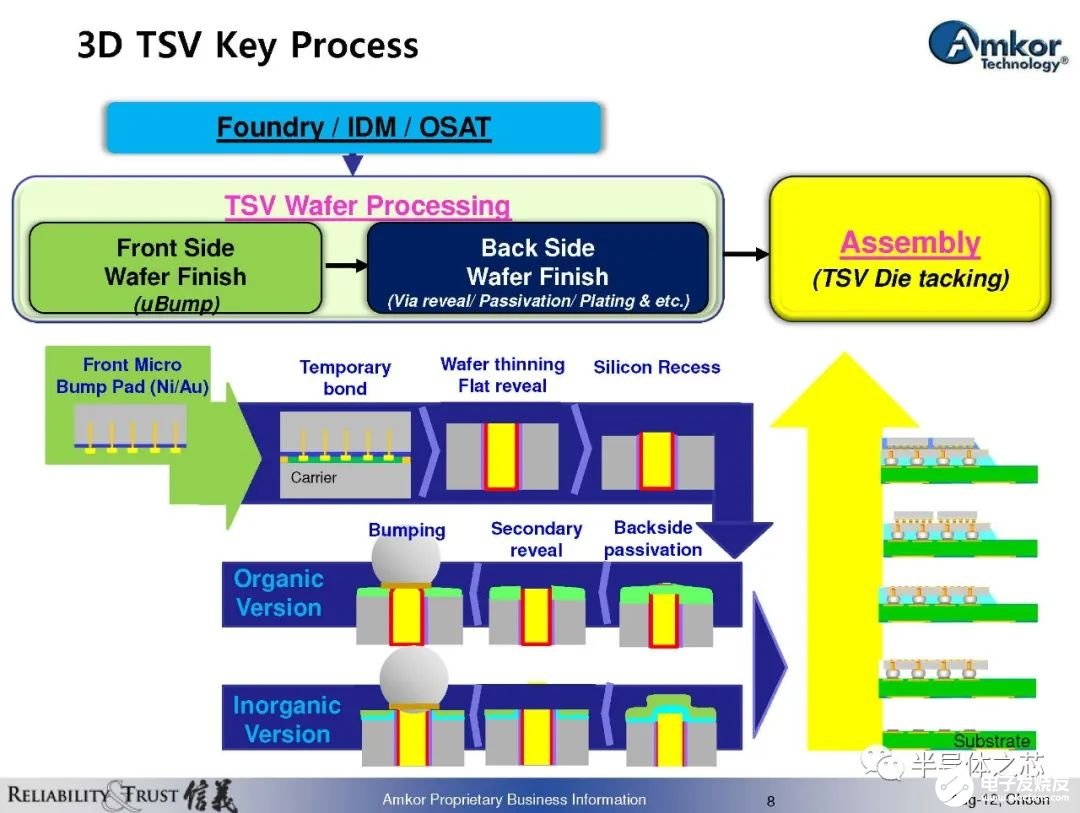

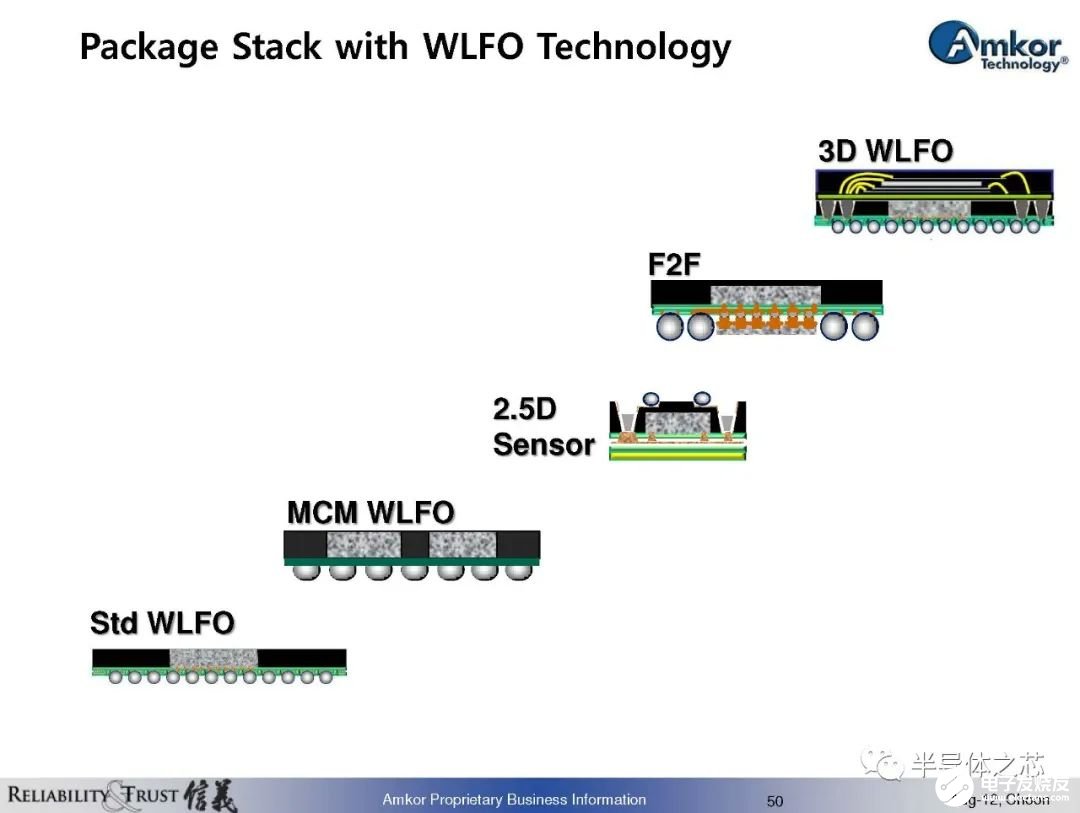

芯片堆疊封裝技術實用教程(52頁PPT)

芯片堆疊封裝技術實用教程(52頁PPT)

評論