在高性能模擬集成電路,諸如開關電容濾波器、∑-△調制器和流水線A/D轉換器中,常常需要高直流增益、高單位增益帶寬的運放來同時滿足系統對精度與速度的要求。高增益要求運放采用多級、長溝道器件,小的工作電流;而高速則要求運放采用單級、短溝道器件,大的工作電流。增益增強技術的提出解決了這對矛盾,提高了運放的直流增益而又不影響其高頻性能。然而,零極點對(doublet)的存在會影響運放的建立特性[1,2]。通常,消除doublet影響的方法是提高其發生的頻率,但若過高的doublet發生頻率將導致系統的不穩定[3,4]。

1 運放的設計和優化

1.1 運放的結構選擇

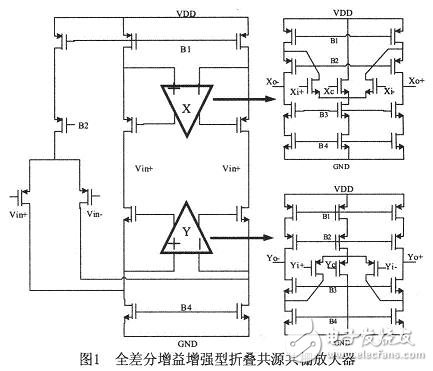

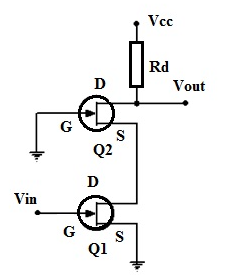

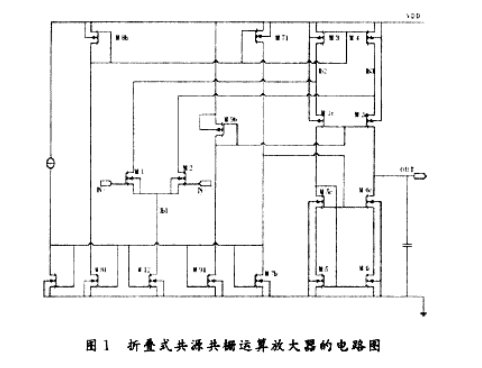

目前流行的運算跨導放大器(OTA)結構中,套筒結構有最好的性能,但輸出擺幅受限,不適合用于低壓設計。折疊共源共柵結構有更大的輸出擺幅以及可以使輸入和輸出短接,共模輸入電平更容易選取,所以得到了廣泛的應用。本運放采用折疊共源共柵結構,總電路如圖1所示。(參見右欄)輸入管選用PMOS管,因為PMOS管的載流子遷移率低,所以要獲得相同的速度和增益,需要更大的電流和更大的尺寸,但因為它的折疊點在NMOS處而NMOS的尺寸要小于流過相同電流的PMOS的尺寸,所以折疊點的寄生電容比較小,折疊點帶來的極點高,有較好的頻率特性。另一方面,PMOS輸入管優化了1/f噪聲。

1.2 建立時間分析及優化

采用共源共柵結構的增益增強技術提高了直流增益,卻沒有顯著影響高頻性能,然而由于零級點對的存在,影響了運放的瞬態建立特性。下面主要分析運放建立特性,來優化建立時間。

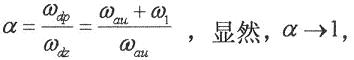

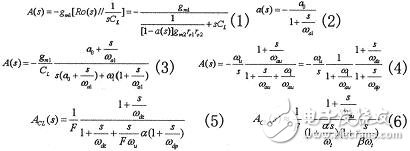

首先,應考察輔助運放引起偶對的原因。在忽略寄生電容作用的條件下,單極點性質的增強型運算跨導放大器(GBCA)增益傳遞函數為式(1),若輔助運放采用式(2)的單極點模型近似,a0》1,得到式(3),代入ωau=a0ωa1的條件,在ω》ωa1的頻率范圍下,開環增益為式(4),由內部反饋環路形成的一對偶對分別為ωdz=ωau,ωdp=ωau+ω1。以偶對中數值較小的零點ωdz為參照,偶對的分離系數α為

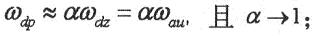

該零點的分離度與輔助運放的單位增益帶寬和主運放的主極點頻率密切相關。在以上簡單近似條件下,由于ωau與ω1無關,則當單調增加輔助運放帶寬使ω》ωa1時,形成的偶對相互間越來越靠近,對系統相位的影響可以忽略,而對瞬態特性的影響必須以閉環系統進行分析。對于F反饋系數及以上開環系統構成的閉環系統,開環系統的偶對將變成閉環系統的偶對。在ω》ωa1的頻率范圍下,有式(5),設閉環系統在主次極點分離條件下的主極點頻率為ωi=Fωu。考慮到 偶對中極點ωdp相對ωt的位置由比值系數

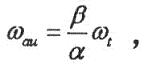

偶對中極點ωdp相對ωt的位置由比值系數 決定,即主要由ωau與ωu的位置關系所決定,

決定,即主要由ωau與ωu的位置關系所決定, 則有式(6)。

則有式(6)。

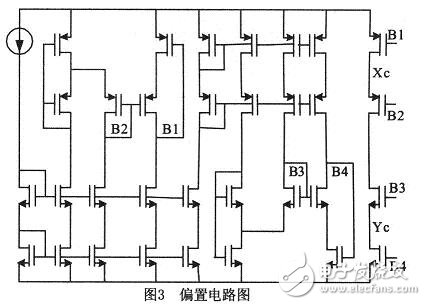

階躍響應可通過拉氏反變換得到:

瞬態特性的理論分析表明,閉環偶對的相對位置關系近似保持原有開環下的性質不變。在高頻極點的影響下,閉環主極點帶寬下降為ωt/α。根據以上的分析結果,得到GBCA電路設計步驟如下:

1)設計主運放。增益帶寬積由建立時間要求確定,相位裕度高于70度;

2)找出主運放的共源共柵(cascode)管的柵電容,作為輔助運放的負載電容;

3)設計輔助運放。增益帶寬積(GBW)略大于主運放的GBW,相位裕度高于80度。

1.3 共模反饋與偏置

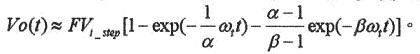

共模反饋電路是全差分運放的一個不可或缺的部分。本文的主運放選用動態開關電容共模反饋,如圖2所示。選用這種結構的原因,一方面是這種共模反饋電路可節省功耗;另一方面是其共模電壓取樣電路不會限制運放的輸出擺幅。盡管其具有上述優點,但它不適合兩個輔助運放。因為兩個輔助運放的輸出負載是主運放中共源共柵管的柵電容,它們都較小。若采用開關電容共模反饋,共模反饋電路的電容勢必更小,致使開關的電荷注入效應影響到電路的精度。此外,兩個輔助運放也是全差分的,也需要共模反饋。由于輔助運放不需要大的輸出擺幅,而且輔助運放nbooster和pbooster是接成跟隨器的形式,所以穩定了輸入共模也就穩定了輸出共模。

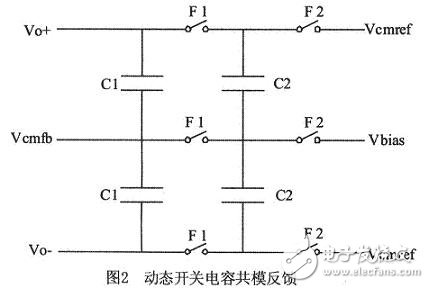

該運算放大器的主放大器和增益增強放大器使用了同一個偏置電路,偏置電路中采用了高擺幅的共源共柵電流源,如圖3所示。

2 仿真結果

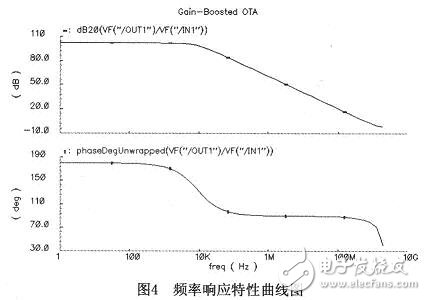

按照12位100MHz采樣頻率流水線A/D轉換器的采樣保持電路的指標來設計這個運算放大器。對動態誤差和靜態誤差所各自需要的增益和單位增益帶寬進行了折衷,將0.002%分配給靜態誤差,余下的0.008%給動態誤差。電路采用中芯國際(SMIC)0.18 μm混合信號CMOS工藝設計,1.8V電壓供電。具體設計指標為:開環增益:102dB:建立時間:4.3ns;精度:0.01%;單位增益帶寬:1.27GHz。頻率響應的曲線如圖4所示。

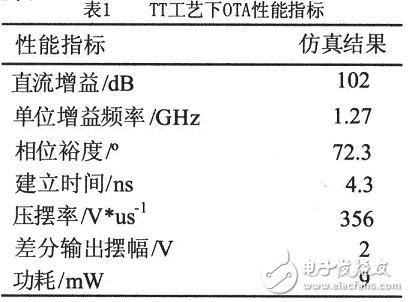

對運算放大器一些重要的性能參數在TT下仿真,結果的歸納見表1。

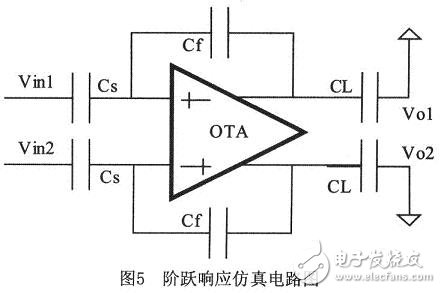

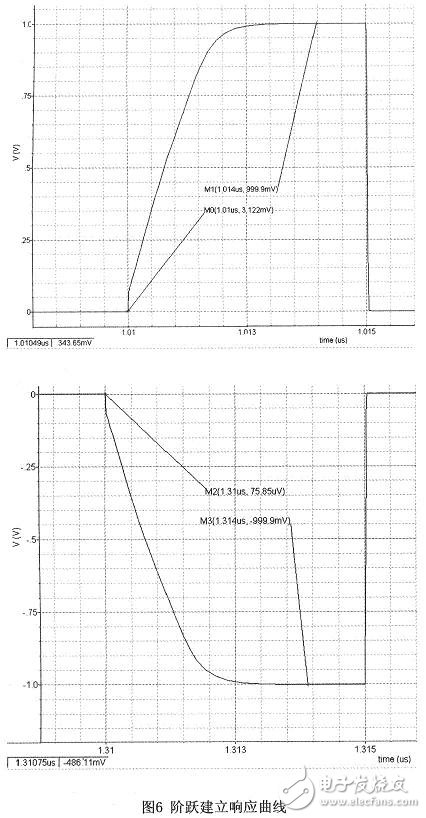

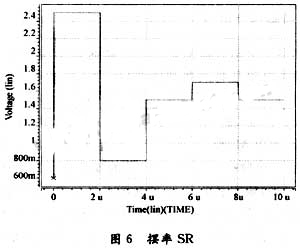

對階躍輸入響應的仿真在如圖5所示的閉環中進行。從運算放大器的輸入端引入一個±1V的大階躍信號,對應的建立時間曲線如圖6所示,表明所設計的電路能夠在4.3ns內達到終態0.01%的精度。

3 結論

本文提出了一種可用于增益增強運放高速設計的優化方法,并采用SMIC 0.18 μm混合信號CMOS工藝設計,實現了一個單級全差分增益增強的折疊共源共柵運算放大器。詳細分析并克服了零極點對可能引起的慢動態性能。仿真結果表明,此運算放大器能夠滿足高性能流水線A/D轉換器設計的要求。

-

放大器

+關注

關注

145文章

14121瀏覽量

216693 -

電容

+關注

關注

100文章

6242瀏覽量

153695 -

濾波器

+關注

關注

162文章

8116瀏覽量

181510 -

調制器

+關注

關注

3文章

897瀏覽量

46246

發布評論請先 登錄

能增益增強運放高速的折疊共源共柵運算放大器設計

能增益增強運放高速的折疊共源共柵運算放大器設計

評論