上次介紹了sdc的基本概念,那接下來幾期,我們來講解一些比較常用的sdc命令。雖然sdc大大小小有上百條命令,但實際常用的其實就那么10幾條。今天我們來介紹下與時鐘相關的命令。主要有以下命令:

create_clock

create_generated_clock

set_clock_uncertainty

set_clock_groups

任何sdc首先定義的都是時鐘,對于一個同步電路而言,緩存器和緩存器之間的路徑延遲時間必須小于一個Clock 周期(Period),也就是說,當我們確認了Clock 規格,所有緩存器間的路徑的Timing Constraint 就會自動給定了。Clock規格主要包含Waveform、Uncertainty和Clock group的定義。我們把它們稱為時鐘的三要素,當然創建任何時鐘都要檢查一下這三者有沒有正確定義。

create_clock

主要定義一個Clock的source源端、周期、占空比(時鐘高電平與周期的比例)及信號上升沿及下降沿的時間點。

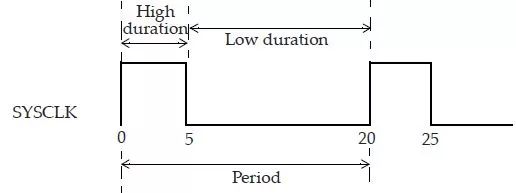

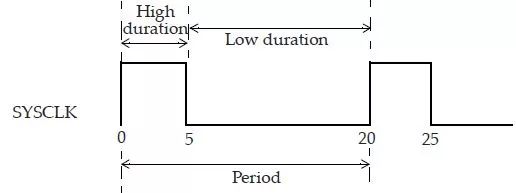

來看一個最簡單的例子:

這個時鐘描述成sdc語句就是:

create_clock -name SYSCLK -period 20 \

-waveform {0 5} [get_ports2 SCLK]

waveform后面跟上升沿和下降沿的時間

-waveform {time_rise time_falltime_rise time_fall ...}

如果沒指定-period,默認的waveform為{0, period/2}

create_generated_clock

generated clocks是另外一個重要的時鐘概念

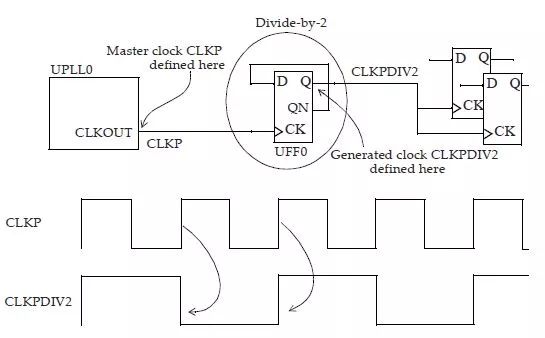

generated clocks 是從master clock中取得的時鐘定義。master clock就是指create_clock命令指定的時鐘產生點,如圖所示:

我們可以用如下命令來描述generated clocks:

#定義master clock

create_clock -name CLKP -period 10 \

-waveform {0 5} [get_pins UPLL0/CLKOUT]

#在Q點定義generated clock

create_generated_clock -name CLKPDIV2 \

-source UPLL0/CLKOUT \

-master_clockCLKP -divide_by 2 [get_pins UFF0/Q]

一般我們把時鐘的源頭會定義成create_clock,而分頻時鐘則會定義為create_generated_clock. 兩者的主要區別在于CTS步驟,generated clock并不會產生新的clock domain, 而且定義generated clock后,clock path的起點始終位于master clock, 這樣source latency并不會重新的計算。這是定義generated clock的優點所在。

Virtual clock

這邊還有一個經常用的概念就是Virtual Clock,虛擬時鐘。

前面介紹的create_clock,create_generated_clock都是real clock。而virtual clock則不掛在任何port或者pin上,只是虛擬創建出來的時鐘。如下所示:

#定義虛擬時鐘

create_clock -name VCLK -period 10 -waveform {0 5}

我們通常會把input/output delay掛在virtual clock上,因為input/output delay約束本來就是指片外的時鐘,所以掛在虛擬時鐘上較為合理。當然如果要省事情,直接掛在real clock上也是可以的。

set_clock_uncertainty

主要定義了Clock信號到時序器件的Clock端可能早到或晚到的時間。主要是用來降低jitter對有效時鐘周期的影響。值得注意的是,在setup check中,clock uncertainty是代表著降低了時鐘的有效周期;而在hold check中,clock uncertainty是代表著hold check所需要滿足的額外margin。

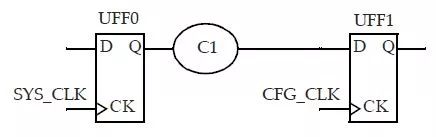

來看下面一條reg2reg path. 對照著如下時鐘波形圖。可以寫出下面的約束。

set_clock_uncertainty-from VIRTUAL_SYS_CLK \

-to SYS_CLK -hold 0.05set_clock_uncertainty -from VIRTUAL_SYS_CLK \

-to SYS_CLK -setup 0.3set_clock_uncertainty -from SYS_CLK \

-to CFG_CLK -hold 0.05set_clock_uncertainty -from SYS_CLK \

-to CFG_CLK -setup 0.1

set_clock_groups

定義完時鐘后,我們也需要通過設置clock group來確認各個時鐘之間的關系。這是很重要的一步,因為通常我們還需要做cross domain check,如果clock group設錯了,會導致整個STA檢查錯誤。一般有三個選項:asynchronous,physically_exclusive和logically_exclusive。

asynchronous代表兩個異步的clock group

physically_exclusive代表兩個clock group在物理意義上相互排斥,比如在一個source pin上定義了兩個時鐘。

logically_exclusive代表兩個clock group在邏輯上相互排斥,比如兩個clock經過MUX選擇器。一個簡單的例子:

set_clock_groups -physically_exclusive \

-group {CLK1 CLK2}-group {CLK3 CLK4}

clock group的定義異常謹慎,需要和前端再三確認。

時鐘的定義就到此為止了,只是一些基礎的概念,具體命令還有很多延伸擴展的內容,大家要去翻doc,深入研究下!

-

時鐘

+關注

關注

11文章

1884瀏覽量

132855 -

SDC

+關注

關注

0文章

49瀏覽量

15818

原文標題:時序分析基本概念介紹——時鐘sdc

文章出處:【微信號:IC_Physical_Design,微信公眾號:數字后端IC芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

MCU時鐘相關功能引腳操作

MSP430G2231單片機,求助其時鐘相關問題,在線等!!!

總結RTC(Real Time Clock)實時時鐘相關的知識

HbirdV2-SoC中如何配置QSPI1和QSPI2的時鐘極性CPOL和時鐘相位CPHA?

與時鐘相關的PCB的設計考慮主要分為兩部分

FPGA中的時鐘相關概念

STM32F030_RTC實時時鐘相關的知識資料下載

MCU時鐘相關功能引腳作用介紹

SPI時鐘極性和時鐘相位

詳細介紹下與時鐘相關的命令

詳細介紹下與時鐘相關的命令

評論