作者:張景濤

問題起源

這個問題來源于華為海思鯤鵬處理器首席架構師兼昇騰AI處理器架構師夏晶在知乎上發出的靈魂之問。

問題初答

在眾多回復中,李博杰同學的回答被認為質量最高。他首先將緩存一致性分為兩個主要場景:一是主機內CPU與設備間的一致性;二是跨主機的一致性。

對于第一個場景(主機內CPU與設備間),李博杰同學明確指出緩存一致性的重要性,并以在微軟研究院實習期間的一個項目為例,說明了使用FPGA將內存連接到PCIe的bar空間上,導致Linux系統啟動時間從3秒延長到30分鐘,速度降低了600倍。這一現象揭示了PCIe不支持緩存一致性,CPU直接訪問設備內存時只能是非緩存型(uncacheable)的。[注:在分析耗時時,除了緩存一致性外,還應考慮PCIe與內存帶寬的差異]

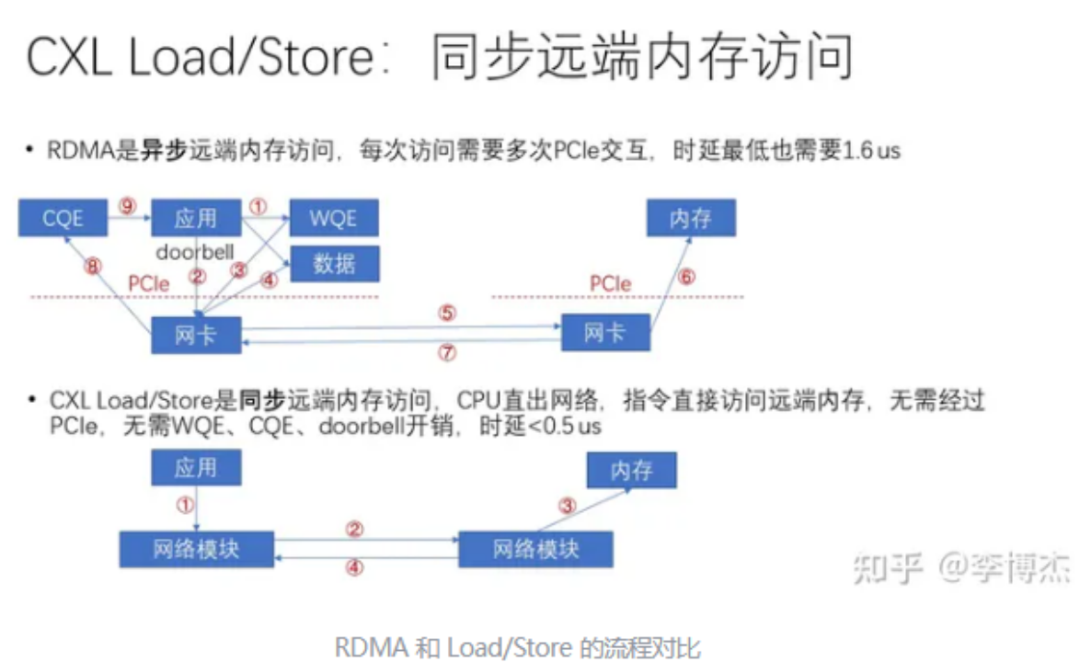

在第一種場景中,他還對比了同步和異步遠程訪問的差異,但原文并未明確指出主機內CPU和設備間一致性的具體優勢。

對于第二個場景(跨主機),跨主機的緩存一致性(CC)存在較大爭議。一方面,大規模分布式一致性的實現難度大,是學術界長期未解的問題。另一方面,許多人對應用場景的理解并不清晰。

例如,在內存池化方面,許多人認為可以利用其他機器的空閑內存來提高集群的內存利用率,這種情況下不需要跨主機的CC,僅需Load/Store操作和主機內的CC。因為借用的內存僅由一臺機器使用,出借方和其他機器均無需訪問。

理想情況下,內存池化可以由多臺機器共享內存,并支持跨主機的CC。這將帶來諸多好處,如簡化編程、減少數據拷貝、提高內存利用率。然而,現實中如何存儲龐大的共享者列表(sharer list)?如何降低緩存失效(Cache invalidation)的高開銷?盡管原文中提出了一些可行方案,例如擴大緩存粒度、將共享列表數據結構改為鏈表或分布式存儲、控制共享者數量,甚至使用租約概念替代共享者列表,但最有效的方法還是與業務結合,因為業務最清楚同步時機和共享數據的使用情況。

最后,李博杰同學指出,跨主機的CC主要應用于Web服務、大數據、存儲等領域。目前,他尚未想到在AI和高性能計算(HPC)領域中的應用,因為AI和HPC通常采用集合通信(collective operations),embedding也有邏輯上中心化的參數服務器(parameter server)來存儲,對多機共享內存數據的需求似乎不大。

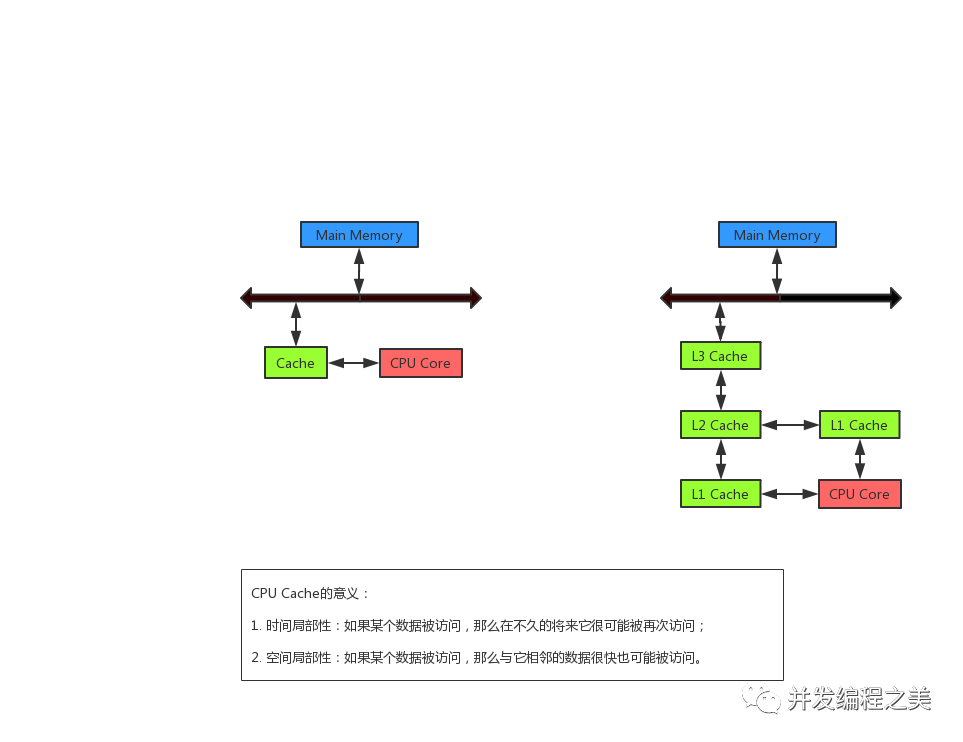

深入思考

針對夏晶老師的問題,筆者在實際工作中也有類似的疑問。在異構計算場景下(尤其是主機內CPU與設備之間),緩存一致性究竟能帶來多大的價值?盡管使用CXL等聲稱支持緩存一致性的總線可以將數據訪問延遲從PCIe的約500納秒降低到50納秒,實現了數量級的優化,但在仔細分析延遲后可以得出明確結論:直接的延遲優化主要是由于協議各層的優化帶來的,而緩存一致性對延遲的優化效果缺乏量化數據支持。直到看到論文《CC-NIC: a Cache-Coherent Interface to the NIC》,許多疑問才得以解答。

在這篇論文中,作者利用X86 CPU UPI接口提供的緩存一致性實現了一個NIC設備,從而驗證了緩存一致性對網卡的具體影響。

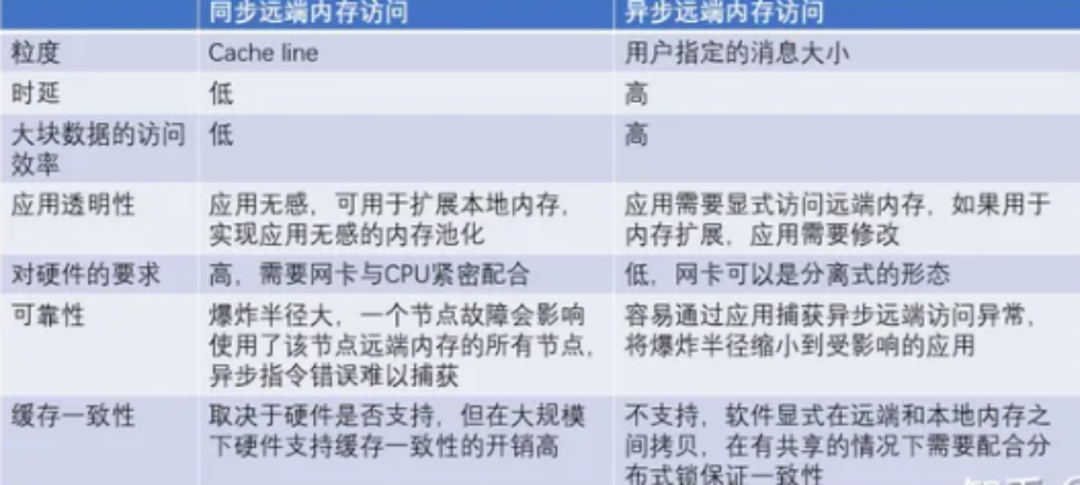

傳統的PCIE接口設備

PCIe接口為設備與主機之間提供了一種非對稱的通信方式。圖1a展示了兩種傳輸機制:MMIO和DMA,分別由主機和設備發起。主機對NIC的讀寫操作通過內存映射輸入/輸出(MMIO)實現。設備將內存區域映射到主機的地址空間,這些區域被設置為不可緩存(UC)或寫組合(WC)內存類型。這樣,主機可以對設備執行加載和存儲操作,這些操作通過PCIe讀寫事務來執行。然而,UC和WC內存類型并不保證緩存一致性或在緩存層次結構中的操作。因此,CPU必須通過PCIe往返行程來加載數據,導致較高的訪問延遲。在ICX CPU平臺上,針對Intel E810 NIC的測試顯示,中位數的MMIO讀延遲分別為982納秒(對于8字節數據)和1026納秒(對于64字節AVX512數據)。而PCIe設備則通過直接內存訪問(DMA)來讀取和寫入主機內存。DMA操作的緩沖區大小通常比64B的MMIO寫組合緩沖區要大得多(例如,4KB),并且通常訪問標準寫回主機內存。盡管傳統PCIe NIC不公開DMA延遲的統計數據,但預計其往返延遲與MMIO相當,大約在1微秒左右。

PCIe的特性和性能對主機-NIC接口的性能提出了挑戰。具體來說,存在以下三個問題:首先,由于PCIe不是一致性互連,因此必須通過顯式的PCIe事務來通信或更新本地數據結構。其次,PCIe操作的高延遲意味著減少互連遍歷的次數對于實現低延遲的數據包傳輸至關重要。最后,通過PCIe進行的數據和元數據寫入對CPU來說在吞吐量和高延遲停頓方面代價高昂。這些問題共同定義了PCIe接口的性能權衡。理想的設計目標是實現高數據包吞吐量、低延遲和高CPU效率,但PCIe的限制使得我們無法同時達到這三個目標。

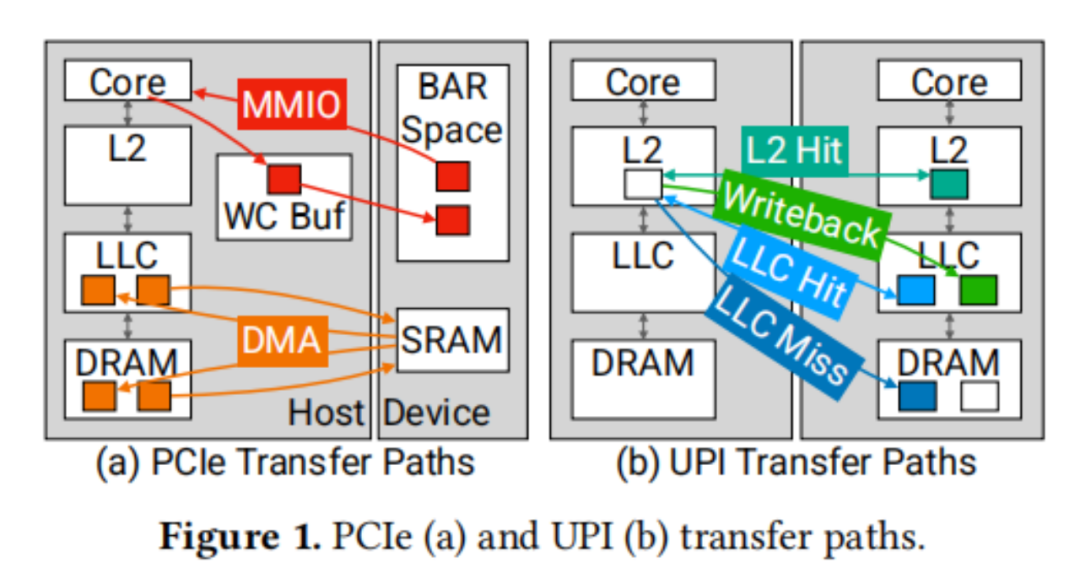

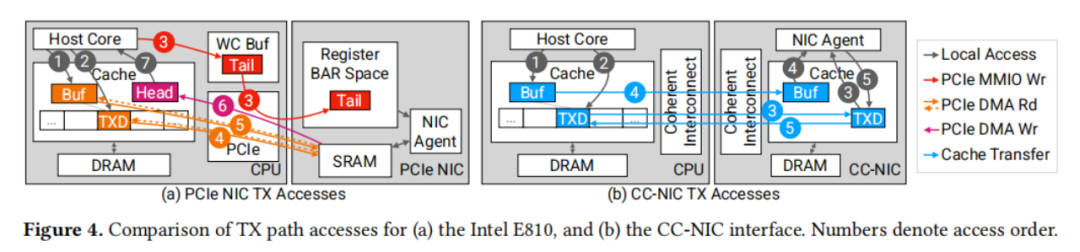

當前的PCIe NIC設計通常優先考慮CPU效率和吞吐量,而犧牲一定的延遲。數據結構通常位于主機本地,并通過顯式的PCIe事務來通知更新。主機在本地內存中維護數據包緩沖區和描述符環,以減少對數據結構訪問和更新的CPU開銷。在傳輸過程中,主機將TX數據包和TX描述符寫入本地內存,并通過MMIO寫入設備端維護的隊列尾部寄存器。這種設計帶來了一種權衡:在MMIO上最小化數據傳輸,但代價是增加了對主機內存中描述符和數據包的額外互連往返讀取。

支持緩存一致性接口

一致性互連技術,如UPI(Universal Platform Interface)和CXL(Compute Express Link),與CPU的內存數據路徑緊密集成,提供了與PCIe根本不同的接口特性。如圖1b所示,跨互連的訪問可以針對DRAM和緩存進行。一致性協議管理著共享緩存的狀態,確保在訪問內存時,數據能夠傳輸到本地緩存。這些協議要求寫入者在寫入之前獲得緩存行的獨占控制權,并使任何遠程緩存中的副本失效。同時,它們也允許多個緩存共享對同一行的讀取訪問,并能夠在緩存之間轉發數據。總的來說,一致性互連提供了一種新的信號和數據結構共享形式,不受PCIe讀寫接口的限制。

與PCIe的非對稱接口不同,一致性互連提供了一個對稱的接口,消除了MMIO和DMA操作之間的權衡。然而,跨互連的傳輸性能受到緩存的存在和一致性狀態的影響,這在延遲、內存控制器請求、協議元數據的開銷以及往返時間方面都有所體現。在一致性互連的上下文中,對緩存行狀態和緩存行為的控制手段有限,這為實現NIC數據結構帶來了機遇和挑戰。

文章指出了實現一致性互連NIC(CC-NIC)時需要考慮的三個設計因素:

1、一致性接口信令和共享數據結構:PCIe NIC通常使用MMIO機制來處理數據和元數據的DMA傳輸以及TX通知。這導致了在接收信號后,通過DMA檢索TX元數據時需要多進行一輪互連往返。而緩存一致性通過硬件執行通知:當遠程端執行寫入操作時,一致性協議會自動使任何本地緩存的副本失效,并在隨后的訪問中獲取新值。此外,一致性互連還允許在主機和NIC之間使用共享數據結構,從而實現共享緩沖池的管理。

2、數據傳輸機制和定位選擇:一致性互連提供了多種數據傳輸機制。CC-NIC可以選擇將寫回內存作為目標,除了緩存繞過數據路徑,還可以將數據結構定位在主機或NIC上,為CC-NIC提供了多種傳輸選項。跨互連的數據傳輸和緩存狀態轉換還取決于對象的當前緩存駐留情況、可能的預取以及由先前訪問引起的緩存狀態。因此,小型對象(如信號和描述符元數據)對布局非常敏感。

3、緩存管理:一致性協議在互連上交換緩存行的所有權。因此,遠程訪問可能導致在后續的本地訪問時需要進行額外的通信。這對于生產者-消費者工作負載尤其成問題。例如,在典型的TX路徑中,元數據和數據從主機傳輸到NIC,隨后NIC執行數據傳輸,而數據不再被NIC需要。在一致性互連的上下文中,保留數據包緩沖區或描述符在NIC端的緩存中是沒有幫助的;它為隨后的主機訪問增加了開銷,因為這些訪問將不得不執行遠程緩存使失效操作。這表明,為了最小化開銷,需要選擇性地使緩存數據失效,這在典型的x86平臺上是不受支持的,或者需要重新設計數據結構以避免這種訪問模式。

CC-NIC設計

利用緩存一致性減少軟件開銷

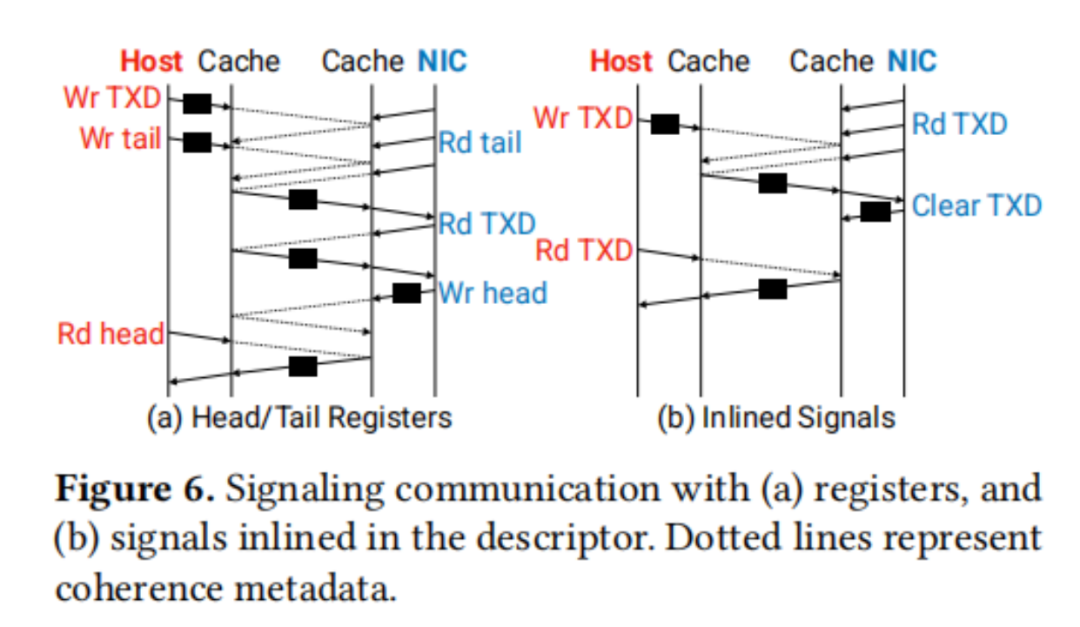

緩存一致性互連提供了一種底層硬件機制,它通過緩存狀態的轉換來傳輸數據并信令新數據的可用性。這種方法避免了傳統基于軟件的信令方式,即通過頭部和尾部索引寄存器進行信令。在一致性緩存互連網絡(CC-NIC)中,采用了描述符內聯信號的方法,通過一個標志來指示描述符是否已經準備好供消費或處于空閑狀態。

將信號與描述符集成在一起的設計,消除了對每個信號單獨進行緩存行傳輸的需要,從而節省了跨socket緩存行訪問的延遲,如圖6所示。在傳輸過程中,NIC不再需要輪詢包含隊列尾部索引的寄存器,而是直接輪詢環中的下一個描述符。描述符的元數據中包含了一個就緒標志,主機在寫入描述符的其他字段后會設置這個標志。一旦這個標志被設置,NIC就能夠在同一訪問中接收到信號和描述符的內容,實現了事件驅動的處理方式。

為了進一步優化信令通信,一個一致性的NIC專用集成電路(ASIC)可以直接處理一致性協議消息。在這種設計中,設備不是通過緩存輪詢抽象來訪問描述符,而是直接響應通過互連接收到的snoop消息。將一致性消息作為信號進行處理,避免了在存在大量隊列計數時,基于軟件的輪詢所面臨的可擴展性限制。這種設計不僅提高了效率,還增強了系統的擴展性和性能。

元數據傳輸的理想數據路徑

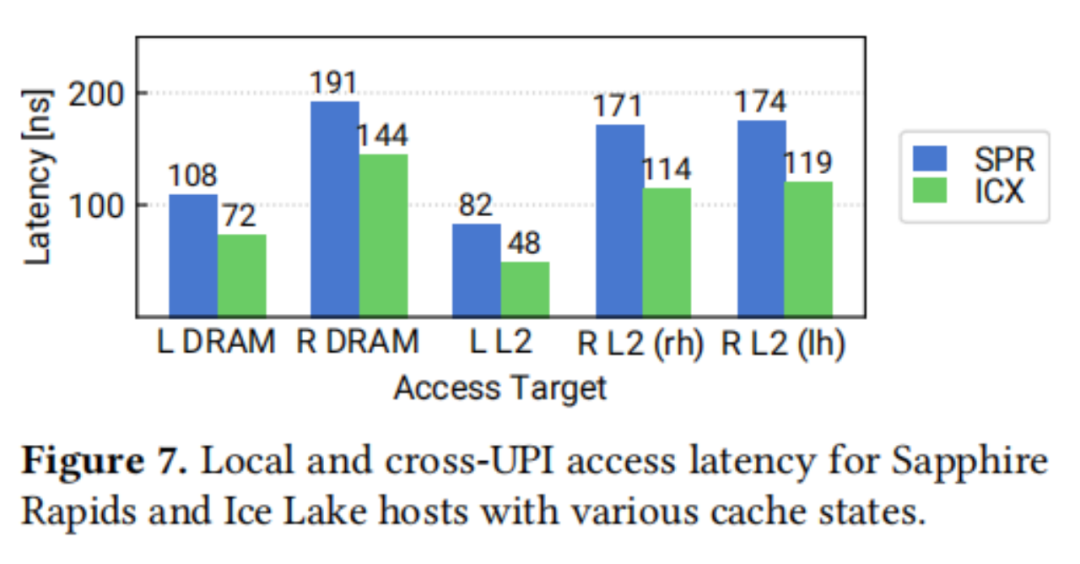

由于一致性互連可能從DRAM或多個緩存層次結構檢索數據,我們測量每種傳輸情況的性能,以了解信號通信的性能影響。圖7顯示了在Ice Lake (ICX)和Sapphire Rapids (SPR)服務器平臺上,對齊的64B對象在各種緩存狀態下的中位數訪問延遲。我們發現,訪問遠程未緩存的DRAM大約是本地DRAM訪問延遲的兩倍。訪問遠程L2緩存中的數據更快:在SPR上為171納秒,在ICX上為114納秒,對于在遠程socket上托管的內存(rh情況),對于在本地socket上托管的內存(lh)則略高。

在這些情況下,遠程CPU已將其L2緩存中的一行寫入并保留在M(修改)狀態,然后本地讀取器訪問該地址。當遠程L2緩存中存在M狀態對象時,它不能存在于任何其他L2緩存中,因此總是本地L2缺失。對于reader homed的內存,讀者的L2缺失導致除了向寫入者的緩存請求遠程請求外,還導致推測性內存讀取。這種推測性讀取是不需要的,并且當對象是reader-homed時,會增加總線利用率并降低性能,因為增加了不必要的流量。無論homing如何,遠程L2訪問都比遠程DRAM訪問更快,表明緩存到緩存傳輸實現了最佳延遲。CC-NIC在其設計中應用了這些觀察結果。CC-NIC將元數據結構放置在writer-homed的內存中:TX描述符環位于主機上,RX環位于NIC home的內存中。它通過使用定期緩存訪問而不是針對內存的目標非時間存儲來增強緩存到緩存傳輸的可能性。然而,NIC接口的工作集大小影響性能,預取訪問也是如此。

確定最優的內存數據布局

NIC元數據,如描述符和信號,展示了每個描述符由一方寫入并由另一方讀取的生產者-消費者訪問模式。例如,TXDs由主機寫入,RXDs由NIC寫入。性能取決于緩存行的訪問模式,因為這決定了為確保一致性所必需的協議通信。

在典型的PCIe NIC接口中,RX緩沖區由主機在NIC實際接收數據包之前分配并發布到RX描述符。這使得在分配緩沖區到RX描述符時無法應用對RX數據包突發的知識。CC-NIC通過利用緩存一致性共享緩沖區管理來克服這個問題。緩存一致性允許主機和NIC同時訪問緩沖池數據結構,而沒有與同時進行的PCIe DMA和CPU訪問(例如,缺乏原子操作)相關的限制。共享緩沖池結構允許NIC在傳輸后將TX緩沖區釋放回池。同樣,NIC可以根據需求分配RX緩沖區并將它們的地址寫入RX描述符環。這導致了一個對稱的設計,避免了額外的隊列來釋放已完成的TX數據包緩沖區和發布空白的RX數據包緩沖區。最后共享緩沖區管理使CC-NIC的緩沖區分配和描述符布局優化成為可能。圖10比較了CC-NIC的緩沖區管理設計與傳統PCIe NIC的設計。

權衡高帶寬和低延遲需求

使用內聯信號時,主機和NIC直接輪詢描述符環內存而不是單獨的寄存器。這導致在寫入和輪詢一系列小于64B緩存行大小的描述符時,緩存行在socket之間抖動,增加了延遲。緩存對齊的描述符通過避免抖動來實現低延遲,但會浪費大量空間(例如,64B中的48B)。為了平衡這些因素,CC-NIC實現了一個優化的解決方案:它將多達4個16B描述符打包到一個緩存行中,未使用的條目清零,并使用每個緩存行一個信號。如果消費者在中間遇到一個空白描述符,它將跳過到下一個緩存行以輪詢后續的描述符組。這在高吞吐量情況下避免了浪費空間,同時在低吞吐量、非批處理的情況下避免了抖動。通過每個描述符組使用一個信號,CC-NIC應用批處理來充分利用每個描述符緩存行。

量化評估

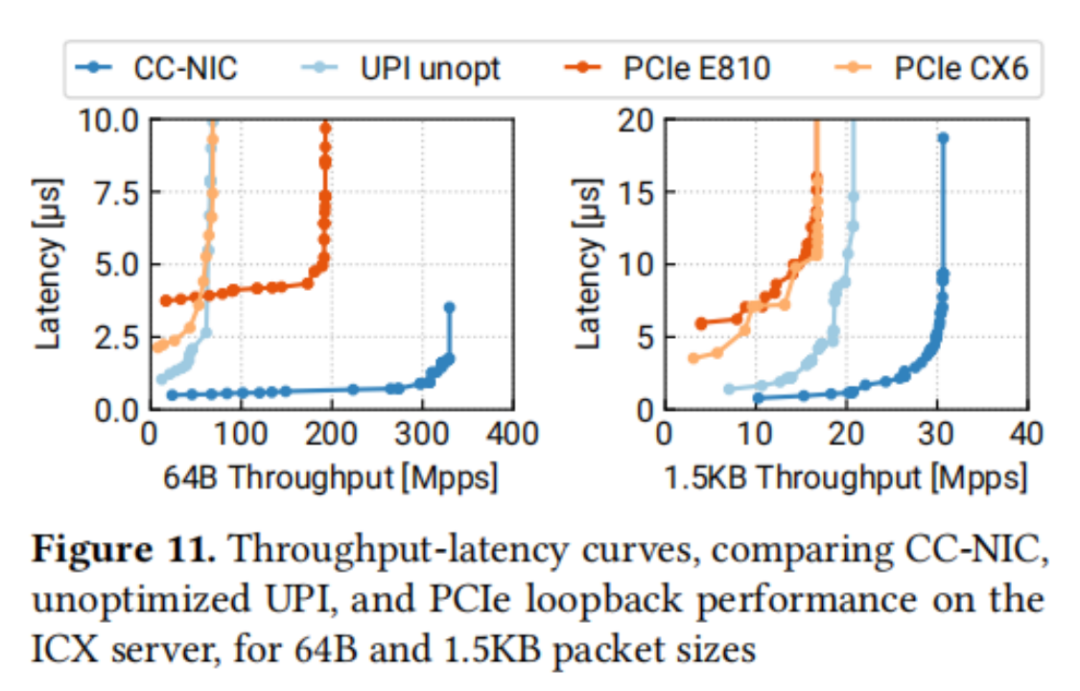

圖11顯示了在ICX服務器上的四種主機-NIC接口的比較:CX6和E810 PCIe NIC,以及在UPI上實現的E810接口的簡單實現,以及CC-NIC。這些結果表明,CC-NIC在延遲改進和高于PCIe的吞吐量方面展現了巨大優勢。CC-NIC的最小延遲比CX6和E810分別低77%和86%。CC-NIC還實現了比E810和CX6高1.7倍和4.3倍的峰值包速率。對于1.5KB數據包,CC-NIC觀察到的比PCIe NIC高1.8倍的數據吞吐量。

總結分析

CC-NIC設計的核心內容除了使用支持緩存一致性的總線接口外,以下幾個關鍵內容對整體性能的提升至關重要:

1、內聯信號:將通知功能內聯到描述符環,對于64B數據包,內聯信號將最小延遲減少了37%,并將最大包速率提高了1.3倍。

2、描述符布局:由于UPI緩存傳輸的64B粒度以及內聯信號所需的直接描述符輪詢,內存布局顯著影響性能。通過將每個描述符緩存對齊(填充)實現低延遲,避免了抖動。將單個16B描述符打包到一個緩存行中通過2.9倍提高了吞吐量。優化的描述符布局在每個緩存行中結合了一個單一的信號和一組描述符。這種布局在匹配最佳最小延遲的同時,實現了3.0倍的吞吐量提升。

3、批處理:批處理對于吞吐量至關重要,對于PCIe NIC,TX批處理允許使用一個MMIO門鈴提交多個數據包,更大的批處理尺寸減少了MMIO操作的速率。對于CC-NIC,TX批處理允許在單個緩存行內傳輸多個描述符。主機端RX批處理主要影響描述符環和緩沖區池上的訪問模式,決定了緩沖區是單獨還是批量處理。

我的回答

結合上述分析,對本文最初提出的問題(本地CPU和設備互聯場景)的回答是:

緩存一致性互連技術為掛接的外部設備提供了實現高性能的可能性,但它的應用并不局限于作為傳統接口的簡單替代。要充分利用緩存一致性的優勢,需要對CPU與外部設備之間的交互機制進行徹底的重構。在這個重構過程中,需要深入考慮幾個方面來最大化緩存一致性的收益,比如內聯信號通知機制、優化的數據和描述符布局以及批處理機制等。只有通過這樣的軟硬件融合優化,才能實現一個高效、可擴展和吞吐延遲均衡的系統。

-

處理器

+關注

關注

68文章

19885瀏覽量

235063 -

cpu

+關注

關注

68文章

11076瀏覽量

216998 -

緩存

+關注

關注

1文章

246瀏覽量

27165 -

異構計算

+關注

關注

2文章

107瀏覽量

16680

原文標題:在異構計算場景下,緩存一致性究竟能帶來多大的價值?

文章出處:【微信號:SDNLAB,微信公眾號:SDNLAB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

介紹ARM存儲一致性模型的相關知識

如何解決數據庫與緩存一致性

一致性規劃研究

加速器一致性接口

Cache一致性協議優化研究

自主駕駛系統將使用緩存一致性互連IP和非一致性互連IP

使用CCIX進行高速緩存一致性主機到FPGA接口的評估

Redis緩存與Mysql如何保證一致性?

深入理解數據備份的關鍵原則:應用一致性與崩潰一致性的區別

異構計算下緩存一致性的重要性

異構計算下緩存一致性的重要性

評論