隨著計算機技術(shù)的發(fā)展,數(shù)據(jù)傳輸速度的要求越來越高。PCI Express(PCIe)作為一種高速串行計算機擴(kuò)展總線標(biāo)準(zhǔn),其性能和可靠性在很大程度上取決于布線設(shè)計。

1. 信號完整性(SI)

信號完整性是指信號在傳輸過程中保持其完整性的能力。在PCIe布線中,信號完整性受到以下幾個因素的影響:

1.1 傳輸線特性

PCIe布線通常使用差分對來傳輸信號,以減少噪聲和提高信號質(zhì)量。差分對的阻抗匹配、長度匹配和間距對信號完整性至關(guān)重要。阻抗不匹配可能導(dǎo)致信號反射,長度不匹配可能導(dǎo)致時序問題,間距不當(dāng)則可能引起串?dāng)_。

1.2 串?dāng)_

串?dāng)_是指一個信號線對另一條信號線的干擾。在高密度的PCIe布線中,串?dāng)_是一個嚴(yán)重的問題。為了減少串?dāng)_,設(shè)計時需要考慮信號線的間距、層間距離和屏蔽措施。

1.3 信號衰減

隨著信號在傳輸線中傳播,信號強度會逐漸衰減。信號衰減受到線材材質(zhì)、線寬、線長和頻率等因素的影響。在高速PCIe布線中,信號衰減可能導(dǎo)致信號失真,影響數(shù)據(jù)傳輸?shù)臏?zhǔn)確性。

2. 電磁兼容性(EMC)

電磁兼容性是指設(shè)備在電磁環(huán)境中正常工作的能力,同時不對其他設(shè)備產(chǎn)生干擾。PCIe布線對EMC的影響主要體現(xiàn)在以下幾個方面:

2.1 輻射發(fā)射

高速信號傳輸會產(chǎn)生電磁輻射,可能對其他設(shè)備造成干擾。為了減少輻射發(fā)射,可以采用屏蔽措施,如使用屏蔽電纜和屏蔽機箱。

2.2 敏感度

PCIe設(shè)備對外部電磁干擾的敏感度也會影響其性能。設(shè)計時需要考慮設(shè)備的屏蔽和接地,以提高其抗干擾能力。

2.3 地平面連續(xù)性

地平面的連續(xù)性對于維持信號的完整性和減少EMI至關(guān)重要。在PCIe布線中,確保地平面的連續(xù)性可以減少信號回路的不連續(xù)性,從而降低EMI。

3. 電源完整性(PI)

電源完整性是指電源系統(tǒng)提供穩(wěn)定、干凈電源的能力。在PCIe布線中,電源完整性受到以下幾個因素的影響:

3.1 電源噪聲

電源噪聲是指電源系統(tǒng)中的電壓波動和紋波。電源噪聲可能導(dǎo)致信號失真和設(shè)備性能下降。為了減少電源噪聲,可以采用去耦電容和電源濾波器。

3.2 電源分布網(wǎng)絡(luò)(PDN)

電源分布網(wǎng)絡(luò)的設(shè)計對于維持電源完整性至關(guān)重要。在PCIe布線中,PDN的設(shè)計需要考慮電源線的阻抗、電流密度和分布均勻性。

3.3 電源完整性與信號完整性的相互作用

電源完整性和信號完整性之間存在相互作用。例如,電源噪聲可能通過電源線和地線耦合到信號線上,影響信號的完整性。

4. 布線設(shè)計的最佳實踐

為了確保PCIe布線的性能和可靠性,以下是一些最佳實踐:

4.1 阻抗控制

確保差分對的阻抗匹配,以減少信號反射和提高信號質(zhì)量。

4.2 差分對長度匹配

盡量保持差分對的長度匹配,以減少時序問題。

4.3 串?dāng)_控制

通過調(diào)整信號線的間距和層間距離,以及采用屏蔽措施,來減少串?dāng)_。

4.4 信號衰減管理

選擇合適的線材和線寬,以及優(yōu)化信號路徑,以減少信號衰減。

4.5 輻射和敏感度控制

采用屏蔽電纜和機箱,以及優(yōu)化設(shè)備的屏蔽和接地,以控制輻射發(fā)射和提高敏感度。

4.6 地平面設(shè)計

確保地平面的連續(xù)性,以減少EMI和提高信號完整性。

4.7 電源噪聲管理

使用去耦電容和電源濾波器,以減少電源噪聲。

-

計算機

+關(guān)注

關(guān)注

19文章

7639瀏覽量

90421 -

信號完整性

+關(guān)注

關(guān)注

68文章

1440瀏覽量

96563 -

PCIe

+關(guān)注

關(guān)注

16文章

1330瀏覽量

84862 -

信號傳輸

+關(guān)注

關(guān)注

4文章

453瀏覽量

20607

發(fā)布評論請先 登錄

NVMe IP高速傳輸卻不依賴XDMA設(shè)計之二:PCIe讀寫邏輯

nvme IP開發(fā)之PCIe上

告別雜亂布線!M型轉(zhuǎn)RJ線束為信號傳輸穩(wěn)定‘護(hù)航’

調(diào)制對信號傳輸質(zhì)量的影響

PCIe數(shù)據(jù)傳輸協(xié)議詳解

如何選擇適合的PCIe配置

PCIe信號完整性問題解決方案

PCIe延遲對系統(tǒng)性能的影響

pcie 4.0與pcie 5.0的區(qū)別

如何檢查pcie插槽兼容性

PCIe的最新發(fā)展趨勢

PCIe接口的工作原理 PCIe與PCI的區(qū)別

功率地和信號地怎么布線

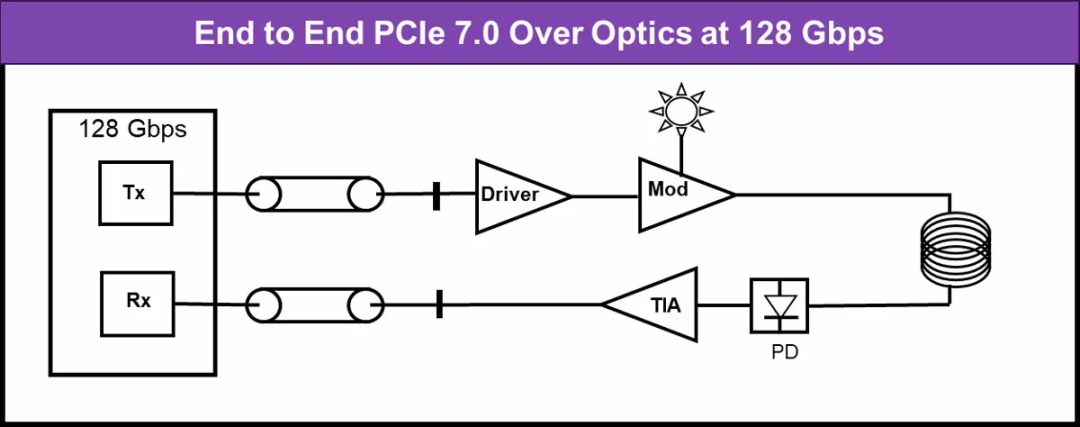

PCIe光傳輸的優(yōu)勢與挑戰(zhàn)

pcie布線對信號傳輸?shù)挠绊?/h1>

pcie布線對信號傳輸?shù)挠绊?/h1>

評論