在系統(tǒng)級仿真中,與DDR4-3200 相比,更高數(shù)據(jù)速率下的 DDR5 的有效帶寬幾乎是其兩倍。這種改進(jìn)是通過提高數(shù)據(jù)速率和增強(qiáng)架構(gòu)來實現(xiàn)的。DDR5 包含從 3200 MT/s 到 8800 MT/s 的數(shù)據(jù)速率。一個值得注意的特性是在DQ接收器中集成了一個多抽頭判決反饋均衡器,可在更高的數(shù)據(jù)速率下抵消碼間干擾(ISI)效應(yīng)。這些發(fā)展旨在滿足下一代 CPU 對每個內(nèi)核帶寬日益增長的要求。

測試要求也同樣發(fā)生了變化,以確保滿足電氣和時序裕量。

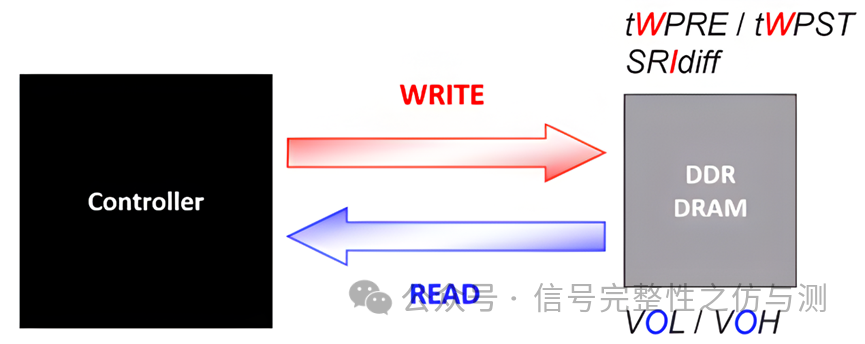

DDR5電氣和時序規(guī)格會根據(jù)信號是讀取還是寫入數(shù)據(jù)而變化。這意味著,例如,斜率或電壓電平取決于信號的方向和來源。寫入數(shù)據(jù)從內(nèi)存控制器發(fā)送(紅色),數(shù)據(jù)從內(nèi)存讀取(藍(lán)色)。寫測試包括“寫入前導(dǎo)碼時序”和“輸入差分斜率”。讀測試包括“讀取高輸出電平和低輸出電平”。DDR5的讀寫數(shù)據(jù)雙向傳輸意味著測試時必須包括讀寫分離步驟,以分析雙向信號的單個數(shù)據(jù)。

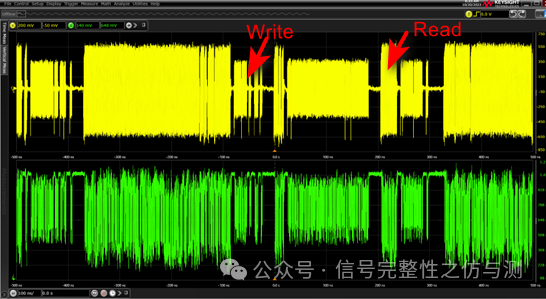

讀寫分離一直是 DDR 總線測試的難點。由于 DDR 總線一直采用讀寫數(shù)據(jù)共享數(shù)據(jù)總線,而 JEDEC 規(guī)范針對讀寫操作制定了不同的指標(biāo),因此如果需要對被測器件和設(shè)備進(jìn)行準(zhǔn)確測試就必須分別對讀和寫進(jìn)行分開測試。一種方法是 Memory Controller 可以編程只進(jìn)行讀或?qū)懖僮饕苑謩e進(jìn)行測試,這種方法不易實現(xiàn)。另外一種方法就是在示波器上根據(jù)讀和寫信號的特點設(shè)置恰當(dāng)?shù)挠|發(fā)進(jìn)行分離。

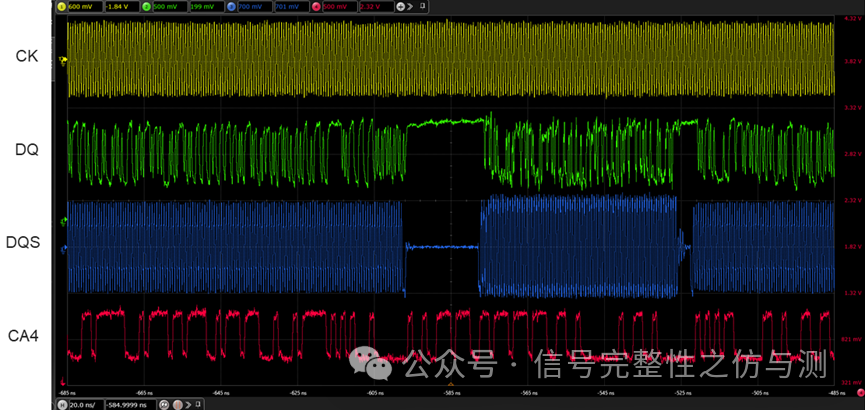

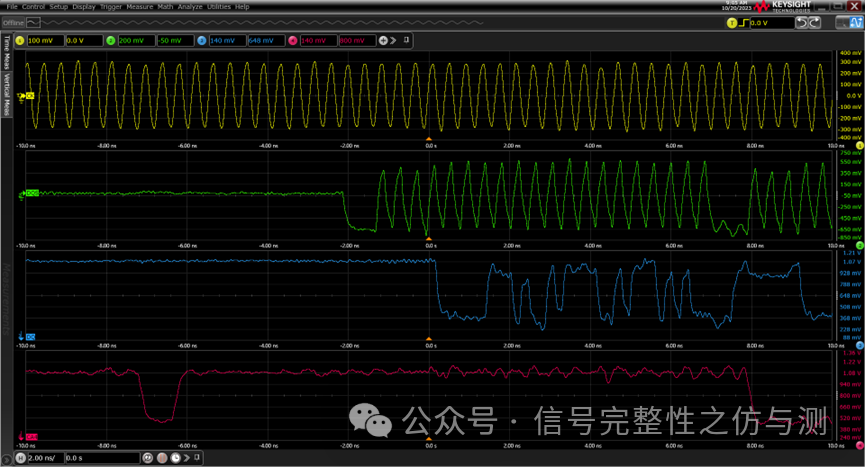

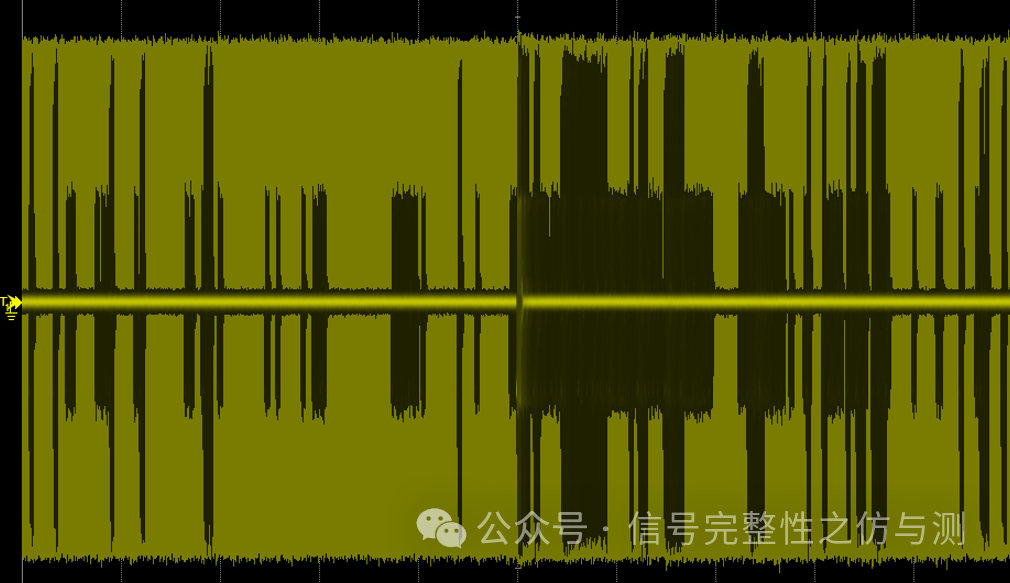

在主板上電的正常操作期間捕獲信號后查看信號可能并不容易。如我們主要關(guān)注的CLK/DQS/DQ/CA4信號,沒有任何后處理,很難判斷讀取和寫入數(shù)據(jù)何時處于活動狀態(tài)。

相位關(guān)系

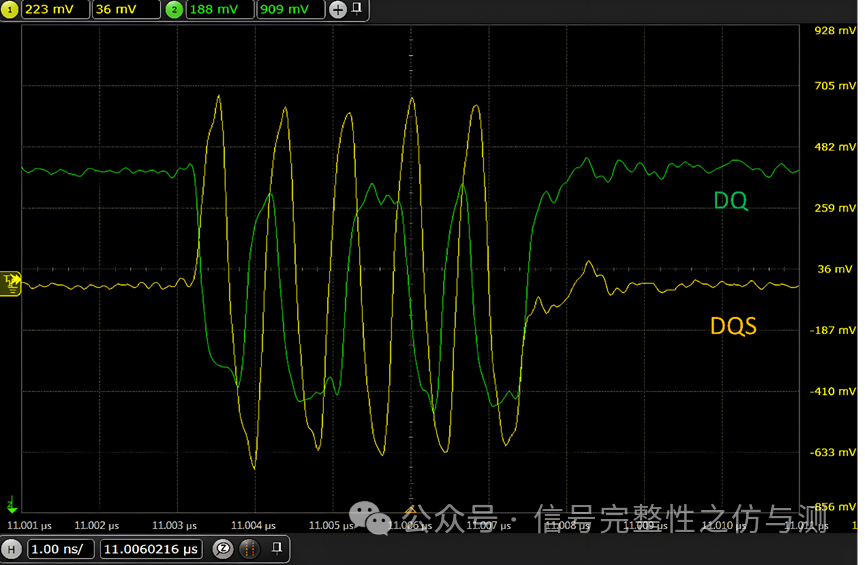

對于DDR4及更早版本,讀取和寫入數(shù)據(jù)遵循可預(yù)測的模式,使測試設(shè)備能夠輕松檢測分離:數(shù)據(jù)相對于寫入選通DQS的中心對齊,讀取時邊緣對齊。

上圖顯示了中心對齊的 DDR4 寫入數(shù)據(jù)和選通信號示例:大部分時序和偏斜對齊的負(fù)擔(dān)都落在內(nèi)存控制器上,因此寫入數(shù)據(jù)以最小的偏斜到達(dá) DRAM 接收器(中心對齊),使數(shù)據(jù)鎖存更容易。

在過往DDR3和DDR4總線上,主要采用DQS前導(dǎo)位或者DQS和DQ的相位差進(jìn)行分離。

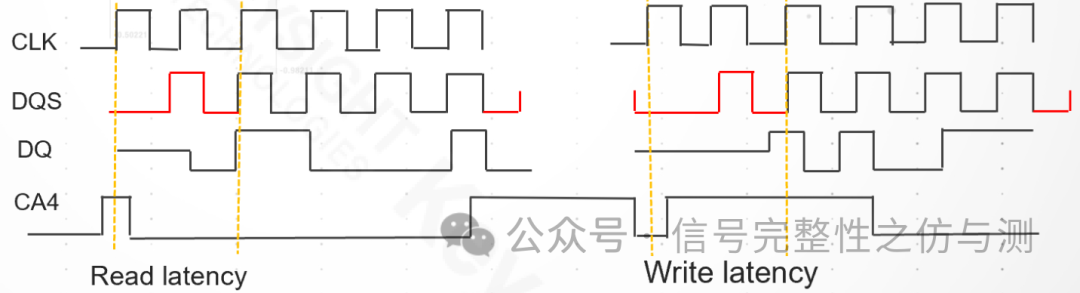

在DDR5總線上,DQS和DQ在讀寫操作時沒有相位差,DQS的讀寫操作的前導(dǎo)碼也是相同的。

因此在DDR5總線上的讀寫分離是一個難點。

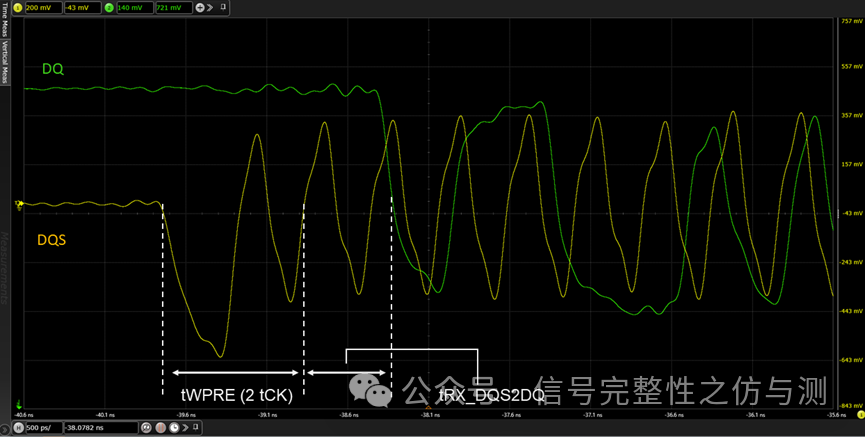

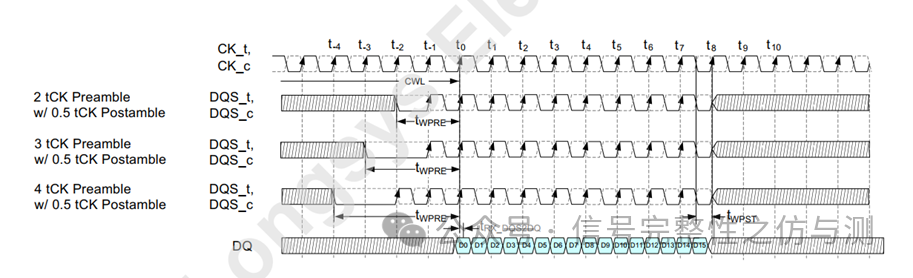

對于DDR5,除了寫入之外,這些規(guī)則幾乎相同。為了降低功耗(DQS 時鐘門控)并簡化寫入訓(xùn)練,DDR5對DRAM輸入使用無與倫比的路徑。但是,還有其他方法可用于讀取和寫入信令。

上圖顯示了寫入數(shù)據(jù)和選通信號之間可能的可變延遲。

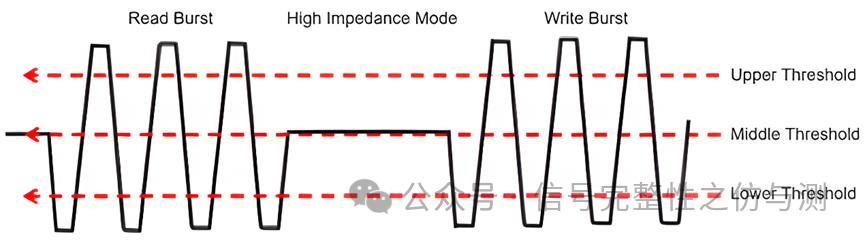

振幅差異

盡管DDR5使用復(fù)雜的協(xié)議來存儲和檢索數(shù)據(jù),但更高的數(shù)據(jù)速率為實現(xiàn)讀寫分離提供了一個有趣的途徑。較高的頻率相關(guān)損耗和信號衰減導(dǎo)致讀寫之間的幅度差異更明顯。由于內(nèi)存流量是盡可能靠近DRAM捕獲的,無論是直接捕獲還是使用interposer,因此讀取數(shù)據(jù)的幅度預(yù)計會更高。了解這些差異可以簡化分離識別過程。一些 DDR5 合規(guī)性工具提供此功能,甚至可以使用機(jī)器學(xué)習(xí)算法來更好地區(qū)分全擺幅突發(fā)和“峰值”邊緣。

命令/地址解碼(CA4)

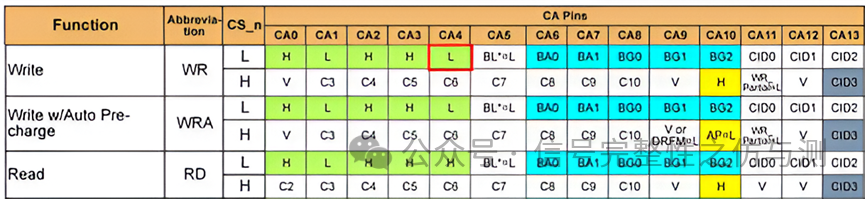

由于DRAM接收讀取和寫入事務(wù)的命令和地址信息,因此很自然地認(rèn)為測試設(shè)備也可以解碼命令以更好地識別分離。這是理想的方案,適用于某些配置。完整命令總線解碼選項的替代方法是對 CA 總線進(jìn)行部分解碼,并僅關(guān)注確定給定命令的突發(fā)類型的 CA 位。對于 DDR5,這是 CA4。

在JEDEC協(xié)議中,很容易就能找到CA4的特別之處,可以看到,寫數(shù)據(jù)時,CA4呈現(xiàn)的特征是低電平;讀數(shù)據(jù)時,CA4呈現(xiàn)的特征是高電平。

那是不是我只要找到持續(xù)的CA4的低電平信號,此時對應(yīng)的數(shù)據(jù)就是寫信號呢?

你想多了!

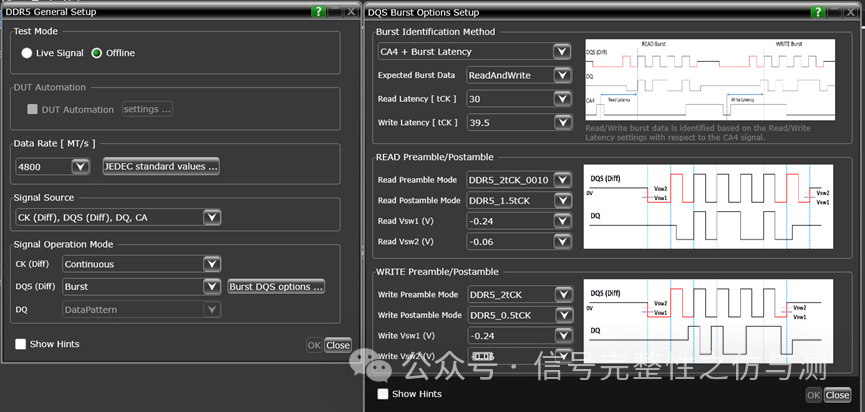

DDR5的一致性測試軟件提供了CA4 lantency分離方法,同樣還有DQS、DQ的Phase分離方法,通過檢測信號的閾值電平來作為一大判斷依據(jù)。

閾值或參考電平用于確定突發(fā)開始和結(jié)束時以及 DQ 和 DQS 信號之間的有效轉(zhuǎn)換。下面顯示了讀信號,然后是電氣空閑狀態(tài),然后是寫信號。

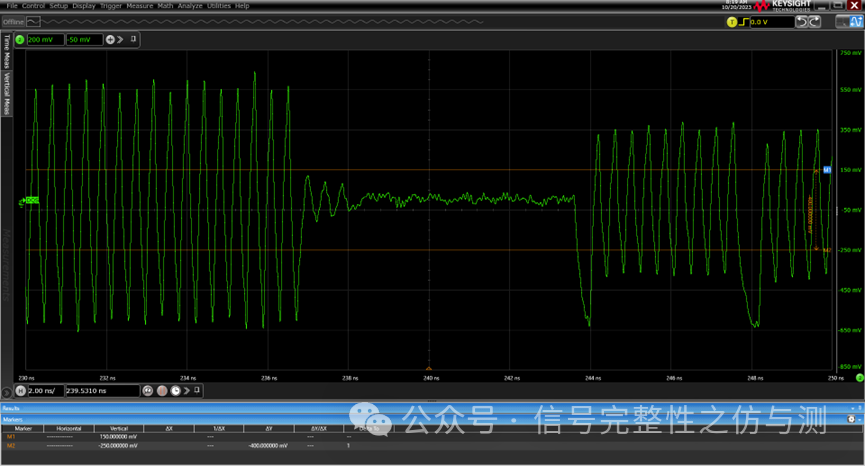

再來看看CA4分離

第 1 步:通過使用屏幕上的標(biāo)記或光標(biāo)來測量延遲以及前導(dǎo)和后導(dǎo)轉(zhuǎn)換電壓,從而確定時序和基準(zhǔn)電平。在下圖中,CA4在有效寫數(shù)據(jù)(綠色)開始時的延遲(紅色)。

第二步,輸入相關(guān)的數(shù)值,很關(guān)鍵。

Preamble參考協(xié)議中的要求

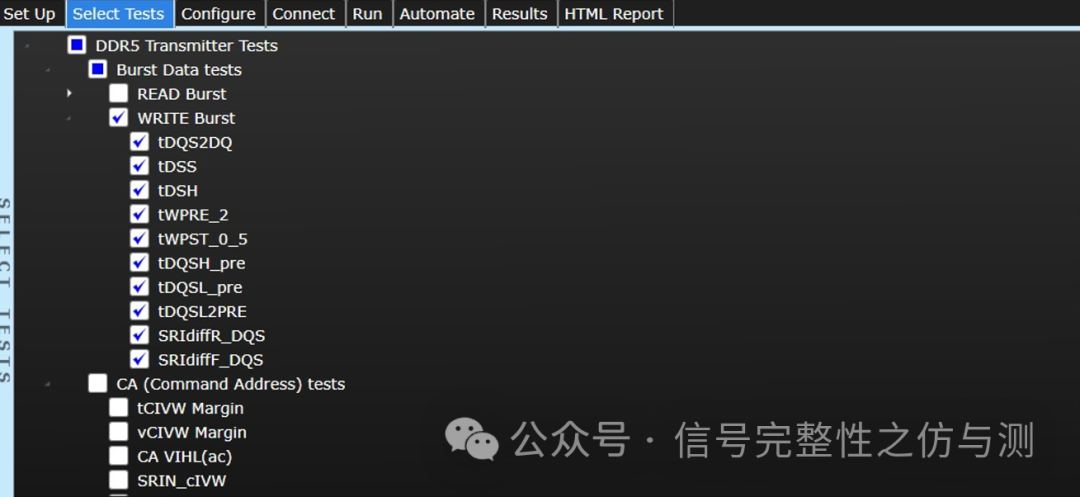

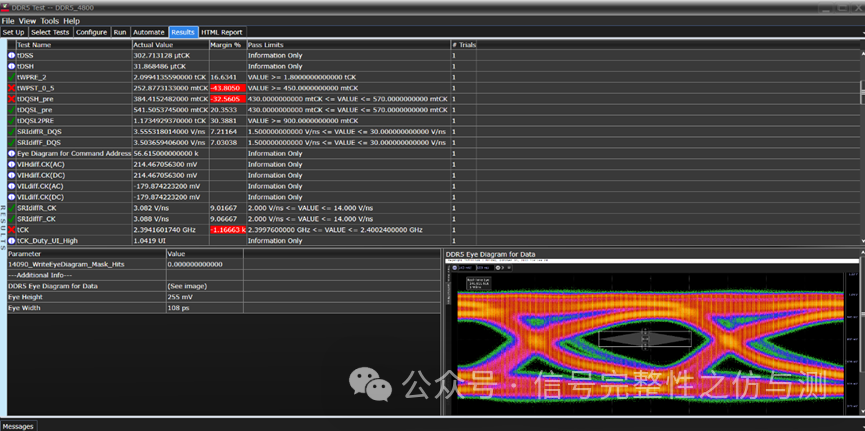

第 3 步:選擇并運行測試。

看這個步驟是不是覺得很簡單,包括開篇的視頻也介紹了如何找read和write lantency,理論上是應(yīng)該行云流水的等著APP跑出結(jié)果就行了。

然而,理論就是理論,無論你是用phase分離還是用CA4 lantency分離,都是在考慮你的耐心,這個問題找了原廠FAE現(xiàn)場,找了付費的技術(shù)支持遠(yuǎn)程連線,折騰了兩個月也沒說出個1234,分離的成功率確實是太低,就算能分,也要跑小時以上。

算了,還是推薦最原始的分離方法,1分鐘即可分離。

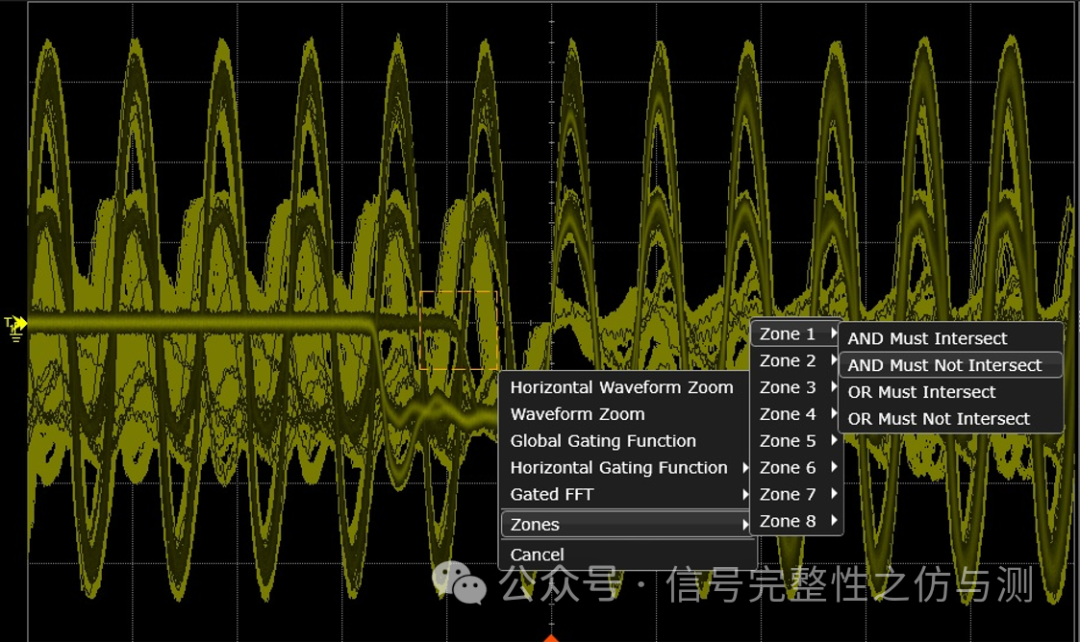

將上述波形展開,讀寫信號都混在一起。

右鍵→Zones→AND Must Not Intersect

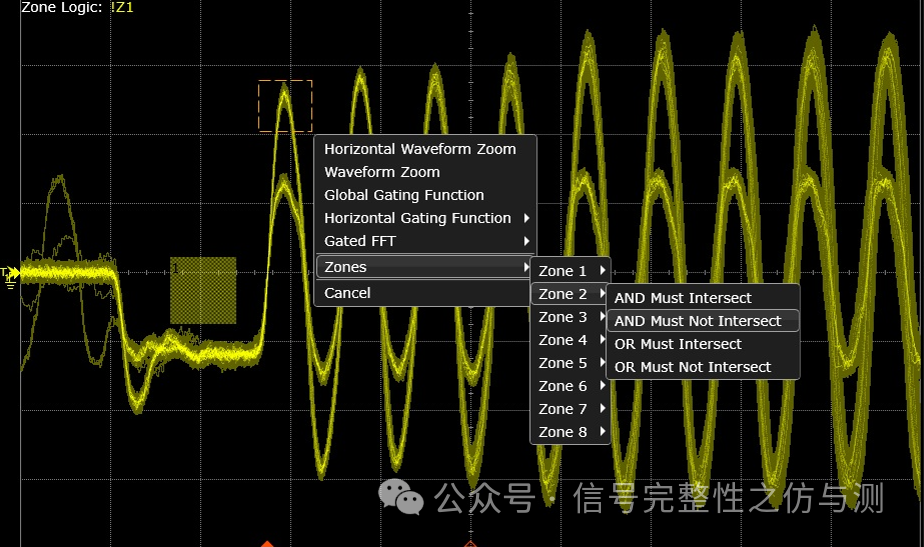

同樣的方法,劃第二個框

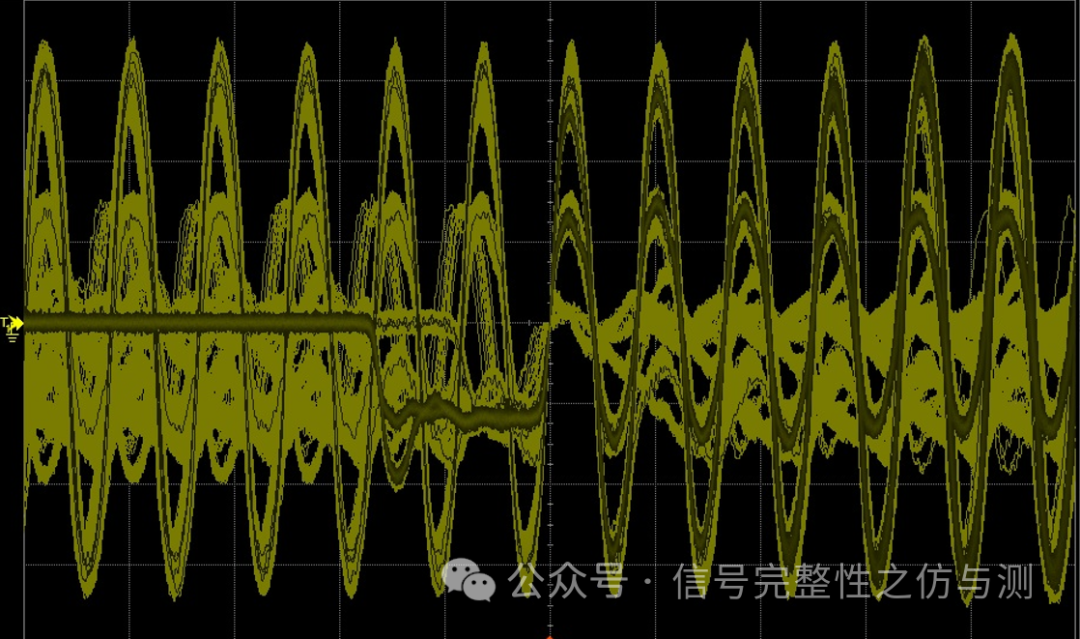

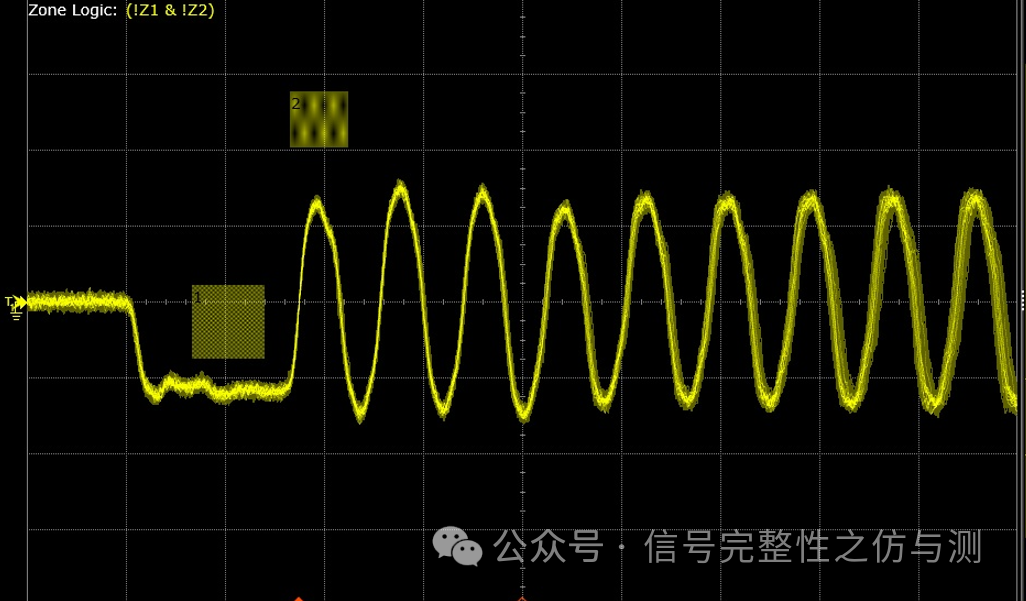

DQS分離成功

DQS分離成功后再看DQ眼圖也就眉清目秀了。

總而言之,讀寫分離采用InfiniiScan要遠(yuǎn)比APP要高效簡單。

-

仿真

+關(guān)注

關(guān)注

52文章

4291瀏覽量

135918 -

DDR4

+關(guān)注

關(guān)注

12文章

333瀏覽量

41767 -

DDR5

+關(guān)注

關(guān)注

1文章

447瀏覽量

24902

原文標(biāo)題:DDR5:揭秘讀寫分離技術(shù)的奧秘

文章出處:【微信號:si-list,微信公眾號:高頻高速研究中心】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

DDR5內(nèi)存接口芯片組如何利用DDR5 for DIMM的優(yōu)勢?

Introspect DDR5/LPDDR5總線協(xié)議分析儀

DDR3/4都還沒玩夠,DDR5已經(jīng)來啦

DDR5這么快,為啥還能那么穩(wěn)?

三種主流內(nèi)存技術(shù)(DDR、GDDR、LPDDR)的速度對比與應(yīng)用和DDR5芯片的設(shè)計

Cadence公司發(fā)布了關(guān)于即將發(fā)布的DDR5市場版本以及技術(shù)的進(jìn)展

DDR5內(nèi)存將在明年實現(xiàn)量產(chǎn)

ddr5的主板可以用ddr4內(nèi)存嗎 幾代CPU才能上DDR5

0706線下活動 I DDR4/DDR5內(nèi)存技術(shù)高速信號專題設(shè)計技術(shù)交流活動

揭秘DDR5的讀寫分離技術(shù)奧秘

揭秘DDR5的讀寫分離技術(shù)奧秘

評論