DDR3是2007年推出的,預計2022年DDR3的市場份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。

最開始的DDR,芯片采用的是TSOP封裝,管腳露在芯片兩側的,測試起來相當方便;但是,DDRII和III就不一樣了,它采用的是BGA封裝,所有焊點是藏在芯片的底部的,測試起來非常不便,一般需要提前預留測試點。

在DDR讀寫burst分析之前,首先得把read burst和write burst分離出來,讀寫雙向的數據全部都擱在DQS和DQ上。那么,DDR的手冊中,留下了哪些線索供我們進行讀寫的分離呢?

要實現DDR的快速的便捷的分離,在讀寫分離之前,我們必須得知道DDR讀寫信號之間的特征差異。首先,看看SPEC里面的定義:

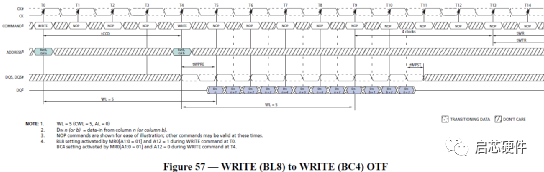

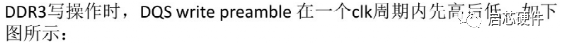

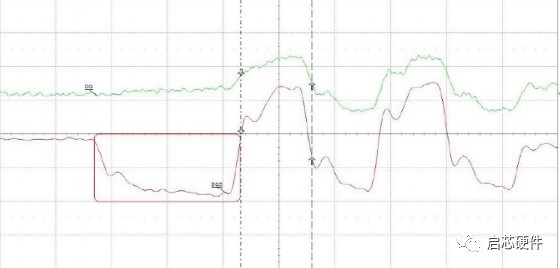

方法一:preamble的差異

在每次的burst之前,DQS會從高阻態切換到一段負脈沖,然后才開始正常的讀寫。這段負脈沖,我們叫做preamble(preamble實際上是在讀寫前,DQS提前通知DRAM芯片或者是controller的信號)。一般說來,讀數據DQS的preamble寬度要大于寫數據。對于DDR3,情況就更簡單了。因為在DDR3中,讀數據的preamble是負脈沖,寫數據的preamble是正脈沖。

方法二:幅度上的差異

一般在DRAM端進行測試,寫數據從memory controller出來,經過了主板PCB板,內存插槽和內存條PCB板,到達DRAM顆粒的時候,信號已經被衰減了,而讀數據剛剛從DRAM出來,還沒有經過任何的衰減,因此讀數據的幅度要大于寫數據。

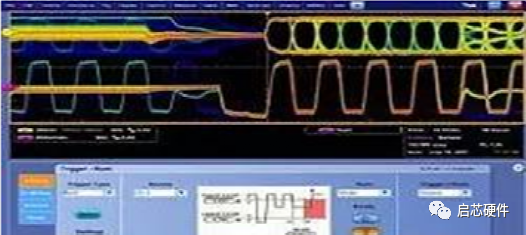

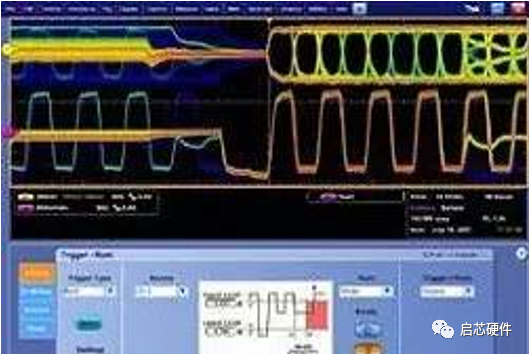

方法三:對齊方式

寫數據是DQS和DQ centre-align(中間對齊), 讀數據DQS和DQ是edge align(邊沿對齊),memory controller在接收到內存的讀數據時,在controller內部把DQS和DQ的相位錯開90度,實現中間對齊來采樣(這個過程示波器就看不到咯);

方法四:斜率的差異:

讀數據的斜率大于寫數據。一般在DRAM端進行測試,寫數據從memory controller出來,經過了主板PCB板,內存插槽和內存條PCB板,到達DRAM顆粒的時候,信號已經被衰減了,所以,斜率也小一些;而讀數據剛剛從DRAM出來,還沒有經過任何的衰減,因此讀數據的斜率要大于寫數據。也可以從下圖得到區分。

Read

Write

總結:

在計算機內存系統中,DDR3(Double Data Rate 3)是一種內存類型,具有讀寫分離(Read-Write Separation)的特性。這種特性可以在一定程度上提高內存的性能和效率。

DDR3的讀寫分離是DDR內存的一項基本功能,它是通過DQ和DQS信號來區分讀操作和寫操作的。

讀寫分離原理:

讀寫分離是指DDR3內存模塊在執行讀取和寫入操作時使用不同的內部電路和通道。這使得內存可以同時進行讀取和寫入操作,而不需要等待一個操作完成后再執行另一個操作。這樣可以顯著提高內存的數據傳輸速度和效率,從而加快整個系統的響應速度。

在DDR3內存中,DQ信號用于傳輸數據,而DQS信號用于傳輸數據讀取和寫入的時鐘信號。在讀操作時,DQS信號會與DQ信號的邊沿對齊,而在寫操作時,DQS信號會在DQ信號的中央對齊。這種不同的對齊方式使得DDR3內存可以區分讀操作和寫操作。

內部通道分離:

DDR3內存模塊內部通常分為讀取通道和寫入通道。這兩個通道可以并行工作,分別處理讀取和寫入操作。通過這種分離,讀取和寫入操作可以同時進行,減少了等待時間。

命令隊列:

DDR3內存模塊通常具有命令隊列(Command Queue)的功能。命令隊列可以在內存控制器和內存模塊之間緩存一系列的讀取和寫入命令。這有助于提高內存的效率,因為內存控制器可以將命令連續發送到內存模塊,而無需等待每個命令的完成。

并行性提高性能:

讀寫分離以及命令隊列的特性使DDR3內存模塊能夠在一定程度上實現并行性,從而提高了內存的性能。它可以在處理大量數據時更加高效,同時也有助于降低內存延遲。

利用DDR3內存中讀數據和寫數據之間信號特征的差異:在每次的burst開始時,DQS會從高阻態切換到一段負脈沖,然后才開始正常的讀寫。這段負脈沖叫做preamble(preamble實際上是在讀寫前,DQS提前通知DRAM芯片或者是controller的信號)。一般說來,讀數據DQS的preamble寬度要大于寫數據。對于DDR3,情況就更簡單了。因為在DDR3中,讀數據的preamble是負脈沖,寫數據的preamble是正脈沖。

幅度上的差異:一般在DRAM端進行測試,寫數據從memory controller出來,經過了主板PCB板,內存插槽和內存條PCB板,到達DRAM顆粒的時候,信號已經被衰減了,而讀數據剛剛從DRAM出來,還沒有經過任何的衰減,因此讀數據的幅度要大于寫數據。

請注意,對于DDR3內存的讀寫分離具體實現可能會因不同的硬件設備和系統環境而有所不同。如果您需要更詳細或最新的信息,建議咨詢相關的硬件工程師或參考最新的技術文檔。

-

芯片

+關注

關注

459文章

52316瀏覽量

438159 -

DDR3

+關注

關注

2文章

283瀏覽量

43014 -

封裝

+關注

關注

128文章

8601瀏覽量

145023 -

DDR

+關注

關注

11文章

731瀏覽量

66537 -

BGA

+關注

關注

5文章

570瀏覽量

48273

發布評論請先 登錄

基于FPGA的DDR3多端口讀寫存儲管理系統設計

【紫光同創國產FPGA教程】【第十章】DDR3讀寫測試實驗

DDR3 SDRAM配置教程

基于FPGA的DDR3多端口讀寫存儲管理設計

cyclone V控制DDR3的讀寫,quartusII配置DDR3 ip核后,如何調用實現DDR3的讀寫呢,謝謝

DDR3芯片讀寫控制及調試總結

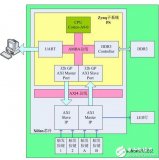

PL與CPU通過DDR3進行數據交互的應用設計

構建SoC系統中PL讀寫DDR3

ddr4和ddr3內存的區別,可以通用嗎

基于FPGA的DDR3多端口讀寫存儲管理的設計與實現

闡述DDR3讀寫分離的方法

闡述DDR3讀寫分離的方法

評論