本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

MIG控制器支持兩種接口:(1)簡單用戶控制邏輯接口;(2)AXI接口。該工程采用前者,后面會整理DDR3的AXI總線訪問方法。

下面簡單介紹一下MIG控制器IP核的使用以及FPGA板上測試結果。

01軟硬件平臺

02IP核參數配置

MIG(Memory Interface Generator)IP核提供了用戶接口邏輯,以便于實現對DDR的訪問。有關MIG的詳細描述,可以參考官方文檔:ug586。這里不展開介紹。

接口配置界面,保持默認選項。

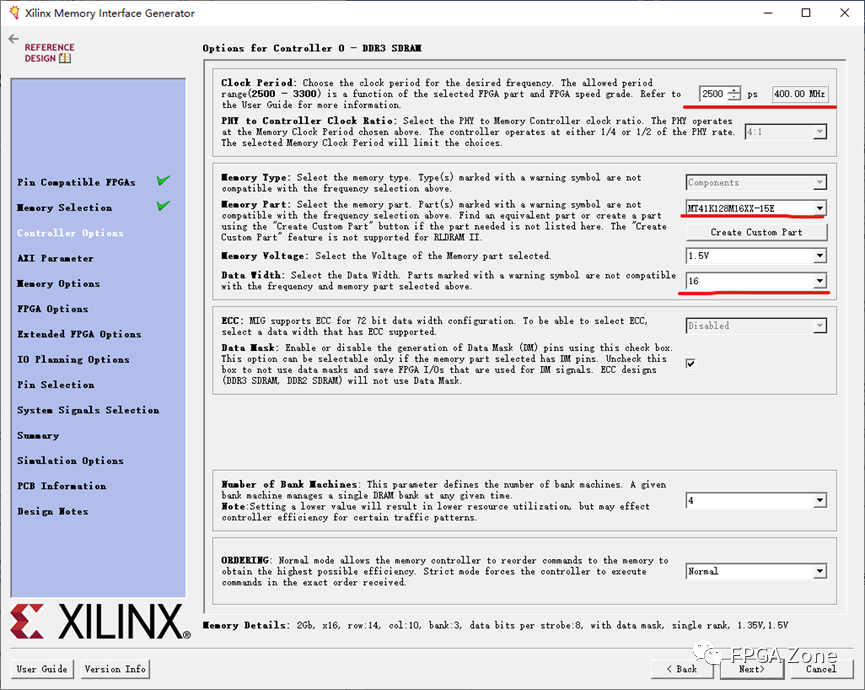

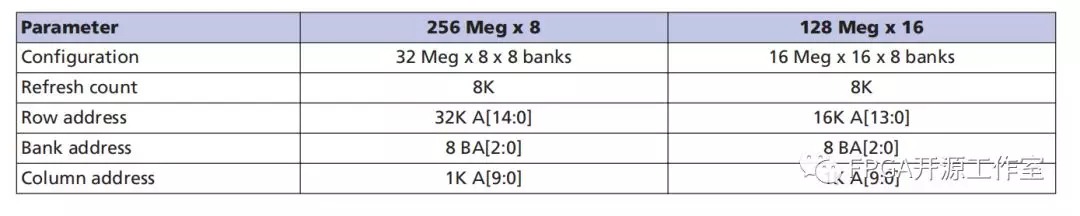

- Clock Period:配置主時鐘頻率,這里選擇400M。由于DDR是雙沿工作,所以讀寫速率為400M2Data Width(16bits);

- 主時鐘頻率和用戶時鐘頻率比例:4:1,因此生成的用戶時鐘為100M;

- Memory Part:配置DDR參數,根據實際情況選擇;

- Data Mask:如果選用的DDR帶有data mask就選上,并將信號拉低,表示不屏蔽數據接口;

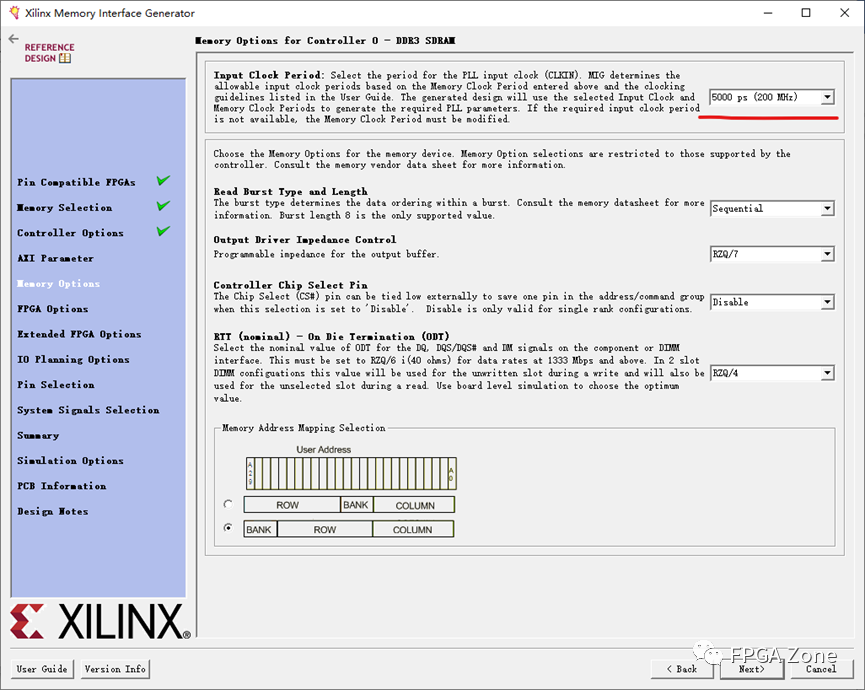

Input Clock Period:輸入時鐘,這里選擇200M。

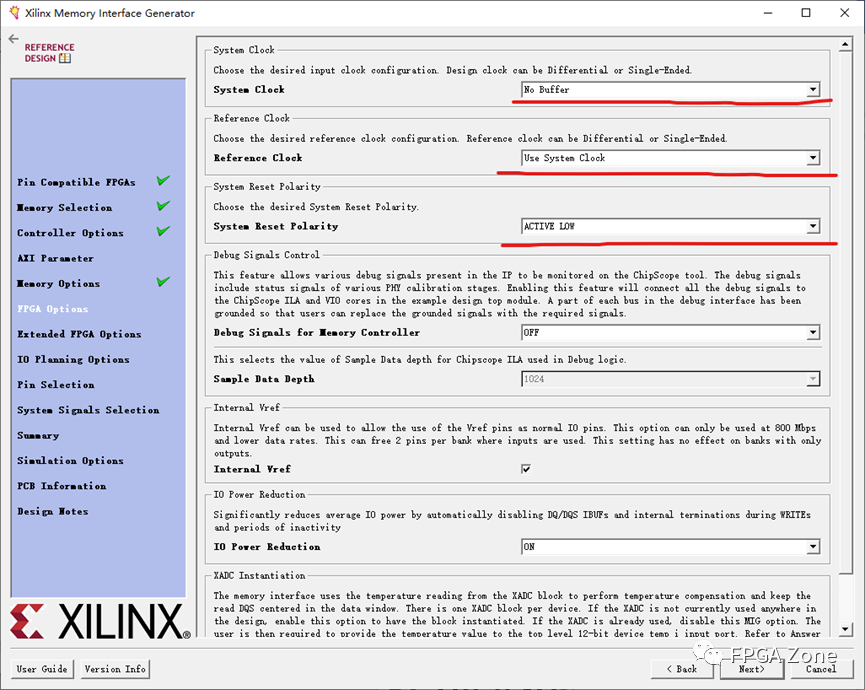

- System Clock:No Buffer;

- Reference Clock:使用系統時鐘;

- 系統復位信號:低電平有效;

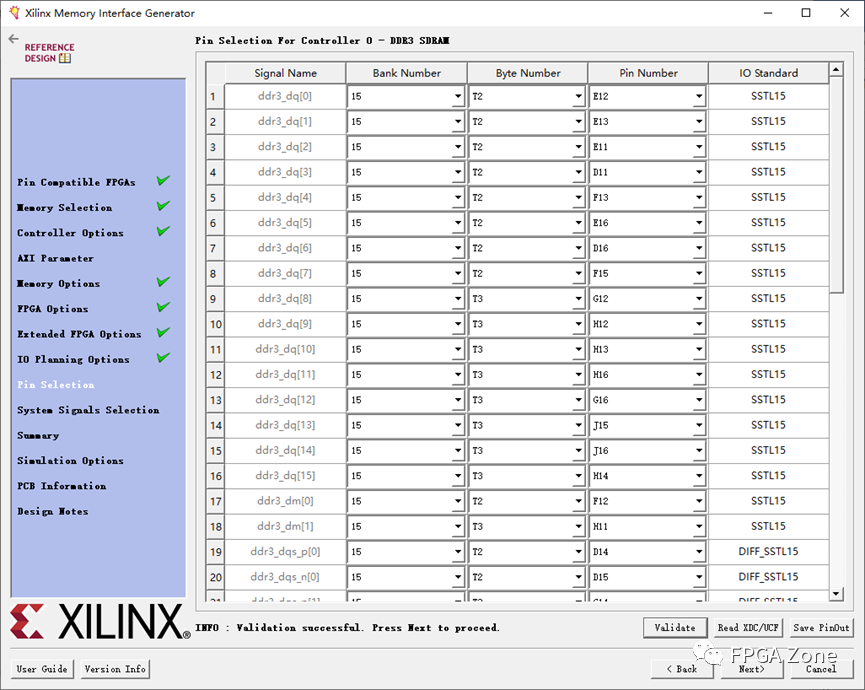

讀取XDC文件管腳配置,并點擊validate,進行校驗。

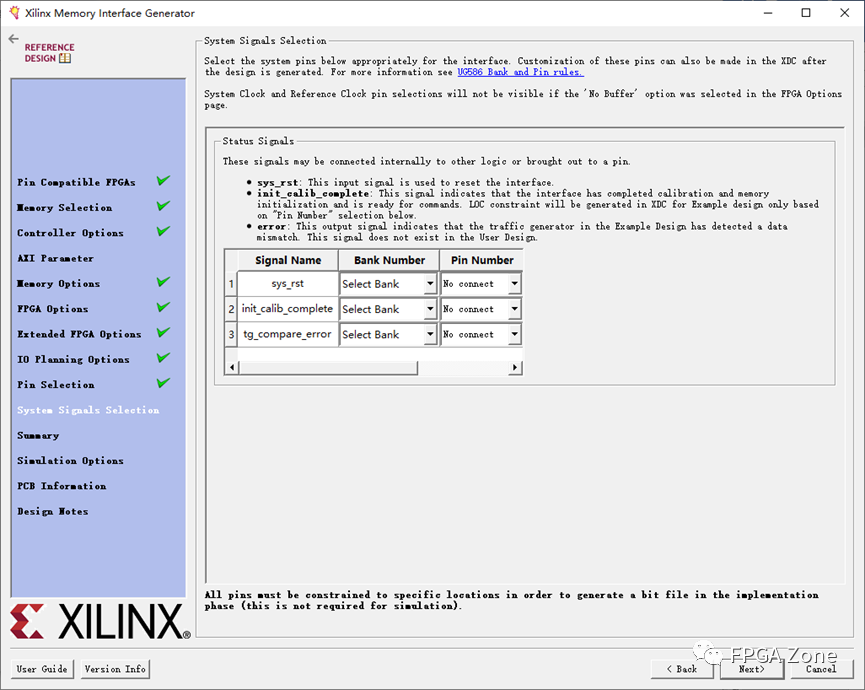

系統信號選擇不用配置,保持默認選項即可。

03用戶接口 & 讀寫時序

MIG IP產生的用戶接口信號是以app_*格式命名:

input [127:0] app_rd_data; //讀數據

input app_rd_data_end; //讀數據結束

input app_rd_data_valid;//讀數據有效

input app_rdy; //MIG控制器準備好讀寫

input app_wdf_rdy; //MIG控制器準備好寫

output [27:0] app_addr; //讀寫地址

output [2:0] app_cmd; //讀寫命令

output app_en; //控制命令使能

output [127:0] app_wdf_data; //寫數據

output app_wdf_end; //寫數據結束

output app_wdf_wren; //寫數據使能

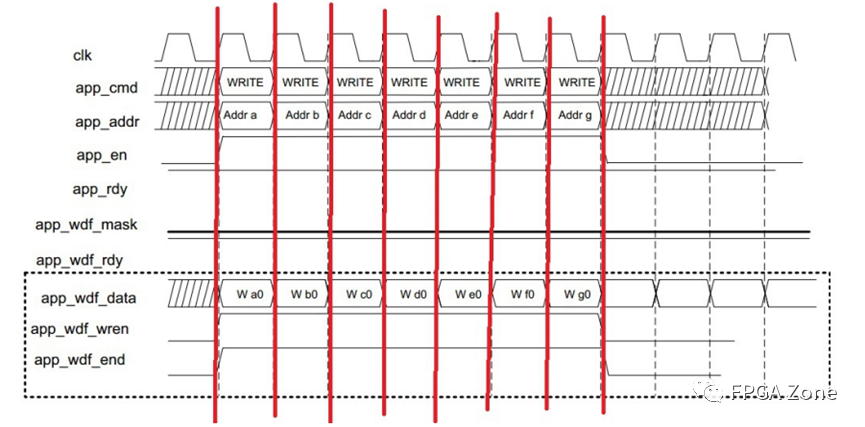

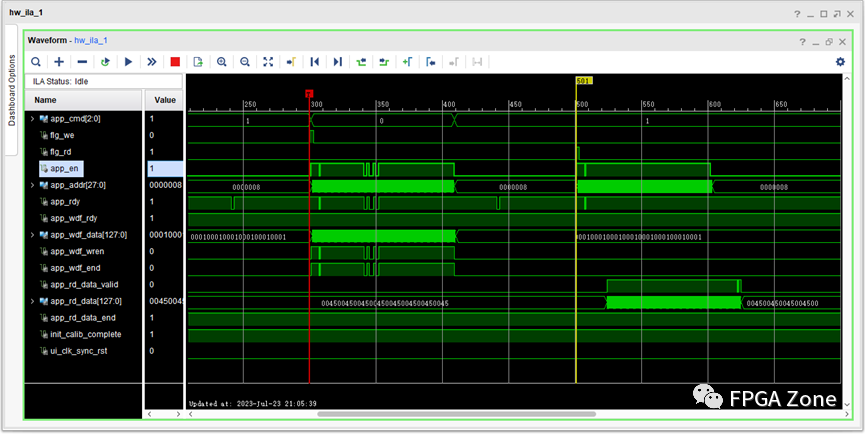

DDR寫時序如下圖所示。邏輯比較簡單,將所有信號嚴格對齊即可。但有一個需要注意的地方,就是當 app_rdy 和 app_wdf_rdy 都為高的時候,才能同時拉高 app_en ,這時寫入的數據才有效。

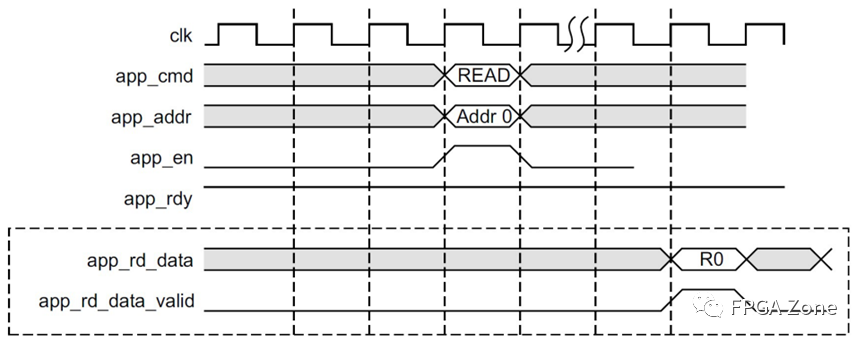

DDR讀時序如下圖所示。app_cmd、app_addr、app_en、app_rdy信號嚴格對齊即可,但是同樣需要在 app_rdy 拉高的情況下,才能拉高 app_en 。另外,數據讀出會略有延遲。

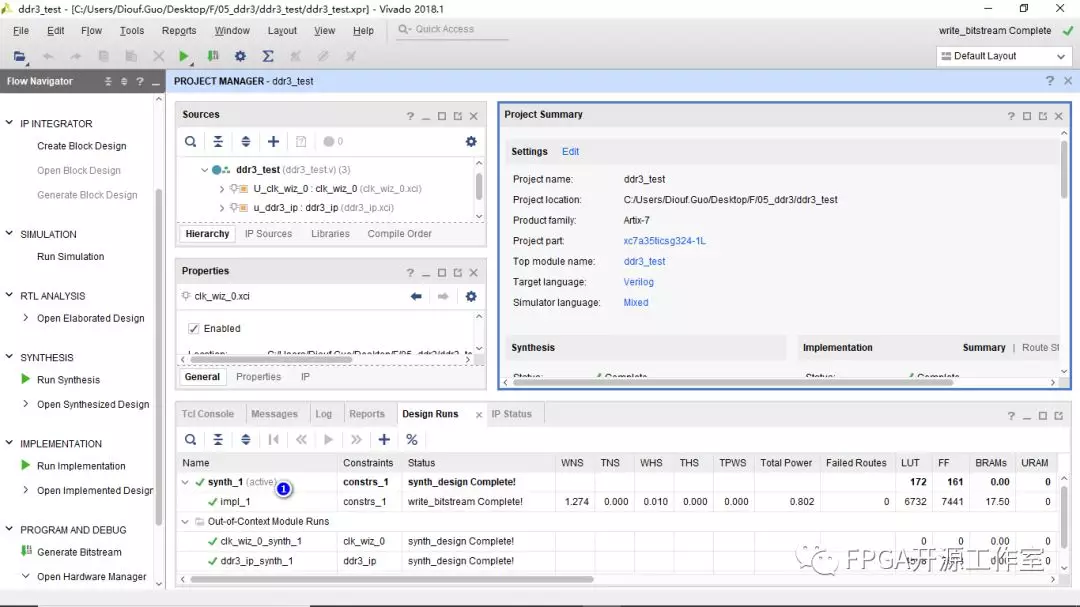

04Vivado工程源碼結構

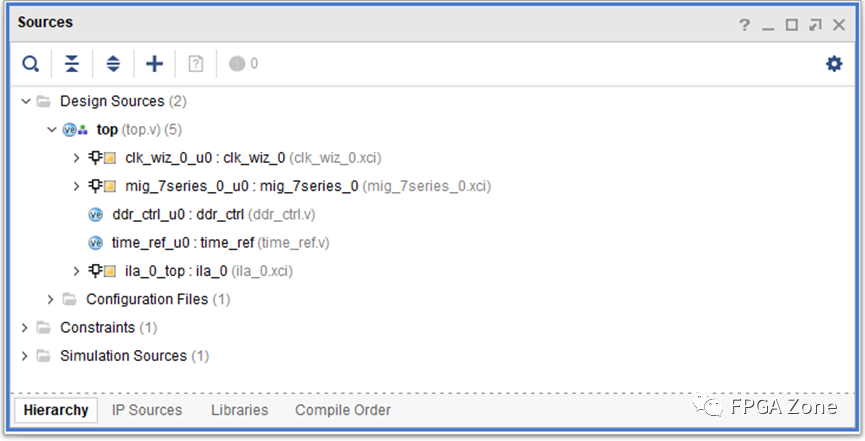

本工程源碼結構如下圖所示。

- ddr_ctrl:ddr用戶接口讀寫控制模塊;

- clk_wiz_0:產生200M時鐘供MIG IP使用;

- time_ref:系統時間基準模塊,以1s為周期計數;

05實現功能 & 測試結果

該Vivado工程主要用于FPGA DDR3讀寫功能測試。基于用戶控制邏輯接口,以1s為周期,每周期內完成1次讀寫操作。板上測試1次讀寫操作的結果如下圖所示。

-

FPGA

+關注

關注

1643文章

21985瀏覽量

615043 -

控制器

+關注

關注

114文章

17019瀏覽量

183246 -

DDR3

+關注

關注

2文章

283瀏覽量

42994 -

接口

+關注

關注

33文章

8963瀏覽量

153331 -

AXI

+關注

關注

1文章

135瀏覽量

17136

發布評論請先 登錄

基于FPGA的DDR3多端口讀寫存儲管理系統設計

基于Digilent的Arty Artix-35T FPGA開發板的DDR3讀寫控制

基于Arty Artix-35T FPGA開發板的DDR3和mig介紹

【紫光同創國產FPGA教程】【第十章】DDR3讀寫測試實驗

基于FPGA的DDR3多端口讀寫存儲管理設計

基于FPGA的DDR3六通道讀寫防沖突設計

基于FPGA的DDR3 SDRAM控制器的設計與優化

基于FPGA的DDR3多端口讀寫存儲管理的設計與實現

關于FPGA外部的DDR3 DRAM怎么回事

基于FPGA的DDR3多端口讀寫存儲管理的設計與實現

基于FPGA的DDR3讀寫測試

基于FPGA的DDR3讀寫測試

評論