隨著對計(jì)算能力、自主系統(tǒng)和下一代架構(gòu)的需求持續(xù)攀升,半導(dǎo)體行業(yè)正經(jīng)歷著前所未有的向萬物智能轉(zhuǎn)變的趨勢。由此,芯片的復(fù)雜程度以及系統(tǒng)和產(chǎn)品中的軟件含量正以驚人的速度呈指數(shù)級增長。

以汽車行業(yè)為例。制造商及其供應(yīng)商正在運(yùn)用全新且頗具爭議的電氣/電子(EE)架構(gòu),對車輛及系統(tǒng)級組件進(jìn)行重新設(shè)計(jì),以此打造差異化的競爭優(yōu)勢。這一趨勢同樣波及工業(yè)自動化、高性能計(jì)算(HPC)數(shù)據(jù)中心以及航空航天等領(lǐng)域,其中軟件定義的系統(tǒng)驅(qū)動著強(qiáng)大的計(jì)算能力,不僅體現(xiàn)在最新的智能手機(jī)、汽車和相機(jī)等邊緣設(shè)備上,還體現(xiàn)在匯聚海量數(shù)據(jù)的核心數(shù)據(jù)中心。

如今,人工智能已滲透到現(xiàn)代科技的方方面面,芯片開發(fā)者面臨全新的挑戰(zhàn):確保產(chǎn)品在激烈的計(jì)算需求下達(dá)到預(yù)期的性能表現(xiàn),并穩(wěn)定、高效地運(yùn)行。這些變革正挑戰(zhàn)著傳統(tǒng)設(shè)計(jì)與驗(yàn)證方法的極限,亟需創(chuàng)新解決方案來應(yīng)對現(xiàn)代芯片和系統(tǒng)架構(gòu)的需求。

此時,硬件輔助驗(yàn)證(HAV)應(yīng)運(yùn)而生,成為助力開發(fā)者優(yōu)化設(shè)計(jì)行為、應(yīng)對復(fù)雜性并確保系統(tǒng)在實(shí)際應(yīng)用中順暢運(yùn)行的關(guān)鍵技術(shù)。

在本篇文章中,我們將深入探討HAV的重要性,剖析不同應(yīng)用場景,分析AI如何塑造新的設(shè)計(jì)需求,并探討開發(fā)先進(jìn)芯片所需的靈活且適應(yīng)行業(yè)需求的解決方案。

芯片設(shè)計(jì)優(yōu)化之路:從IP到軟件定義系統(tǒng)

要理解現(xiàn)代芯片開發(fā)的復(fù)雜性,我們需溯本逐源,檢查過程的每一個階段,從IP的基礎(chǔ)構(gòu)建模塊開始。這些模塊作為先進(jìn)芯片架構(gòu)的核心。IP最初只是起點(diǎn),隨后演變成復(fù)雜的系統(tǒng),當(dāng)與軟件結(jié)合時,創(chuàng)造出旨在改善我們?nèi)粘I畹膽?yīng)用程序。為了實(shí)現(xiàn)最佳性能,從IP到系統(tǒng)硬件和軟件的每個組件都必須共同優(yōu)化。

對于芯片開發(fā)者而言,主要存在兩種策略選擇。一是自主開發(fā),利用自身的專業(yè)知識和專有設(shè)計(jì)來構(gòu)建核心模塊;二是獲取授權(quán),從諸如新思科技等行業(yè)領(lǐng)先企業(yè)處直接獲得相應(yīng)模塊的使用許可。然而,這一過程并未就此終結(jié)。完成IP選擇、集成以及芯片制造之后,仍需進(jìn)行后續(xù)步驟。芯片隨后將被集成至電路板中,構(gòu)成高性能加速系統(tǒng)的核心架構(gòu)。隨后,設(shè)計(jì)這些系統(tǒng)以驅(qū)動并執(zhí)行廣泛的軟件應(yīng)用,涵蓋從低級驅(qū)動程序至高級AI框架及應(yīng)用等多個層級。這一綜合性策略確保各個組件能夠和諧運(yùn)作,從而在整個AI加速生態(tài)系統(tǒng)中實(shí)現(xiàn)最大化的效率與性能。

盡管從IP模塊發(fā)展至成熟的AI加速系統(tǒng)這一過程在理論上顯得較為直接,但實(shí)際操作中卻充滿挑戰(zhàn)。關(guān)鍵在于:如何采取相應(yīng)措施,以確保這些系統(tǒng)在整個開發(fā)流程的各個階段,以及從功能性正確性、性能表現(xiàn)至功耗控制等多個維度上,均能夠按照預(yù)期目標(biāo)穩(wěn)定運(yùn)行?

在萬物智能時代的使用案例與芯片設(shè)計(jì)驗(yàn)證

確保從IP到系統(tǒng)和軟件的一切都能正確運(yùn)行并非易事。如下圖所示,在整個設(shè)計(jì)過程中必須徹底驗(yàn)證幾個關(guān)鍵用例。

通過RTL回歸進(jìn)行功能驗(yàn)證、IP性能驗(yàn)證和合規(guī)性檢查對于確認(rèn)IP在系統(tǒng)級環(huán)境中按預(yù)期運(yùn)行至關(guān)重要。早期階段的性能分析、低功耗評估和測試生成同樣對于確保效率和可靠性極為關(guān)鍵。此外,還必須納入安全、安保和硅生命周期管理等關(guān)鍵考慮因素,以滿足現(xiàn)代設(shè)計(jì)需求。

隨著產(chǎn)品的演進(jìn)以及工作負(fù)載和系統(tǒng)的復(fù)雜性增加,傳統(tǒng)的驗(yàn)證技術(shù)變得不再可行,必須采用新的方法論。

市場需求推動HAV架構(gòu)的演進(jìn)

硬件輔助驗(yàn)證(HAV)──一種能夠大幅提升驗(yàn)證任務(wù)執(zhí)行速度的仿真與原型設(shè)計(jì)技術(shù)──不久前被引入市場,用以增強(qiáng)基于仿真的驗(yàn)證手段及其他傳統(tǒng)技術(shù),不過起初僅應(yīng)用于最為高端的設(shè)計(jì)領(lǐng)域。然而,隨著芯片與軟件復(fù)雜度的不斷提升、預(yù)硅設(shè)計(jì)周期的拉長,以及全面的硬件-軟件驗(yàn)證變得愈發(fā)重要,HAV現(xiàn)已成為當(dāng)下絕大多數(shù)設(shè)計(jì)工作中不可或缺的一環(huán)。

如今,工程師們不僅要驗(yàn)證單個部件,還需確保硬件與軟件之間復(fù)雜的系統(tǒng)級交互得以有效運(yùn)轉(zhuǎn)。這其中不僅包含了對底層IP合規(guī)性的嚴(yán)格把控,還涉及到性能與功耗的細(xì)致優(yōu)化,使得整個驗(yàn)證過程成為一項(xiàng)艱巨的任務(wù)。

集成的驗(yàn)證引擎──涵蓋從各抽象層級的基于仿真的工具,到硬件輔助解決方案如仿真及基于FPGA的原型設(shè)計(jì)──為高效處理大量工作負(fù)載提供了可能,有效解決了至關(guān)重要的可擴(kuò)展性問題。在這一背景下,基于云的解決方案顯得尤為寶貴,它們能夠進(jìn)一步優(yōu)化性能與成本效率,實(shí)現(xiàn)通過結(jié)合本地與云端資源來并行處理眾多工作負(fù)載和回歸測試。

有效驗(yàn)證的核心在于能夠平滑地在不同用例間切換,自早期的快速RTL調(diào)試直至高性能軟件工作負(fù)載的驗(yàn)證。具備可配置性且能高效應(yīng)對這一系列需求的HAV平臺,對于驗(yàn)證真實(shí)世界中芯片與系統(tǒng)設(shè)計(jì)的復(fù)雜性至關(guān)重要,這些設(shè)計(jì)往往需要依托真實(shí)的工作負(fù)載來進(jìn)行測試。面對永無止境的驗(yàn)證需求,設(shè)計(jì)團(tuán)隊(duì)還需敏銳地把握每個驗(yàn)證引擎的投資回報率(ROI)。雖然不存在一種萬能的引擎能夠適配所有用例,但我們已然步入了一個新時代,在這個時代里,HAV設(shè)置在跨項(xiàng)目乃至項(xiàng)目內(nèi)部的重新配置能力已成為考量ROI的關(guān)鍵因素之一,與直接的購置成本及諸如驗(yàn)證設(shè)備功耗之類的間接成本一同被納入考量。

歸根結(jié)底,一個具備適應(yīng)性的驗(yàn)證架構(gòu)意義重大,它不僅能夠迎合多樣化的用戶需求與用例,還能保持足夠的靈活性以應(yīng)對這個不斷演進(jìn)的領(lǐng)域所提出的未來技術(shù)挑戰(zhàn)。

引領(lǐng)半導(dǎo)體設(shè)計(jì)的長期創(chuàng)新之路

作為尖端芯片設(shè)計(jì)工具與IP的領(lǐng)軍企業(yè),新思科技處于這一變革的前沿。從確保首次流片成功,到構(gòu)建支撐現(xiàn)代設(shè)備的復(fù)雜架構(gòu),我們深知硬件輔助驗(yàn)證(HAV)對于持續(xù)創(chuàng)新至關(guān)重要。

HAV提供了驗(yàn)證復(fù)雜硬件-軟件交互作用的關(guān)鍵工具與基礎(chǔ)設(shè)施,提升了系統(tǒng)與產(chǎn)品的整體質(zhì)量,并大幅縮短了產(chǎn)品推向市場的時間。此外,它有效降低了昂貴的硅晶重制成本,為探索下一技術(shù)層次鋪平了道路。在這一過程中,HAV不僅革新了設(shè)計(jì)流程,還賦予開發(fā)者們實(shí)現(xiàn)宏偉構(gòu)想所需的信心與高效。

-

IP

+關(guān)注

關(guān)注

5文章

1791瀏覽量

151693 -

軟件

+關(guān)注

關(guān)注

69文章

5137瀏覽量

89015 -

AI

+關(guān)注

關(guān)注

88文章

34553瀏覽量

276108 -

組件

+關(guān)注

關(guān)注

1文章

531瀏覽量

18344

原文標(biāo)題:硬件輔助驗(yàn)證技術(shù)HAV:開啟芯片與系統(tǒng)設(shè)計(jì)的未來之門

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

通信設(shè)備EMC整改:從測試到優(yōu)化的系統(tǒng)性解決方案

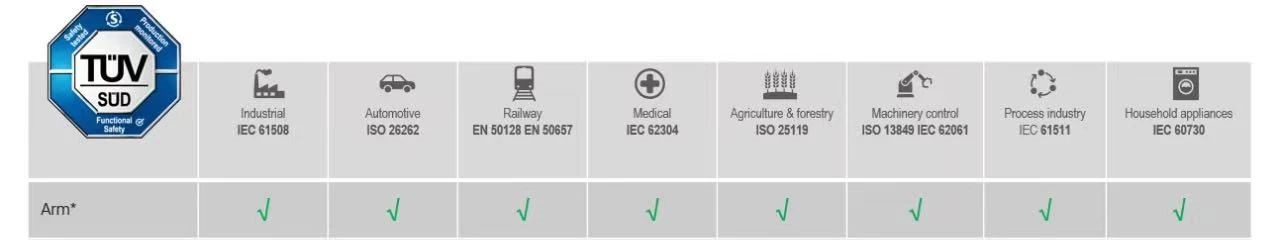

智能無人設(shè)備從IP核到系統(tǒng)的全流程功能安全問題初探

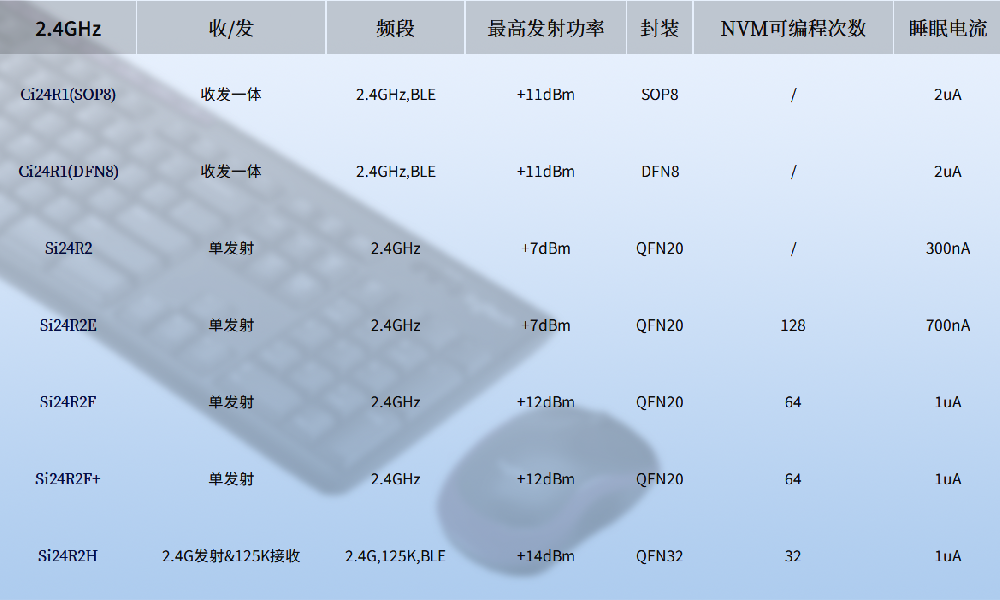

國產(chǎn) 2.4G 芯片:從技術(shù)突破到產(chǎn)業(yè)應(yīng)用的國產(chǎn)化之路

直流電機(jī)EMC整改:從驅(qū)動系統(tǒng)到整車的協(xié)同優(yōu)化

VirtualLab Fusion應(yīng)用:使用optiSLang進(jìn)行光柵優(yōu)化

如何理解芯片設(shè)計(jì)中的IP

芯耀輝:從傳統(tǒng)IP到IP2.0,AI時代國產(chǎn)IP機(jī)遇與挑戰(zhàn)齊飛

從零到一:搭建屬于自己的海外IP代理池

從匿名瀏覽到數(shù)據(jù)安全:代理IP用戶心聲全記錄

EtherCAT從站轉(zhuǎn)EtherNet/IP從站協(xié)議網(wǎng)關(guān)(JM-EIP-ECAT)

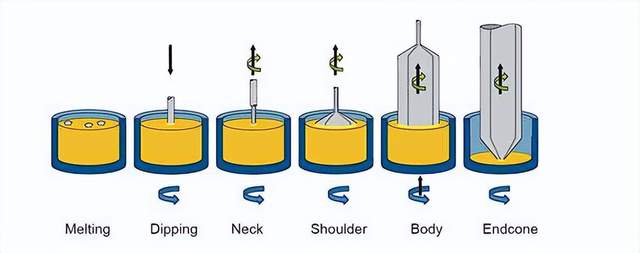

國產(chǎn)芯片原廠的出路:從風(fēng)潮到現(xiàn)實(shí)的破局之路

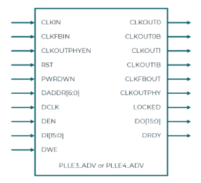

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰(zhàn)的任務(wù)!

從芯片到系統(tǒng):SOC如何重塑電子產(chǎn)業(yè)

芯片設(shè)計(jì)優(yōu)化之路:從IP到軟件定義系統(tǒng)

芯片設(shè)計(jì)優(yōu)化之路:從IP到軟件定義系統(tǒng)

評論