文章來源:半導體與物理

原文作者:jjfly686

本文簡單介紹了兩種新型的選擇性刻蝕技術——高氧化性氣體的無等離子體刻蝕和原子層刻蝕。

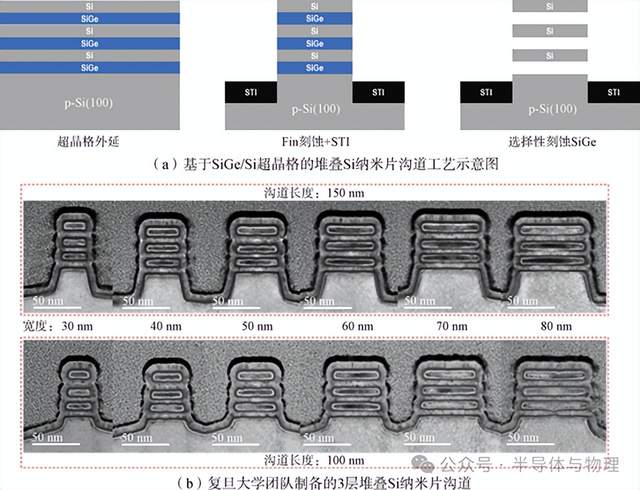

全環繞柵極晶體管(Gate-All-Around FET, GAAFET)作為一種有望替代FinFET的下一代晶體管架構,因其能夠在更小尺寸下提供更好的靜電控制和更高的性能而備受關注。在制造n型GAAFET的過程中,一個關鍵步驟是在內隔層沉積之前對Si-SiGe堆疊納米片進行高選擇性的SiGe:Si蝕刻,以產生硅納米片并釋放溝道。

本文將探討這一過程中涉及的選擇性刻蝕技術,并介紹兩種新型的刻蝕方法——高氧化性氣體的無等離子體刻蝕和原子層刻蝕(ALE),它們為實現高精度、高選擇性的SiGe刻蝕提供了新的解決方案。

GAA結構中的SiGe超晶格層

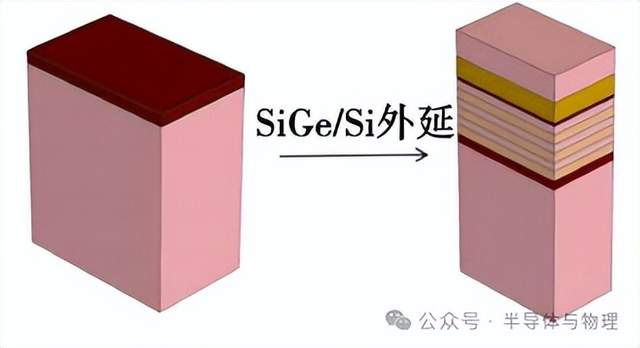

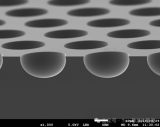

在GAAFET的設計中,為了增強器件性能,通常會在硅襯底上交替生長Si和SiGe層,形成多層結構,即所謂的超晶格。這些SiGe層不僅能夠調整載流子濃度,還能通過引入應力來改善電子遷移率。然而,在后續的工藝步驟中,需要精確地去除這些SiGe層,同時保留硅層,這就要求有高度選擇性的刻蝕技術。

選擇性刻蝕SiGe的方法

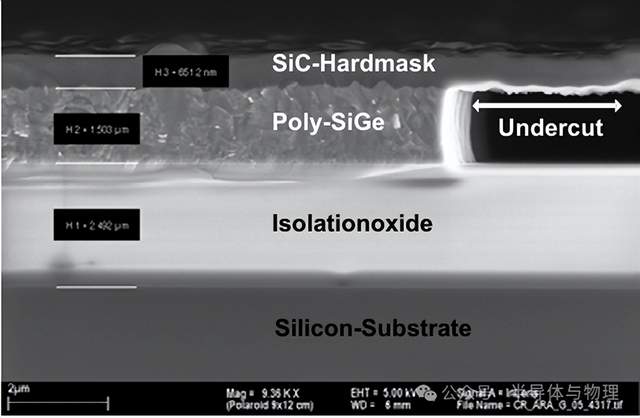

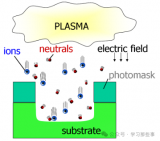

1.高氧化性氣體的無等離子體刻蝕

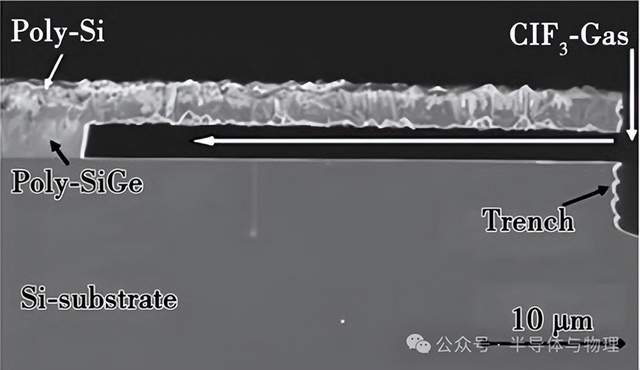

ClF3氣體的選擇:這種刻蝕方法采用具有極高選擇性的高氧化性氣體,如ClF3,SiGe:Si選擇比可達到1000-5000。并且可以在室溫下完成刻蝕,且不會造成等離子體損傷。

低溫高效:最佳溫度大約在30°C左右,實現了低溫條件下的高選擇性刻蝕,避免了額外熱預算的增加,這對保持器件性能至關重要。

干燥環境:整個刻蝕過程處于完全干燥條件下進行,消除了結構粘連的風險。

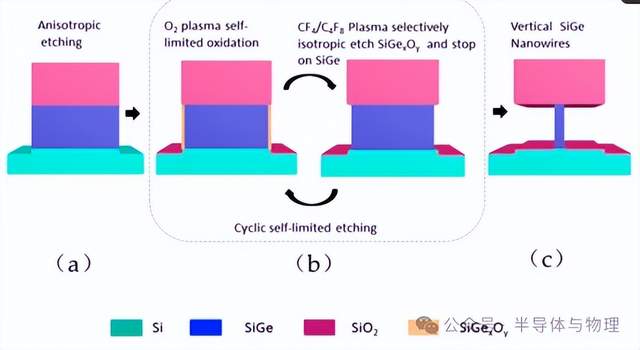

2.原子層刻蝕(ALE)

自限制特性:ALE是一種基于兩步循環工藝的刻蝕技術,首先對所要刻蝕材料表面的第一層進行改性,然后將改性層去除而不影響未改性的部分。每一步都具有自限制性,保證了每次僅去除幾個原子層的精確度。

循環刻蝕:不斷重復上述兩步工藝,直到達到所需的刻蝕深度。這一過程使得ALE能夠實現內側墻中小尺寸空腔的原子級別精度刻蝕。

聲明:本網站部分文章轉載自網絡,轉發僅為更大范圍傳播。 轉載文章版權歸原作者所有,如有異議,請聯系我們修改或刪除。聯系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

SiGe

+關注

關注

0文章

99瀏覽量

24033 -

刻蝕

+關注

關注

2文章

205瀏覽量

13406

發布評論請先 登錄

PCBA 加工必備知識:選擇性波峰焊和傳統波峰焊區別大揭秘

芯片刻蝕原理是什么

半導體選擇性外延生長技術的發展歷史

什么是高選擇性蝕刻

濕法刻蝕:晶圓上的微觀雕刻

如何提高濕法刻蝕的選擇比

晶圓濕法刻蝕原理是什么意思

半導體濕法和干法刻蝕

選擇性沉積技術介紹

晶圓表面溫度對干法刻蝕的影響

SiGe與Si選擇性刻蝕技術

SiGe與Si選擇性刻蝕技術

評論