????埃(?)作為一個長度單位,在集成電路制造中無處不在。從材料厚度的精確控制到器件尺寸的微縮優化,埃級尺度的理解和應用是確保半導體技術不斷發展的核心。

什么是埃(Angstrom)?

埃(符號:?)是一種非常小的長度單位,主要用于表示微觀領域的尺度,例如原子、分子之間的距離,或者晶圓制造中的薄膜厚度。1 ? 等于 (10^{-10}) 米,也就是0.1納米(nm)。為了更直觀地理解這個概念,我們可以通過以下比喻說明:

一根人的頭發直徑約為70,000納米,也就是700,000 ?。

如果將1米想象為地球的直徑,那么1 ? 就像是地球表面上一粒小沙子的直徑。

在集成電路制造中,埃單位的引入是因為它精確而便捷,尤其適用于描述極薄的膜層(如氧化硅、氮化硅、摻雜層等)的厚度,或者描述納米尺度的特征尺寸。隨著半導體工藝技術的進步,對厚度的控制精確到了單個原子層的水平,埃已經成為不可或缺的單位。

埃的物理意義和應用背景

埃作為長度單位,是科學研究和工業實踐中理解物質微觀性質的重要工具。以下是其關鍵物理意義:

原子和分子的尺寸量級:原子的直徑通常在0.5-3 ?之間。例如,氫原子的直徑約為0.5 ?,氧原子的直徑約為1.2 ?。這意味著埃是描述原子級別距離的理想單位。在化學中,鍵長(兩個原子核之間的平均距離)通常用埃來表示。例如,C-C鍵長約為1.54 ?。

薄膜厚度的精準控制:在集成電路制造中,薄膜的厚度往往需要達到原子級精度,例如氧化硅層的厚度可能為10 ?左右。這種精度決定了芯片的性能和可靠性。

晶體結構和晶格常數:半導體材料(如硅、砷化鎵)的晶格常數(即晶體中相鄰原子間的距離)通常用埃表示。例如,硅的晶格常數為5.43 ?。這一特性與材料的電學和機械性能密切相關。

光學和電子顯微鏡的分辨能力:高端顯微鏡的分辨率能夠達到亞埃級(即小于1 ?),從而觀測原子和分子的排列,這在晶圓缺陷分析中尤為重要。

缺的單位。

埃在集成電路制程中的應用?????

在集成電路制造中,埃單位的應用非常廣泛且重要。它貫穿了薄膜沉積、刻蝕、離子注入等多個關鍵工藝。以下對幾個典型場景進行說明:

①薄膜厚度控制

??

在半導體制造過程中,薄膜材料(如氧化硅SiO?、氮化硅Si?N?等)被用作絕緣層、掩膜層或電介質層。薄膜的厚度對器件性能有至關重要的影響:

例如,MOSFET(金屬氧化物半導體場效應晶體管)柵氧化層的厚度通常為幾納米甚至幾埃。過厚會導致器件性能下降,過薄則可能導致擊穿。

化學氣相沉積(CVD)或原子層沉積(ALD)技術能以埃級精度沉積薄膜,確保厚度符合設計要求。

②摻雜控制

離子注入技術中,注入離子的滲透深度與劑量直接影響半導體器件的性能。埃單位常被用來描述注入深度的分布情況。例如,淺結工藝中,注入深度可能僅為幾十埃。

③刻蝕精度

在干法刻蝕中,刻蝕速率和停刻時間需要精確控制到埃級別,以避免對底層材料的損傷。例如,在晶體管的柵極刻蝕中,如果刻蝕過頭,將導致性能劣化。

④原子層沉積(ALD)技術

ALD 是一種能以單原子層為單位堆積材料的技術,每次循環可能僅形成0.5-1 ?的薄膜厚度。這種技術在超薄膜層的構造中極具優勢,例如用作高介電常數(High-K)材料的柵極介質。

?

如何理解埃的尺度?

為了幫助工程師更加形象地理解埃的概念,可以用以下方式比喻:

埃與原子的關系:如果將一個原子想象成一個乒乓球,那么1 ?就相當于兩顆乒乓球之間的距離。

埃與微觀工藝的關系:假設人的頭發直徑為70,000納米,將其縮小到一顆晶體管的柵極長度(約為幾納米),那么這層柵氧化層的厚度可能只占頭發厚度的50萬分之一。

埃與人類感知尺度的對比:如果把1米比作地球,那么1 ?就如同地球表面上一粒細沙的直徑。這種極端的尺度對大多數人來說是抽象的,但對于工程師來說卻是日常思考的一部分。

為什么埃在集成電路制造中如此重要???

隨著半導體工藝進入先進節點(例如7 nm、5 nm、3 nm甚至未來的2 nm),集成電路的微縮逼近物理極限,而這一極限就體現在埃級厚度的控制上。以下是埃單位在行業中重要性的總結:

尺寸微縮驅動的需求:晶體管的特征尺寸(例如柵極長度、通道寬度等)已經達到數十埃的水平。微縮工藝要求工程師對材料的厚度和界面特性實現極高的控制。

性能和功耗的平衡:在先進制程中,柵極氧化層越薄,器件的開關速度越快,但也更容易出現漏電問題。通過精確控制埃級厚度,可以優化性能與功耗的平衡。

工藝控制能力的提升:精確的埃級控制是提升良率的關鍵。例如,在多層互連中,金屬間隙的填充、絕緣層的厚度控制均需要埃級的均勻性。

新材料和工藝的探索:隨著摩爾定律逐漸接近極限,半導體行業引入了高-K介質、二維材料(如石墨烯、MoS?)等新材料。這些材料的特性通常在埃級尺度上決定其宏觀表現。

總結。埃(?)作為一個長度單位,在集成電路制造中無處不在。從材料厚度的精確控制到器件尺寸的微縮優化,埃級尺度的理解和應用是確保半導體技術不斷發展的核心。

-

集成電路

+關注

關注

5420文章

11987瀏覽量

367537 -

半導體制造

+關注

關注

8文章

442瀏覽量

24602

原文標題:描述晶圓薄膜厚度的單位:埃

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

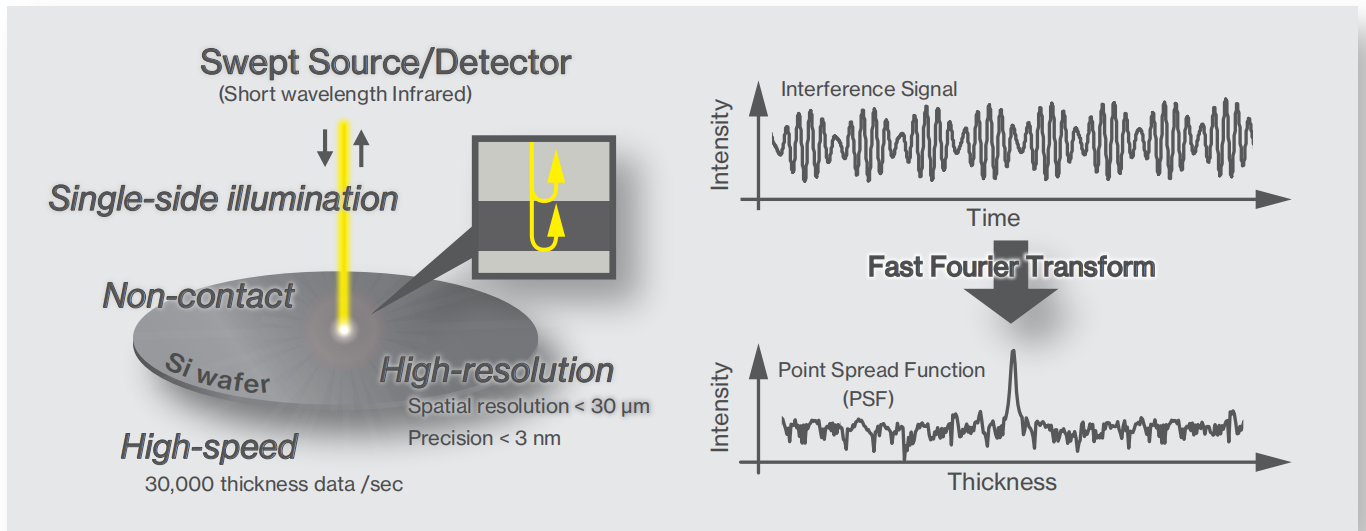

MICRO OLED 金屬陽極像素制作工藝對晶圓 TTV 厚度的影響機制及測量優化

描述晶圓薄膜厚度的單位:埃介紹

描述晶圓薄膜厚度的單位:埃介紹

評論