本文主要簡單介紹探討接觸孔工藝制造流程。以55nm接觸控工藝為切入點進行簡單介紹。

在集成電路制造領域,工藝流程主要涵蓋前段工藝(Front End of Line,FEOL)與后段工藝(Back End of Line,BEOL)。前段工藝主要用于制作晶體管,而后段工藝則專注于實現晶體管之間的金屬布線互連。其中,接觸孔工藝作為前后段工藝銜接的關鍵環節,其作用是連接晶體管有源區與第一金屬層。在大規模生產的成套工藝流程里,接觸孔工藝一旦出現缺陷,常常會成為影響良率的關鍵因素。在該工藝模塊中,接觸電阻(Contact Resistance,Rc)和套刻對準(Overlay)是需要重點關注的兩個核心部分。

電路信號的傳輸速度取決于電阻與電容的乘積,因此,在接觸孔工藝中,降低接觸電阻成為了一個至關重要的問題。針對這一問題,主要可從接觸孔材料、接觸孔關鍵尺寸等方面展開考量。

接觸孔工藝簡介

在接觸孔材料方面,用金屬鎳硅化物替代以往的金屬鈷硅化物,能夠獲得更小的接觸電阻;采用金屬鎢替換之前的金屬鋁作為接觸孔的填充材料,不僅可擁有更強的抗電遷移能力,還能實現更小的電阻率以及更高的臺階覆蓋率;在不影響填充能力的前提下,減小具有高阻特性的黏合層 Ti/TiN 的厚度,同樣可以達到降低電阻的目的。

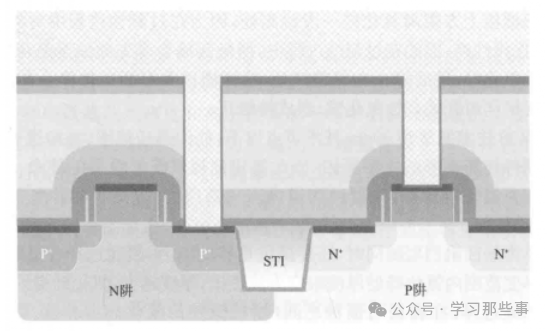

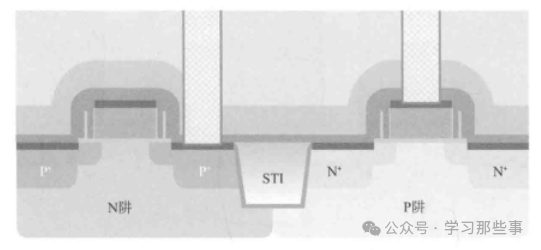

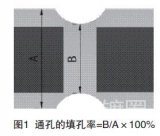

在接觸孔關鍵尺寸方面,隨著技術節點逐漸縮小,多晶硅到接觸孔的距離越來越短。減小接觸孔的關鍵尺寸,有助于減少多晶硅和接觸孔之間橋聯的問題,然而,關鍵尺寸的減小會致使接觸孔與多晶硅及有源區的接觸面積變小,進而增加接觸電阻。與此同時,降低層間介質的厚度也有助于降低電阻。所以,需要探尋合適的工藝窗口,以平衡這些因素之間的關系。光刻工藝中的套刻對準步驟,對接觸孔工藝有著較大的影響,尤其是在靜態隨機存取存儲器(Static Random - Access Memory,SRAM)區域。靜態隨機存取存儲器依靠提高晶體管密度來增加緩存容量,其設計可不遵循最小設計規則,這給工藝帶來了極大的挑戰。在靜態隨機存取存儲器區域,當接觸孔與柵極套刻對準時,若出現較大偏差,就容易導致接觸孔和柵極之間發生橋聯短路,進而使器件失效。當接觸孔與有源區套刻對準時,部分有源區上的接觸孔與有源區重疊,一旦產生對準偏差,在后續刻蝕過程中就會刻蝕掉一部分淺溝槽隔離(STI)上的氧化物,從而增加漏電,加大器件功耗。

接觸孔工藝流程

55nm 接觸孔工藝選用金屬鎢作為填充材料,在器件與第一層金屬之間采用介質材料,以此形成層間介質層(Inter - Layer Dielectric,ILD),從而實現電性隔離,并降低金屬與襯底之間的寄生電容。55nm 接觸孔工藝的具體步驟如下:

清洗:

在進行化學氣相沉積(Chemical Vapour Deposition,CVD)之前,需對晶圓表面進行清洗,以確保其表面潔凈。

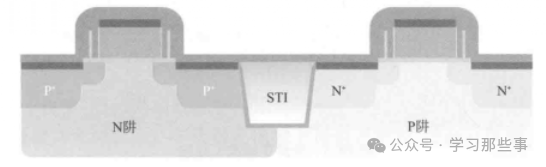

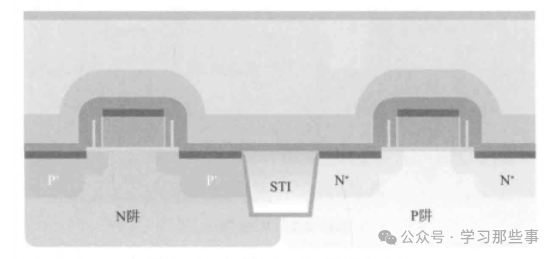

沉積具有拉應力的氮化物層:

如下圖所示,利用化學氣相沉積法沉積一層氮化物,這層氮化物既作為后續刻蝕接觸孔的刻蝕停止層,同時還能引入應力。在早期工藝中,對器件的工作速率要求相對較低,所以在這一步驟采用的是氧化物加氮化物的組合,主要目的是實現電性隔離。加入氧化層,一方面是將其作為刻蝕停止層;另一方面是因為氮化物與硅襯底的晶格常數和熱膨脹系數不匹配,氮化物與硅直接接觸會產生較大應力,容易致使硅襯底出現裂紋、大量位錯或缺陷。因此,需要在襯底上生長一層氧化物,以緩解氮化物與硅襯底之間的應力。隨著技術節點不斷縮小,對 <100> 晶向的硅片施加拉應力,能夠顯著提升其溝道的電子遷移率,進而提高器件的驅動電流。所以,在這一步驟中去除了氧化物,以充分發揮氮化物的應力作用,通過精準控制沉積工藝的各項指標來調控應力大小,有效提升 NMOS 器件的工作速率。

生長具有拉應力的氮化物

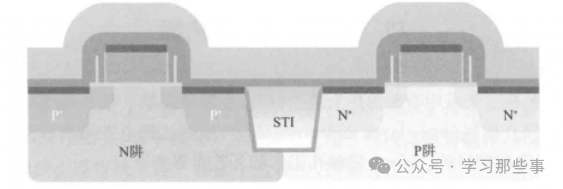

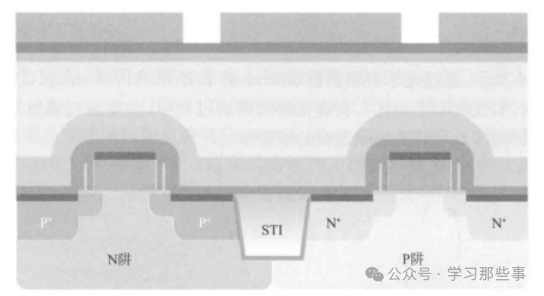

沉積磷硅玻璃:

如下圖所示,運用高密度等離子體化學氣相沉積工藝(High Density Plasma Chemical Vapour Deposition,HDPCVD)沉積磷硅玻璃(PSG),將其作為第一層層間介質層。磷硅玻璃是在未摻雜硅酸鹽玻璃(Undoped Silicate Glass,USG)中摻磷形成的,它能夠有效吸收固定離子(主要為 Na)并阻擋水汽。在該步驟中,主要從間隙填充能力(Gap Fill)、等離子體損傷、薄膜均勻性這三個方面對高密度等離子體化學氣相沉積工藝進行優化。

生長磷硅玻璃層

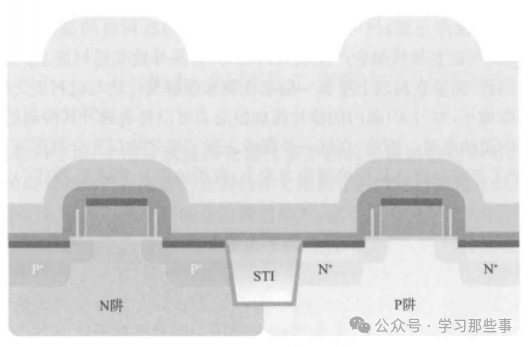

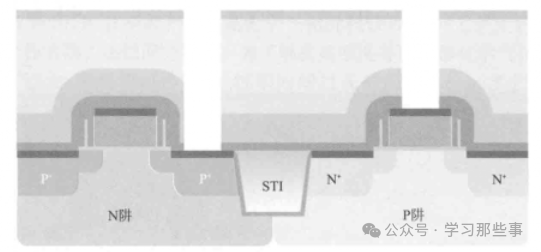

沉積 TEOS:

如下圖所示,采用等離子體增強化學氣相沉積(PECVD)工藝生長正硅酸乙酯(TEOS),將其作為第二層層間介質層。為解決高密度等離子體化學氣相沉積工藝中等離子體密度過大、薄膜均勻性欠佳、沉積時間過長的問題,55nm 工藝采用 PSG + TEOS 的組合作為層間介質。

生長正硅酸乙酯層

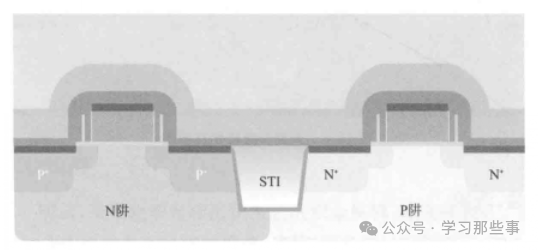

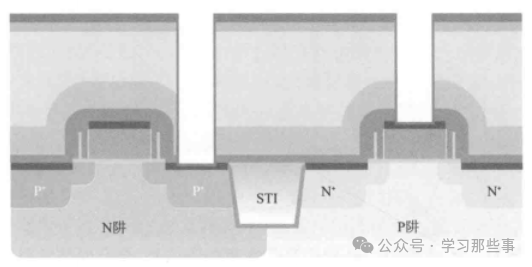

CMP:

如下圖所示,借助化學機械研磨(Chemical Mechanical Polishing,CMP)來調整層間介質層的高度,實現表面平坦化。在研磨氧化物的過程中,主要通過調節研磨時間來達到指定的介質層高度,最后清洗去除表面的研磨液。

化學機械研磨調整高度

沉積氧化物:

如下圖所示,利用等離子體增強化學氣相沉積形成一層氧化物,該氧化物可作為光刻的抗反射涂層,以減少反射,降低駐波效應,同時還能修復化學機械研磨工藝對表面造成的損傷。

生成等離子體增強的氧化物

光刻:

如下圖所示,通過光刻膠旋涂、前烘、對準與曝光、后烘、顯影、堅膜等一系列步驟,將掩模上的圖形轉移到光刻膠上。非接觸孔區域保留光刻膠,接觸孔區域的光刻膠則通過顯影去除,后續將通過刻蝕工藝形成接觸孔。

光刻形成接觸孔圖案

刻蝕、清洗:

如下圖所示,采用 CF?等氣體形成的等離子體轟擊晶圓,去除無光刻膠覆蓋區域的介質層,形成高深寬比的接觸孔。在形成接觸孔后,通過干法刻蝕和濕法刻蝕去除光刻膠和抗反射涂層,隨后將晶圓放入清洗槽中清洗,最后在物理氣相沉積(Physical Vapor Deposition,PVD)金屬前,用氬離子濺射去除表面的氧化物。

刻蝕形成接觸控圖案

沉積黏合層(Glue Layer,GL):

如下圖所示,利用物理氣相沉積工藝濺射沉積 Ti 和 TiN 層。Ti/TiN 層主要有兩方面作用:一方面,由于鎢與氧化物的黏附性較差,如果直接將鎢填充進氧化物,形成的介質層中鎢層極易脫落,因此需要 Ti/TiN 作為黏附層,防止鎢層脫落;另一方面,Ti/TiN 層作為阻擋層,能夠有效防止鎢擴散至器件有源區內,對器件性能造成損害。

沉積Ti/TiN層

沉積鎢層:

如下圖所示,采用化學氣相沉積工藝沉積金屬鎢,填充接觸孔。這個過程主要分為兩步,第一步是利用六氟化鎢(WF?)、硅烷(SiH?)和乙硼烷(B?H?)在一定溫度和壓力下反應沉積一層鎢籽晶層,第二步是利用六氟化鎢(WF?)和氫氣(H?)沉積大量的鎢。

沉積鎢層

CMP:

如下圖所示,利用化學機械研磨去除表面多余的鎢層和 Ti/TiN 層,防止鎢殘留導致不同區域的接觸孔短路,同時也使表面平坦化。正硅酸乙酯層是化學機械研磨的停止層,考慮到工藝的容忍度,當終點檢測器檢測到正硅酸乙酯的成分時,會再進行一定時間的研磨,確保鎢沒有殘留。

-

檢測器

+關注

關注

1文章

888瀏覽量

48489 -

工藝

+關注

關注

4文章

677瀏覽量

29296

原文標題:接觸孔工藝簡介

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

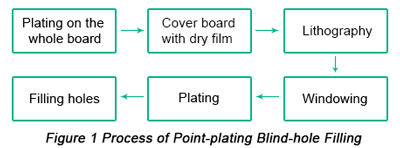

點鍍盲孔填充工藝流程簡介

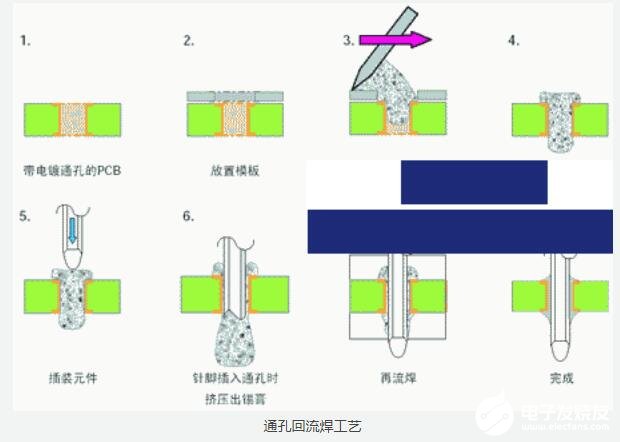

通孔回流焊工藝原理_通孔回流焊接工藝的優缺點

何時使用通孔技術工藝?

PCB導電孔塞孔工藝的實現

PCB線路板導電孔塞孔工藝的實現

互連/接觸/通孔/填充分別代表了什么

接觸孔工藝簡介

接觸孔工藝簡介

評論