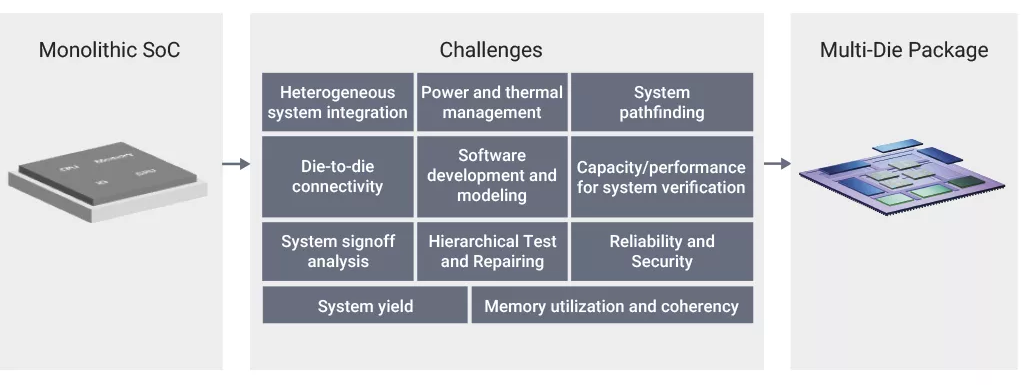

Multi-Die設計是一種在單個封裝中集成多個異構或同構裸片的方法,雖然這種方法日益流行,有助于解決與芯片制造和良率相關的問題,但也帶來了一系列亟待攻克的復雜性和變數。尤其是,開發者必須努力確保Multi-Die芯片在整個生命周期內的健康狀況和可靠性。這不僅包括對各個裸片進行測試和分析,還包括對Die-to-Die連接性以及整個Multi-Die封裝進行測試和分析。

利用新思科技Multi-Die解決方案加快創新速度

新思科技處于Multi-Die設計創新領域的前沿,我們最近與臺積公司合作,演示了兩個裸片之間通過高速UCIe(通用芯粒互連技術)規范進行通信。新思科技的監控、測試和修復(MTR) IP是此次演示的核心,展示了Multi-Die互連的制造和現場健康狀況。

接下來,我們將探討確保Multi-Die質量和可靠性所面臨的獨特挑戰,深入了解為何全面的監控、測試和修復解決方案對芯片開發者至關重要,以及新思科技和臺積公司正在采取哪些舉措來提供助力。

互連監控、測試和修復的必要性

隨著半導體變得更加復雜,即在單個封裝中集成多個異構或同構裸片,裸片(也稱為小芯片)之間有效通信和可靠互連的需求大幅增加。UCIe規范對Die-to-Die互連進行了標準化,促進了小芯片間的高速通信。然而,這些連接的高速特性要求對其進行嚴格的監控、測試和修復,以確保芯片在整個生命周期內實現無縫通信。監控信號完整性對于確保互連的整體健康狀況至關重要。通過基于嚴格算法的測試,可以發現不同類型的開路、短路以及這些高數據速率通道附近可能出現的互連間串擾問題。同樣重要的是,能夠在工藝、電壓和溫度(PVT)范圍內累積增強任何修復特征,以涵蓋不同的用例。

為了實現UCIe Die-to-Die鏈路,開發者必須解決幾個關鍵的Multi-Die健康挑戰,包括:

窄間距:UCIe高級封裝中的間距(即互連之間的距離)非常短(25-55um之間)。在芯片制造過程中,探測這些微凸塊非常困難。這就需要一種嵌入式功能,能夠進行自測而不是進行探測。

僅使用UCIe主帶和邊帶:通常,除了主帶和邊帶通道外,沒有額外的可測性設計(DFT)端口可用于單個裸片級測試。

高速信號完整性:由于UCIe通信的高速特性,保持信號完整性變得極具挑戰性。需要持續監測UCIe PHY參數,以便及時發現并糾正問題。

冗余與修復:為了提高質量、可靠性和良率,需要通過提供備用互連來實現冗余。出現故障時,備用互連可以替換有缺陷的互連,確保通信不間斷。

環境變化性:互連在不同的環境條件(如溫度和電壓)下可能表現不同。需要對在多種條件下運行的互連進行測試和修復,以確保其魯棒性。

Multi-Die健康狀況監控和可靠性綜合解決方案

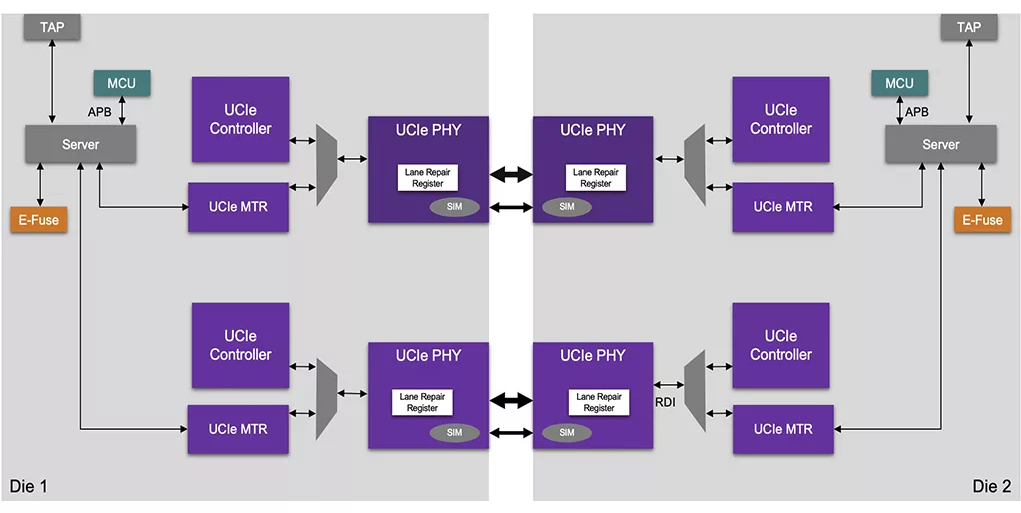

我們的MTR IP解決方案由多個協同工作的組件組成,為Multi-Die設計提供全面的健康檢查:

專用任務模式信號完整性監控:這由嵌入在UCIe高速互連通道內的信號完整性監控器(SIM)組成,用于持續監控信號完整性,實時反饋Die-to-Die通信通道的健康狀況。

內置自測(BIST)算法:這些確定性算法旨在檢測高級互連故障類型,包括因窄間距和高數據速率而可能出現的互連間串擾。

累積修復:高級UCIe提供冗余通道用于修復。每136個主通道配有12個額外的冗余通道,而在邊帶方面,4個主通道配有4個備用通道。這種冗余對于修復故障互連而不影響整體系統性能至關重要。借助這些冗余通道,MTR使用內置冗余分析(BIRA)算法進行硬修復,并將修復數據累積存儲在E-Fuse中。

通過高速接口實現高速訪問與測試(HSAT)以及自動測試向量生成(ATPG):HSAT功能有助于訪問隱藏裸片,通過功能接口實現自適應高帶寬測試。這不僅能夠縮短測試時間,還能因引腳數和測試硬件的減少而降低成本,并支持在芯片的整個生命周期內進行測試。

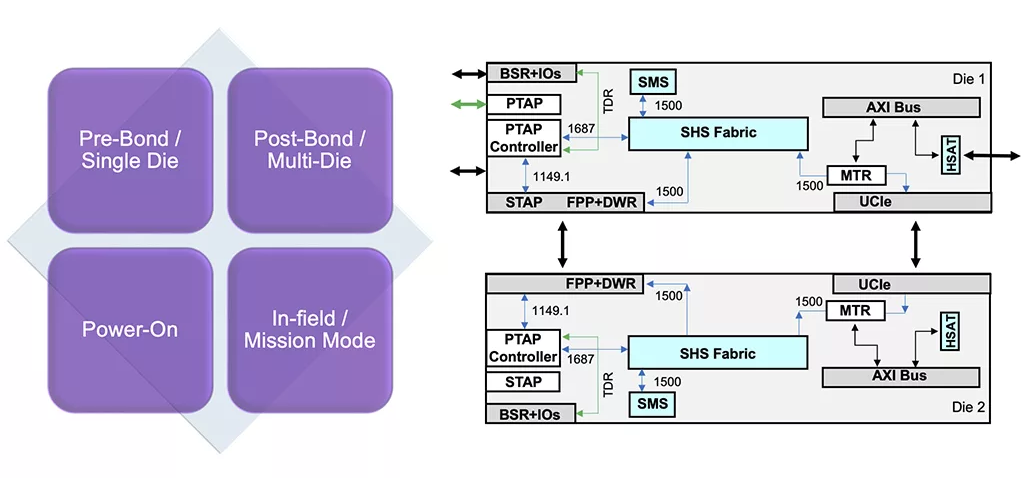

我們的MTR IP解決方案可用于多種生命周期場景:在單個裸片層面,確保單個裸片的健康狀況良好;在Multi-Die層面,這在制造堆疊芯片時尤為重要;在開機模式下,確保用戶每次在實際使用中開啟設備時,MTR都能發揮作用;以及在實時任務模式下,提供更深入的實時健康狀況檢查。前兩種場景最適用于臺積公司等代工廠,后兩種場景則適用于代工廠的客戶。

展示基于UCIe的Multi-Die進展

在小芯片峰會(Chiplet Summit)上,我們展示了采用臺積公司工藝在CoWoS-S中介層上成功實現UCIe PHY IP一次性流片成功的最新成果。此外,我們還分享了一項演示結果,該演示展示了兩個裸片通過高速UCIe Die-to-Die接口和標準GPIO接口進行通信的情況。

在第一種配置中,我們的MTR IP在兩個新思科技UCIe IP之間提供互連可靠性、測試和修復功能。在第二種配置中,SLM MTR IP支持IEEE 1838測試訪問基礎結構,允許進行裸片內通道測試。

這兩種配置都支持在每個裸片內部利用各種片上技術全面執行監控、測試、調試和修復功能,例如用于隨機邏輯塊的新思科技HSAT和SEQ IP、用于嵌入式存儲器塊的SMS IP,以及用于UCIe塊的SHS和MTR IP。這些功能覆蓋了鍵合前和鍵合后的制造階段、實際應用中的開機階段以及定期的任務健康監控。該設計展示了如何在Multi-Die封裝的整個芯片生命周期內使用上述功能,而不會在堆疊裸片時造成覆蓋率損失或向量膨脹。

我們對Multi-Die健康狀況與可靠性的承諾

新思科技致力于幫助客戶突破半導體技術的界限,并提供在整個芯片生命周期內具有超高制造良率和魯棒性的Multi-Die設計。我們針對基于UCIe的Multi-Die設計提供的SLM MTR IP解決方案就是這一承諾的最好證明,它為監控、測試和修復Die-to-Die互連提供了一個魯棒的框架。該解決方案可用于芯片生命周期的各個階段,包括設計、試制到生產和現場階段。

-

芯片

+關注

關注

459文章

52306瀏覽量

437745 -

封裝

+關注

關注

128文章

8598瀏覽量

144985 -

新思科技

+關注

關注

5文章

858瀏覽量

51307

原文標題:新思科技+臺積公司,助力Multi-Die設計全流程健康狀況和可靠性

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

西門子Tessent Multi-die解決方案實現2.5D/3D IC可測性設計自動化

西門子推出Tessent Multi-die軟件解決方案 滿足多維設計的需求

2023是否會成為Multi-Die的騰飛之年?

光子芯片公司如何輕松搞定復雜Multi-Die設計?

芯片革命:Multi-Die系統引領電子設計進階之路

設計更簡單,運行更穩健,UCIe標準如何“拿捏”Multi-Die系統?

如何成功實現Multi-Die系統的方法學和技術

VCS:助力英偉達開啟Multi-Die系統仿真二倍速

Multi-Die系統,掀起新一輪技術革命!

Multi-Die系統驗證很難嗎?Multi-Die系統驗證的三大挑戰

新思科技攜手英特爾推出可量產Multi-Die芯片設計解決方案

新思科技Multi-Die系統如何滿足現代計算需求

利用Multi-Die設計的AI數據中心芯片對40G UCIe IP的需求

利用新思科技Multi-Die解決方案加快創新速度

利用新思科技Multi-Die解決方案加快創新速度

評論