概述

具有隱含時鐘的DS1248 1024k NV SRAM為全靜態非易失RAM (按照8位、128k字排列),內置實時時鐘。DS1248自帶鋰電池及控制電路,控制電路連續監視VCC是否超出容差范圍,一旦超出容差,鋰電池便自動切換至供電狀態,寫保護將無條件使能、以防存儲器和實時時鐘數據被破壞。

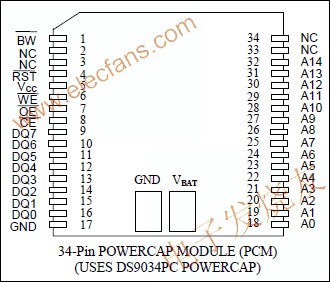

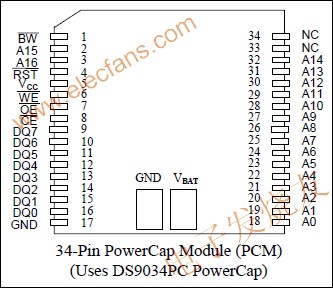

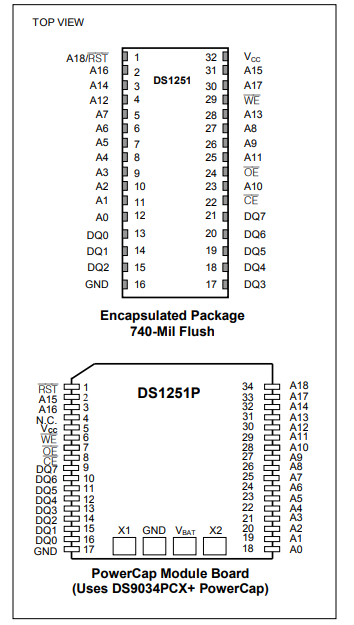

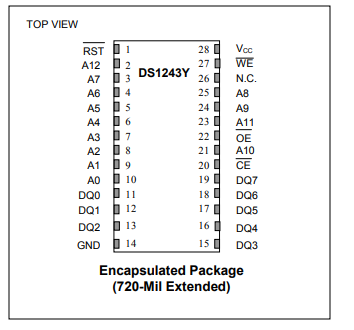

DS1248有兩種封裝:32針DIP和34針PowerCap模塊。32針DIP式模塊將晶體、鋰能源和硅集成在一個封裝中。34針PowerCap模塊板設計有觸點,用于連接到包含晶體和電池的單獨PowerCap(DS9034PCX)。這種設計允許在表面安裝過程完成后將PowerCap安裝在DS1248P的頂部。在表面安裝過程后安裝PowerCap可以防止因回流焊所需的高溫而損壞晶體和電池。PowerCap采用鍵控設計,可防止反向插入。PowerCap模塊板和PowerCap單獨訂購,并裝在單獨的容器中運輸。

數據表:*附件:DS1248 1024k NV SRAM,帶有隱含時鐘技術手冊.pdf

特性

- 實時時鐘(RTC)保持跟蹤百分之一秒、秒、分、時、星期、日、月和年

- 128k x 8 NV SRAM可直接替代易失靜態RAM或EEPROM

- 內置鋰電池維持日歷運行及保存RAM數據

- 時鐘功能對RAM操作完全透明

- 月和年決定每個月的天數,有效期至2100年

- 10%工作范圍

- 工作溫度范圍:0°C至+70°C

- 無外部電源時可保存數據10年以上

- 第一次上電前,鋰電池與電路斷開、維持保鮮狀態

- 提供DIP模塊

- 標準32引腳JEDEC引腳排列

- 提供無引線封裝

- PowerCap模板

- 表面貼裝可直接與帶有電池和晶振的PowerCap連接

- 電池可更換(PowerCap)

- 引腳兼容于DS1244P及DS1251P

引腳配置

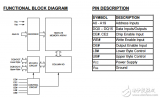

幻影時鐘操作

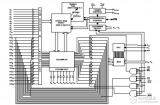

與幻影時鐘的通信是通過對64位串行比特流進行模式識別來建立的,必須通過執行包含DQ0上正確數據的64個連續寫入周期來匹配。在識別64位模式之前發生的所有訪間都指向內存。在識別建立后,接下來的64個讀取或寫入周期提取或更新幻影時鐘中的數據,并禁止存儲器訪間。

在芯片啟用、輸出啟用和寫入啟用的控制下,通過串行比特流實現與計時功能的數據傳輸。最初,使用幻影時鐘的CE和OE控制對任何存儲位置的讀取循環通過將指針移動到64位比較寄存器的第一位來啟動模式識別序列。接下來,使用SmartWatch的CE和WE控制執行64個連續的寫入周期。這64個寫入周期僅用于訪間幻影時鐘。因此,套接字中內存的任何地址都是可以接受的。然而,為訪間幻影時鐘而生成的寫入周期也在將數據寫入配套RAM中的一個位置。管理這一要求的首選方法是在RAM中只留出一個地址位置作為幻影時鐘暫存區。當執行第一寫入周期時,將其與64位比較寄存器的位0進行比較。如果找到匹配,指針將遞增到比較寄存器的下一個位置,并等待下一個寫入周期。如果未找到匹配項,指針將不會前進,所有后續寫入周期都將被忽略。如果在模式識別過程中的任何時候發生讀取循環,則當前序列將中止,比較寄存器指針將重置。如上所述,模式識別持續了總共64個寫入周期,直到比較寄存器中的所有位都匹配為止(圖1)。正確匹配64位后,幻影時鐘啟用,與計時寄存器之間的數據傳輸可以繼續進行。接下來的64個周期將導致幻影時鐘在DQ0上接收或傳輸數據,具體取決于OE引腳或WE引腳的電平。到存儲塊外部其他位置的循環可以與CE循環交錯,而不會中斷到幻影時鐘的模式識別序列或數據傳輸序列。

-

鋰電池

+關注

關注

260文章

8379瀏覽量

175181 -

時鐘

+關注

關注

11文章

1886瀏覽量

132901 -

DS1248

+關注

關注

0文章

3瀏覽量

7711

發布評論請先 登錄

DS1345W 3.3V、1024k NV SRAM

DS1330 256k非易失(NV) SRAM

DS1245W 3.3V 1024k非易失SRAM

DS1248,DS1248P 1024k NV SRAM

as7c316098b REV 1.0 1024K×16位高速CMOS SRAM

SRAM 8 Mbit (1024K x 8/512K x 16) nvSRAM帶實時時鐘

DS1248 1024k NV SRAM,帶有隱含時鐘技術手冊

DS1248 1024k NV SRAM,帶有隱含時鐘技術手冊

評論