本文作者:JonathanDodge,P.E.,Mike Zhu, Shusun Qu ,Mike Tian

隨著Al工作負載日趨復雜和高耗能,能提供高能效并能夠處理高壓的可靠SiCJFET將越來越重要。我們將詳細介紹安森美(onsemi)SiC cascode JFET,內容包括Cascode(共源共柵)關鍵參數和并聯振蕩的分析,以及設計指南。本文將繼續講解并聯的挑戰。

并聯的挑戰

在前文我們介紹并聯設計的挑戰如靜態電流失配、動態電流失配,接下來將繼續講解其他挑戰。

并聯振蕩

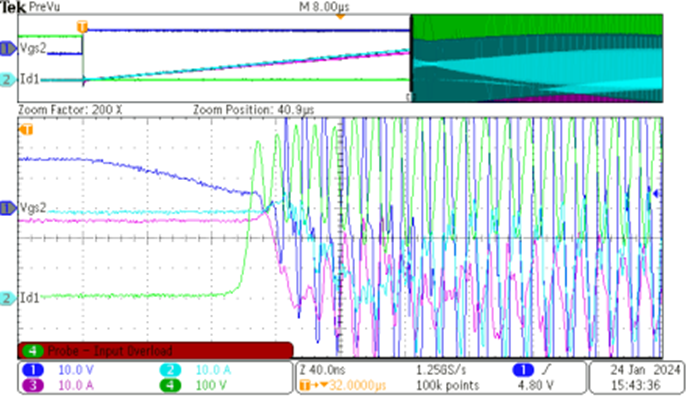

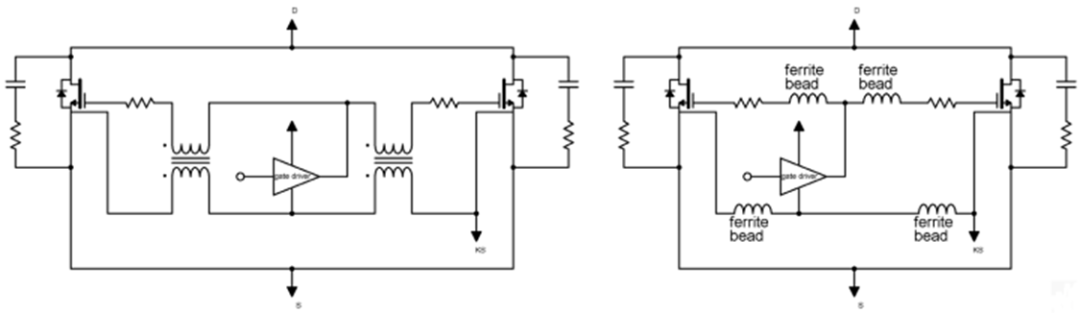

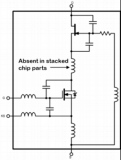

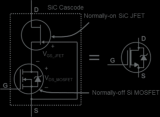

對于高增益、快速開關器件來說,并聯振蕩可能是一個問題。由于 SiC JFET cascode(簡稱cascode)內部有兩個有源器件:一個低電壓 Si MOSFET 和一個 SiC JFET,因此這尤其令人擔憂。持續的并聯振蕩(如圖 1所示)可能會因開關損耗過高而導致器件失效。

使用示波器很難觀察到振蕩。波形可能看起來很好,但在幾個開關周期內就會開始振蕩。造成這種情況的原因有很多,例如負載電流、電壓和溫度的變化。主要原因是cascode的快速開關,尤其是在大電流時更易發生,此時di/dt 和 dv/dt 的速度會更快。

圖 1 雙脈沖測試期間兩個并聯cascode進入持續并聯振蕩狀態

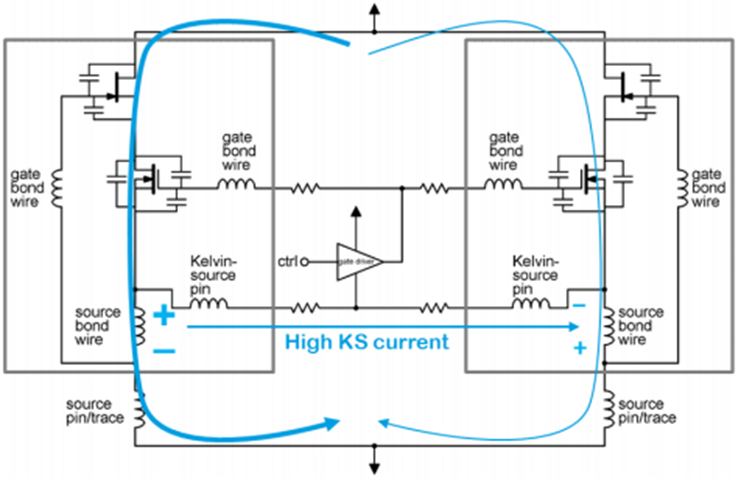

盡管很復雜,但分析具有Kelvin源引腳的兩個并聯cascode的工作情況還是很有用的,包括相關的電容和電感,如圖4所示。TO-247-3L和D2Pak-3L封裝沒有Kelvin源引腳,這種情況將在后面討論。

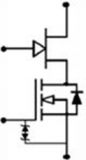

圖 2 兩個并聯cascode在動態電流失配的情況下導通

如前所述,由于閾值電壓的變化,動態電流失配實際上幾乎是不可避免的,而且電路布局的不對稱性可能會加劇這種情況。

在圖 2 中,我們可以想象有兩個cascode導通,左邊的cascode導通時間比右邊的稍早。左側cascode中的較大電流會導致左側源極電感兩端產生較高的電壓。在極端情況下,右側cascode的電流可能會暫時反向流動。無論情況如何,源極電壓失配會誘導電流流經Kelvin源連接,如圖4和圖5所示。

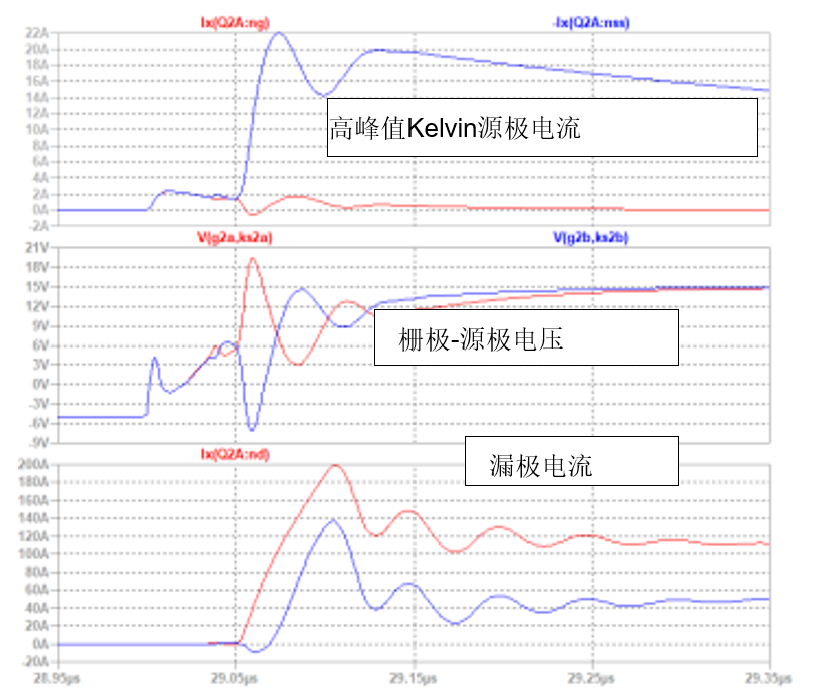

圖 3 頂部圖表:Kelvin源極電流大大超過柵極電流。中間和底部圖表:每個Cascode的 VGS和 ID

圖 3 顯示了兩個并聯 UF3SC120009K4S 帶電感負載硬開關導通的仿真結果。每個器件都有一個 680 pF 加 4.7 Ω 的漏極-源極緩沖電路(snubber)。一個cascode的 JFET 和 MOSFET 的閾值電壓比典型值低 10%,而另一個則比典型值高 10%,從而導致動態電流失配。

盡管這種情況可能發生,但概率較低。這里沒有增加額外的Kelvin源阻抗。頂部圖表顯示的Kelvin源電流峰值大大超過cascode柵極電流。理想情況下,柵極電流和Kelvin源電流在幅度上是相等的(差分)。中間圖形中的cascode柵極-源極電壓顯示出異相振鈴,這是柵源電壓不平衡的一個典型特征,在某些情況下會演變為持續的、破壞性的并聯振蕩。圖 5 的底圖顯示了漏極電流的失配,這種不匹配最終導致了Kelvin源極電流的增大。動態電流失配會穩定在接近零的狀態。

源極和/或漏極電感不匹配也會導致動態失配。當這種情況與閾值電壓的隨機變化相結合時,可能會隨機產生并聯振蕩,尤其是在使用coscode電路時,因為JFET和MOSFET的閾值電壓變化都會導致動態電流失配。

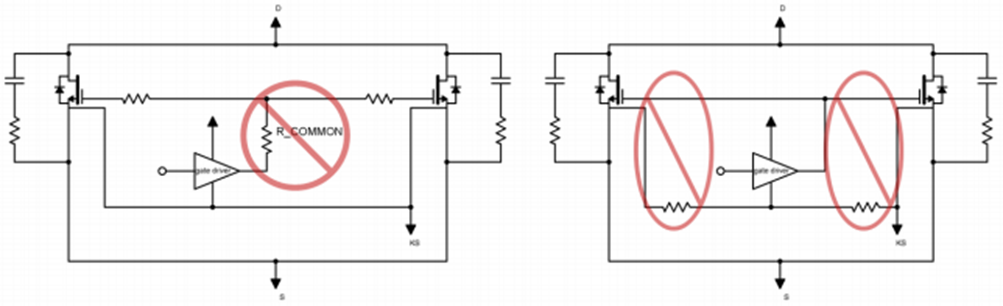

一個看似簡單的解決方案是將所有柵極環路電阻移動到每個Kelvin源連接處,或者在使用不同的導通/關斷電阻時盡量這樣做,如圖6(b)所示。然而,這可能會導致持續振蕩。

為什么會這樣呢?增加Kelvin源電阻確實可以減少峰值Kelvin源電流。然而,考慮到進出cascode MOSFET 柵漏電容的電荷是通過cascode的柵極電阻。柵極電阻越小,柵極電流峰值越高,MOSFET 的 dVDS/dt 峰值越高,JFET 的 dVGS/dt 峰值也就越高。此外,柵極電阻為MOSFET輸出電容 - 源極電感及其他LC諧振電路提供了阻尼。如果將所有柵極環路電阻移到Kelvin源連接處,則會移除cascode MOSFET柵極的阻尼,加上柵極電流與Kelvin源電流之間的巨大不匹配,這些因素結合起來會導致振蕩。

如何實現柵極阻尼最大化,同時最小化柵極電流與Kelvin源極電流的失配?首先,我們將每個cascode 的柵極電阻留在柵極連接中,而不是留在Kelvin源極連接中。我們需要最大限度地提高每個柵極的阻尼,不應使用公共柵極電阻,見圖 3(a)。將所有柵極電阻置于每個cascode 柵極連接中。并根據用戶指南推薦的柵極電阻值進行初步測試。

其次,我們可以在柵極和Kelvin源極連接處添加共模電感(common-mode choke,CMC)或差分耦合電感,如圖 5(a)所示。這將使柵極和Kelvin源極電流大小更加匹配。實驗表明,在 10 MHz 頻率下,CMC 阻抗至少為 100 Ω(如 Pulse AWCU00453226223TT2 或 Bourns SRF4530A-220Y 或類似產品)時,可消除持續振蕩。具體參數無需嚴格限定,特別是因為 CMC 對延遲時間沒有影響。

第三,并聯時必須安裝緩沖電路。除了降低開關壓擺率外,緩沖電路還能通過緩沖電阻抑制振鈴。因此,增加緩沖電路可大大降低振蕩的可能性。最后,盡可能依靠緩沖電路來設定開關速度,以最小化柵極電阻。這與直覺相反,但在《cascode 入門》中已有解釋。用戶手冊推薦的柵極電阻值為實現干凈開關的最小值。并聯器件可以共享一個共用的緩沖電路,或者每個cascode 都有獨立的緩沖電路。重要的是保持布局對稱性,并使緩沖電路連接的電感最小化。

圖 4 并聯時應避免的事項

圖 5 建議的Kelvin源并聯方法

對于共模電感來說,布線是一項挑戰。而鐵氧體磁珠則非常小巧,更容易安裝在狹小的電路板布局中,如圖 5(b)所示。與 CMC 一樣,每個Kelvin源極和柵極連接中的鐵氧體磁珠都能避免振蕩。但與 CMC 不同的是,鐵氧體磁珠會導致延遲時間明顯增加。推薦的阻抗范圍是在100 MHz下70到400 Ω,如 Bourns MU2029-301Y。與添加 CMC 一樣,除了在柵極連接中使用常規的柵極電阻外,在Kelvin源極和柵極連接中使用鐵氧體磁珠也能防止振蕩。

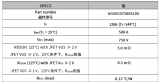

圖 6 建議的無Kelvin源并聯方法

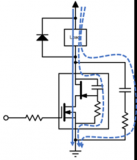

無Kelvin源引腳的器件

不帶Kelvin源引腳的器件也可以并聯。但一般來說,最好并聯帶有Kelvin源引腳的器件,因為消除了部分柵極驅動環路中的負載電流,可大大降低柵極振鈴。在沒有Kelvin源引腳的情況下,建議在柵極和柵極驅動返回連接到每個cascode 源時,都安裝一個鐵氧體磁珠,如圖 6 所示。此圖僅為概念圖。根據柵極驅動器的不同,在使用負關斷電壓時,柵極驅動環流可能會連接到柵極驅動電源,而不是直接連接到柵極驅動器。

其他設計技巧

如前所述,cascode通常需要使用緩沖電路,并聯時尤其需要。漏極-源極緩沖電路可降低開關壓擺率,從而減少產生振蕩的可能性。

直流母線電容和去耦電容必須靠近cascode,以盡量減少電感。建議在cascode旁邊安裝表面貼裝陶瓷電容(直流母線),并配合使用大容量薄膜電容器和/或鋁電解電容(作為去耦電容)。對稱電源布局非常重要。當大電流(例如大于 100 A)和高 di/dt 壓擺率時,磁場可能“推動”相鄰器件及導體中的電流偏向一側,從而引發電流失衡及其他與噪聲相關的干擾問題。

靠近柵極驅動器及其電源的地方必須有足夠的旁路電容;此處電容不足會導致振蕩。建議使用表面貼裝陶瓷電容器。

柵極走線可以較長,而且由于我們處理的開關頻率一般不在 MHz 范圍內,因此即使走線的長度不同也不會有影響。不過,柵極走線必須屏蔽,最好在相鄰電路板層上設置電源層。切勿讓柵極走線跨越電源層邊界。

未完待續,后續推文將講解演示和測試結果。

-

并聯

+關注

關注

5文章

247瀏覽量

35962 -

安森美

+關注

關注

32文章

1781瀏覽量

92916 -

JFET

+關注

關注

2文章

180瀏覽量

22642 -

SiC

+關注

關注

31文章

3180瀏覽量

64591 -

靜態電流

+關注

關注

3文章

375瀏覽量

21423

原文標題:SiC JFET并聯的五大難題,破解方法終于來了!

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

安森美SiC Combo JFET的靜態特性和動態特性

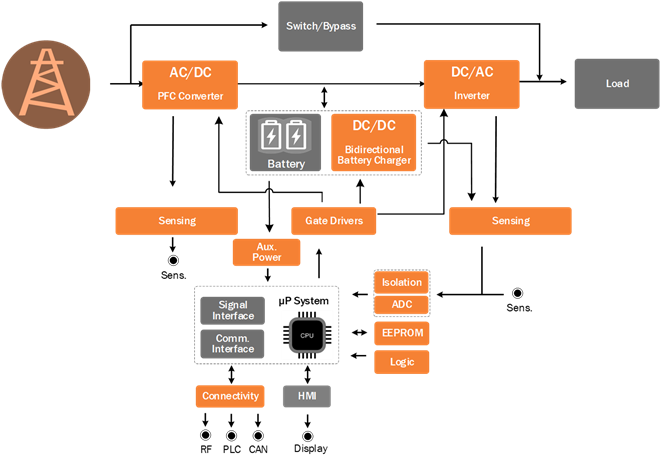

安森美豐富的SiC方案解決新一代UPS的設計挑戰

安森美SiC Cascode JFET的背景知識和并聯設計

安森美SiC Combo JFET技術概覽和產品介紹

安森美SiC cascode JFET并聯設計的挑戰

安森美SiC cascode JFET并聯設計的挑戰

評論