在芯片設計的世界里,有一種被稱為"火眼金睛"的技術,它就是DFT(Design for Testability,可測性設計)。今天,就讓我們一起揭開這項技術的神秘面紗,看看它是如何成為芯片質量的守護神的。

DFT:芯片質量的守護神

DFT,全稱Design for Testability,即可測性設計。它是一種在芯片設計階段就考慮測試問題的技術,目的是為了提高芯片的可測試性,確保芯片在制造過程中能夠被有效地檢測和診斷。把有缺陷的芯片篩選出來,防止有缺陷的芯片流入到客戶手上。同時考慮成本和收益,向量覆蓋率越高,越有利于篩選出有缺陷的芯片。

DFT的工作原理

DFT的工作原理主要基于掃描鏈(Scan Chain)、內置自測試(BIST,Built-In Self-Test)、IO測試與邊界掃描(Boundary Scan)三種技術。

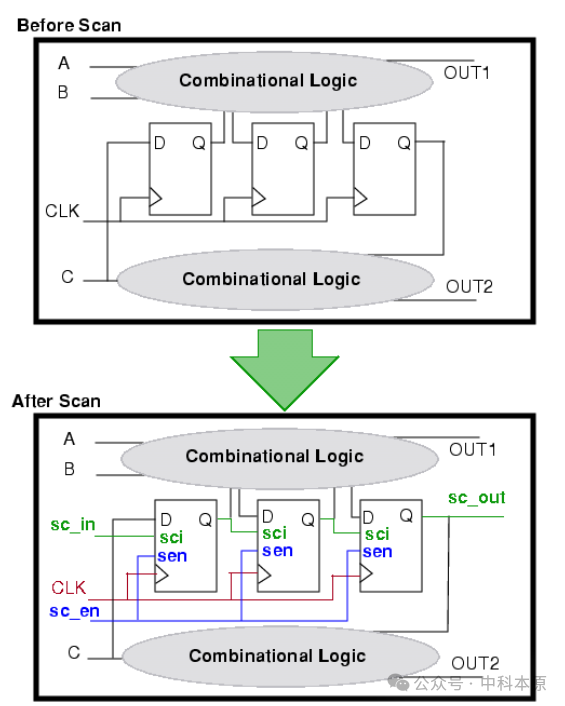

掃描鏈(Scan Test):通過插入掃描鏈(Scan Chain),使得內部邏輯狀態都可控制,既控制內部邏輯的輸入,也控制內部邏輯的輸出,生成測試向量檢測實際輸出與期望輸出是否一致,來篩選出有Stuck-at故障、transition故障等的芯片。在測試模式下,我們可以通過這條鏈將測試數據輸入芯片,并讀取芯片的輸出數據,從而檢測芯片的功能是否正確。

圖1 Design Before and After Adding Scan

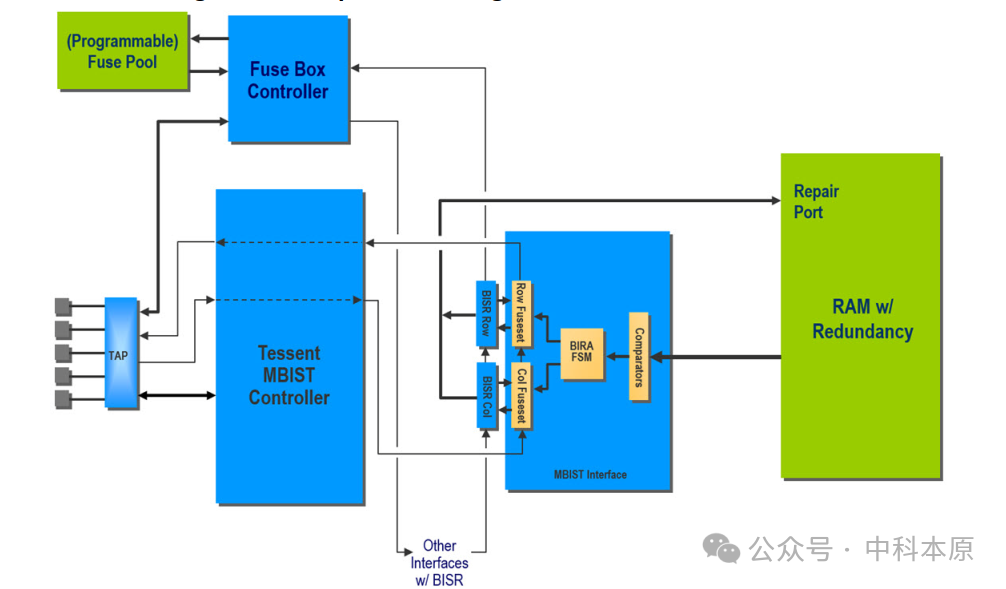

內置自測試(mbist):內置自測試是一種在芯片內部集成測試電路的技術。它可以在芯片工作時自動進行測試,無需外部測試設備的參與。針對SRAM、DRAM等存儲器單元,通過旁路邏輯和BIST算法檢測物理缺陷(如短路、斷路),篩選出有故障的芯片。這種技術特別適用于檢測芯片的存儲器和邏輯電路。

圖2 Configuration with BISR Controller

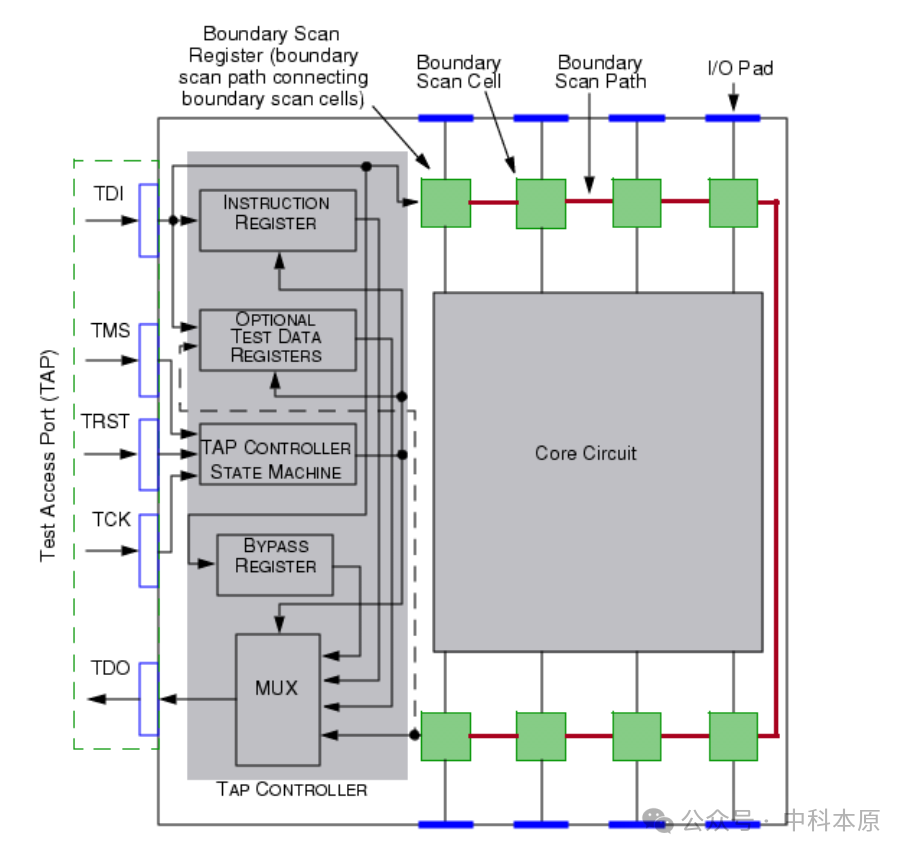

IO測試與邊界掃描(Boundary Scan) :驗證芯片引腳連接性,篩選出管腳有制造缺陷的芯片。通過以上測試,在晶圓未切割前進行初步測試,篩選出存在制造缺陷的芯片,避免后續封裝成本的浪費。這個測試原理就和EDA驗證一樣,都是通過golden值來判斷邏輯的正確性

圖3 Boundary Scan Architecture

DFT的應用

DFT技術在芯片設計中的應用非常廣泛。無論是處理器、存儲器,還是各種專用芯片,都離不開DFT的支持。

中科本原實時控制系列DSP芯片憑借其完善的DFT架構,確保了芯片在復雜應用場景下的高可靠性和穩定性。具體來說,DFT設計通過在芯片內部集成多種測試機制,如掃描鏈、內建自測試(BIST)和邊界掃描(Boundary Scan),能夠在芯片制造和運行過程中實時監測和診斷潛在故障。這種設計不僅提高了芯片的可測試性,還顯著降低了生產測試成本和時間,同時增強了芯片在高溫、高濕、強電磁干擾等惡劣環境下的抗干擾能力。此外,DFT設計還支持芯片的全生命周期管理,從設計、制造到現場應用,均可通過高效的測試手段確保芯片性能的一致性,從而滿足工業控制、汽車電子、航空航天等對可靠性要求極高的領域需求。

DFT的未來

隨著芯片技術的不斷發展,DFT技術也在不斷進步。未來的DFT技術將更加智能化,能夠自動識別和診斷芯片的問題。同時,DFT技術也將更加高效,能夠在更短的時間內完成芯片的測試。

將來,中科本原也會在DSP系列芯片的DFT設計中不斷地進行突破和創新,設計出低功耗、高效率的DFT方案,滿足不同場景對芯片的實時性和能效的高要求。

結語

DFT技術,這個芯片設計中的"火眼金睛",以其獨特的方式守護著芯片的質量。它讓我們能夠在芯片設計階段就預見并解決問題,確保芯片的穩定性和可靠性。隨著科技的進步,DFT技術也將不斷進化,為芯片設計帶來更多的可能性。讓我們期待中科本原在DFT設計領域的無限可能,不僅為自身產品賦予更高的競爭力,也為推動國產芯片的崛起貢獻力量。

-

芯片設計

+關注

關注

15文章

1073瀏覽量

55510 -

DFT

+關注

關注

2文章

233瀏覽量

23278

原文標題:

文章出處:【微信號:中科本原,微信公眾號:中科本原】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

淺談DFT可測性設計的工作原理

淺談DFT可測性設計的工作原理

評論