文章來源:學習那些事

原文作者:小陳婆婆

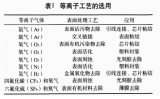

隨著集成電路特征尺寸的縮小,工藝窗口變小,可靠性成為更難兼顧的因素,設計上的改善對于優化可靠性至關重要。本文介紹了等離子刻蝕對高能量電子和空穴注入柵氧化層、負偏壓溫度不穩定性、等離子體誘發損傷、應力遷移等問題的影響,從而影響集成電路可靠性。

集成電路可靠性是產品壽命、穩定性和性能的關鍵, 晶圓制造階段的可靠性問題主要源于工藝步驟對器件的潛在損傷。 等離子體蝕刻工藝對集成電路可靠性有廣泛且決定性的影響,本文分述如下:

可靠性與失效時間

等離子體蝕刻對高能量電子和空穴注入柵氧化層(HCl)的影響

等離子體蝕刻對負偏壓溫度不穩定性(NBTI)的影響

等離子體蝕刻對等離子體誘發損傷(PID)的影響

等離子體蝕刻對應力遷移(SM)的影響

1、可靠性與失效時間

在超大規模集成電路時代,可靠性設計必須貫穿于IC開發的每個過程,這包括設計、工藝開發、制造和封裝等各個階段,只有全面考慮,新技術運用時的可靠性才能得到一定保證。隨著集成電路特征尺寸的縮小,工藝窗口變小,可靠性成為更難兼顧的因素,設計上的改善對于優化可靠性至關重要。

1. 可靠性與時間的關系:

產品的可靠性通常是隨時間遞減的函數,即工作時間越長,可靠性越低。

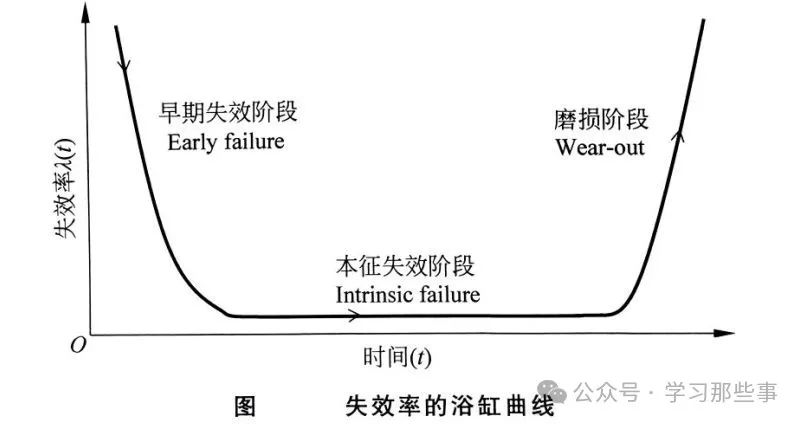

圖1 失效率的浴缸曲線

2. 規定條件對可靠性的影響:

產品的可靠性水平和壽命在不同工作條件下會有所不同,這些條件包括環境條件、維護條件和操作方法等。

3. 可靠性與質量的不同:

器件的可靠性與質量是兩個不同的概念,質量是器件與時間無關的屬性,而可靠性則與器件隨時間的退化相關。

4. 失效時間的定義:

當器件的重要參數退化到不能正常工作時,器件失效,此時對應的時間稱為失效時間。

失效時間與壽命不同,壽命強調在規定條件下(一般為工作條件),而失效時間不一定。

5. 失效時間與應力的關系:

器件的最終失效時間不僅與器件的材料性能和微結構有關,也取決于器件承受的電場、溫度、化學環境等應力的大小。

6. 失效時間和應力的建模:

對失效時間和應力的建模非常關鍵,模型直接決定了從高應力水平下的失效時間外推到低應力水平下的失效時間長短。

7. 威布爾失效率:

威布爾失效率可能隨時間增大、減小或保持不變,這取決于威布爾分布的參數。

當參數等于1時,威布爾失效率是常數,與時間無關。當參數小于1時,威布爾失效率隨時間減小。當參數大于1時,威布爾失效率隨時間增大。

2、等離子體蝕刻對HCI的影響

在工藝可靠性領域,HCI(高能量電子和空穴注入柵氧化層)是導致器件性能退化的重要因素。這種注入過程會產生界面態和氧化層陷阱電荷,進而造成柵氧化層的損傷。隨著損傷的累積,器件的電流電壓特性將發生變化,當這些變化超過一定限度時,器件將失效。

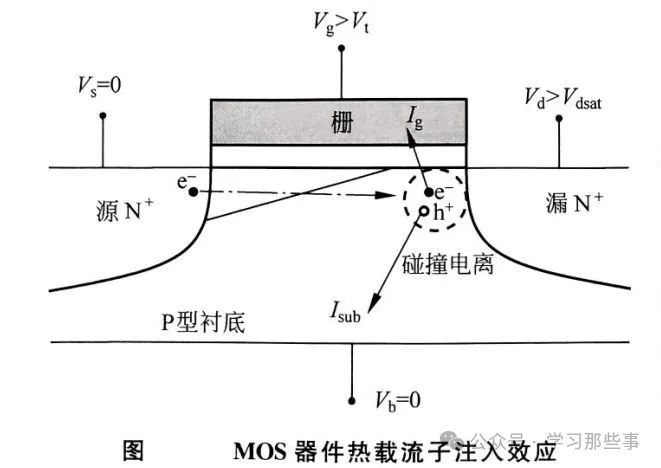

熱載流子注入效應示意圖:

圖2 MOS器件熱載流子注入效應

上圖展示了MOSFET器件的熱載流子注入效應示意圖,直觀呈現了熱載流子如何對柵氧化層造成損傷。

為了抑制熱載流子效應,可以采取以下措施:選擇合適的源漏離子注入濃度和襯底注入濃度;使用輕摻雜漏區(LDD)方法,該方法已被證明能有效抑制熱載流子效應。

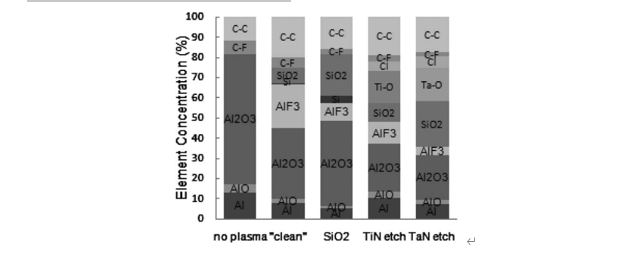

等離子體蝕刻對HCI性能的影響:

研究表明,等離子體相關工藝損傷后的柵極氧化層,其HCI性能明顯惡化。這是因為等離子體工藝過程中,柵氧中會流過一定的電流,這個充電電流會造成新的氧化層陷阱和界面態。當熱載流子注入這些受損區域時,更容易導致氧化層的進一步損傷。

3、等離子體蝕刻對NBTI的影響

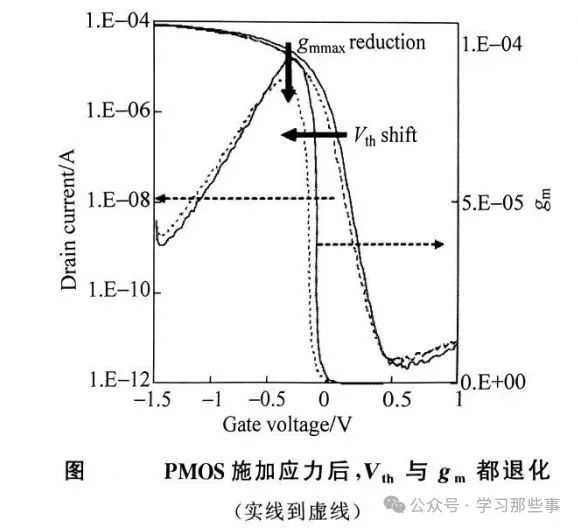

NBTI(負偏壓溫度不穩定性)是PMOS器件在柵極負偏壓和較高溫度條件下工作時,其器件參數(如閾值電壓Vth、跨導gm和飽和漏電流Idsat等)發生不穩定性的現象。

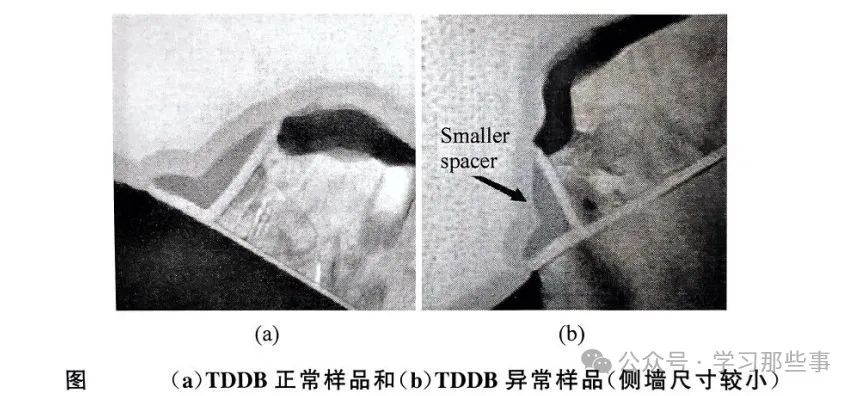

圖3 (a)TDDB正常樣品和(b)TDDB異常樣品(側墻尺寸較小)

對于NMOS器件,則對應的是PBTI(正偏壓溫度不穩定性)

圖4 PMOS施加壓力后,Vth與gm都退化(實線到虛線)

NBTI效應的解釋模型:

反應-擴散模型很好地解釋了NBTI效應。在該模型中,PMOS器件在負柵偏壓下,SiO2層中的電場方向為離開界面方向。如果Si-H鍵斷裂,就會釋放一個H+離子,留下帶正電的界面態。H+離子在電場作用下向SiO2中漂移,增加了氧化層陷阱的數量。這些界面態與陷阱導致半導體器件參數的改變。當停止施加應力(即電場降為0)時,部分H+離子會產生回流,使器件發生部分恢復,但完全恢復是不可能的,因為部分H離子會在SiO2柵電介質層內發生還原反應。

NBTI退化的飽和現象:

由于Si-H鍵的數量是有限的,隨時間增加,未斷的Si-H數目減少,Si-H斷裂引起的退化率也不斷減小,最后趨近于零,這就是NBTI退化的飽和現象。

引起NBTI的物質與改善方法:

氫氣和水汽是引起NBTI的兩種主要物質。為了減小NBTI效應,必須降低Si-SiO2界面處的初始缺陷密度并且使水不出現在氧化層中。將氘注入Si-SiO2界面來形成Si-D鍵是一個改善NBTI的有效方法。

等離子體損傷對NBTI的影響:

經過等離子體損傷(PID)后的器件,其NBTI性能會發生退化。因為電荷損傷導致了更高的界面態密度,盡管后續的退火過程有可能將其鈍化,但這些高的初始界面態密度導致了更高的NBTI退化。因此,NBTI可以作為檢測潛在等離子體損傷的有效手段。

退火工藝對NBTI的影響:

研究表明,純H2退火比N2/H2混合氣體對改善NBTI幫助更大。因為純H2有更高的H2含量,其到達Si-SiO2界面的H更多,對懸掛鍵的鈍化作用更明顯。然而,退火時間有明顯的飽和效應,當退火時間大于一定值后,延長退火時間并不能進一步增加NBTI失效時間。過量的H和界面態形成有緊密聯系,所以當太多的H漂移到達Si-SiO2界面時,會與已鈍化后的Si-H鍵中的H結合形成H2,而遺留下新的懸掛鍵,從而導致NBTI性能退化。

偽柵去除工藝對NBTI的影響:

在偽柵去除工藝中,HBr氣體的解離生成的H活性離子會損傷柵電介質,影響NBTI。使用同步脈沖等離子體可以降低HBr的解離率,明顯改善NBTI,且不影響其他性能。在偽柵去除后的光阻去除工藝中,更高H2含量的N2/H2灰化工藝能使NBTI失效時間增加一個數量級。

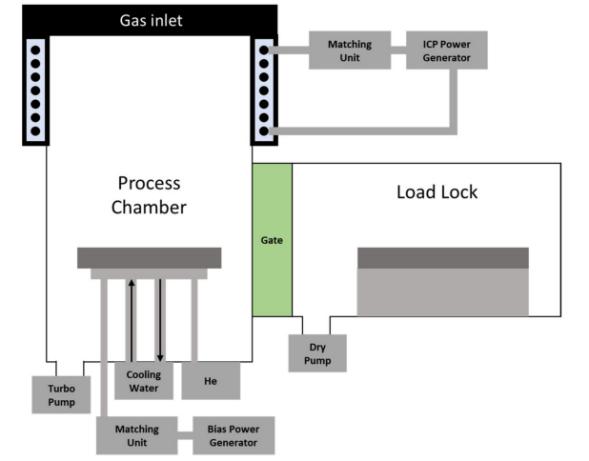

4、等離子體蝕刻對PID的影響

等離子體誘發損傷(PID)是集成電路制造中一個關鍵問題,尤其在各式各樣的等離子體工藝中,MOSFET器件易受損傷而導致性能偏移。PID的主要機理包括:

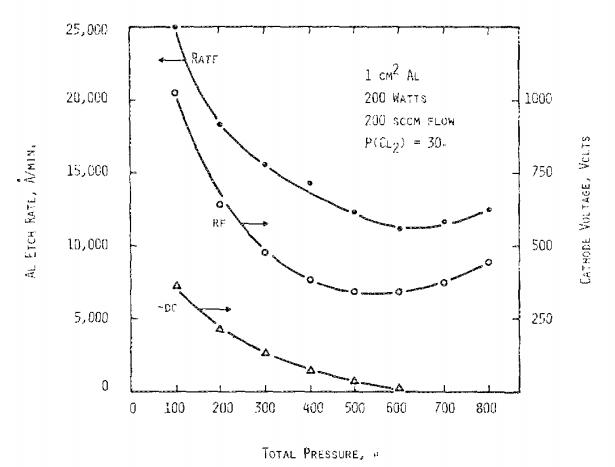

1. 等離子體密度:

高的等離子體密度意味著更大的電流,容易引發PID問題。當等離子體密度增加時,電荷充電效應增強,導致器件損傷加劇。例如,減小ICP金屬蝕刻反應腔室高度會顯著增強晶圓表面電場強度,從而增加PID風險。

2. 等離子體局部不均勻性:

在非均勻等離子體中,局部范圍內的電勢不均衡會在晶圓表面產生電流路徑,引起柵氧化層損傷。

3. 電子遮蔽效應(ESE):

等離子體中電子的方向性較差,容易被光阻遮蔽,導致正離子在蝕刻前端聚集,形成對器件的正電勢,引發PID。

圖5 (a)電子遮蔽效應和(b)反向電子遮蔽效應

4. 反向電子遮蔽效應(RESE):

在圖形空曠區域,電子的各向同性導致部分電子被要蝕刻的金屬側壁收集,而離子不會,從而在金屬側壁形成負電勢,對器件造成損傷。

5. 真空紫外線輻射(VUV):

等離子體放電時產生的大量VUV光子會在柵氧化層中產生光電流,損傷器件。采用帶隙比氧化硅窄的氮化硅層能有效阻擋VUV,保護柵氧化層。

PID的程度可以通過柵極漏電流來表征。

圖6 (a)PID的測試方法:柵極漏電流和(b)PID的測試結果

當接收天線面積與器件大小的比值(天線比)越大時,器件受到的損傷越嚴重。電路設計時,避免過高的天線比、采用金屬跳層或使用保護二極管將電荷引入襯底能有效抑制PID影響。

不同等離子體工藝對PID的影響各異。例如,第一金屬層的電介質蝕刻在很小的接觸孔天線比時就可能產生PID問題,而高層金屬要到幾千的天線比時才產生PID問題。過蝕刻時間、電源頻率等因素也會影響PID。在偽柵去除工藝中,由于等離子體直接接觸高k柵介質層上的功函數金屬,氫離子對柵介質層的損傷大大增加。

為了應對PID挑戰,業界開發出了在偽柵去除后再沉積高k柵介質層的工藝,以及先用等離子體蝕刻一部分再用化學溶劑去除剩余部分的方法,有效避免了等離子體蝕刻引起的柵介質層損傷。

5、等離子體蝕刻對SM的影響

等離子體蝕刻對SM(應力遷移)的影響主要體現在以下兩個方面:

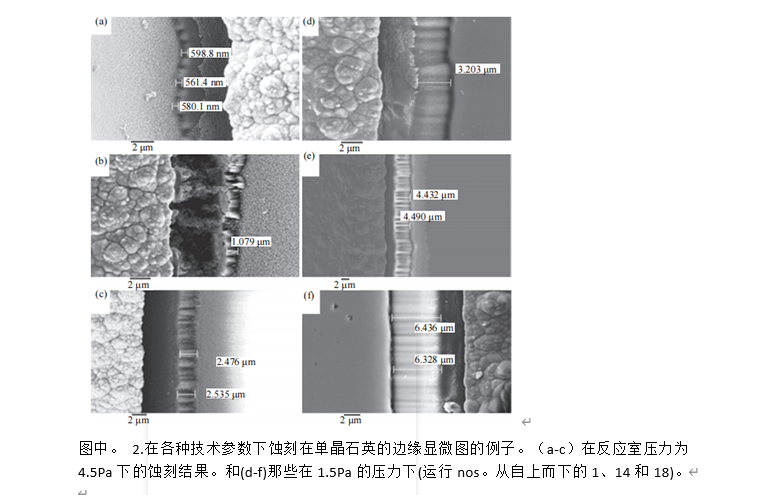

蝕刻后通孔的形貌

蝕刻工藝后,通孔的形貌對后續的金屬填充和應力遷移行為有著重要影響。如果蝕刻過程中,溝槽和通孔連接處出現了小柵欄狀形貌,這種不規則的形貌會導致銅填充時在這些區域出現空洞。

圖7 通孔底部空洞導致接觸電阻上升

這些空洞會成為應力集中的點,從而在應力遷移過程中加速空洞的擴展,最終導致電路的早期失效。因此,控制蝕刻工藝以獲得良好的通孔形貌是防止應力遷移的重要措施之一。

通孔底部的聚合物殘留及銅表面處理工藝

蝕刻后,通孔底部可能會殘留一些聚合物。這些聚合物殘留物不僅會影響后續的金屬填充效果,還可能成為應力遷移過程中的缺陷源。此外,通孔底部的銅表面狀態也對應力遷移行為有顯著影響。如果銅表面存在氧化物或其他污染物,會加速應力遷移過程中的空洞形成和擴展。

為了改善通孔底部的聚合物殘留和銅表面狀態,通常采用蝕刻后處理(Post Etch Treatment, PET)工藝。有研究發現使用N2/H2氣體的PET比CO2能更好地清除通孔底部的聚合物殘留,并且對通孔底部銅進行還原,從而顯著提高了SM性能。

圖8 (a)不同PET對通孔底部聚合物的清理能力以及(b)相對應的SM測試結果

這是因為N2/H2氣體能夠有效地與聚合物殘留物反應,將其轉化為可揮發的物質,并通過氣流將其帶走。同時,H2還能還原銅表面,去除氧化物和其他污染物,從而改善了銅表面的狀態。

等離子體蝕刻對SM的影響主要體現在通孔形貌和通孔底部的聚合物殘留及銅表面處理工藝上。為了獲得良好的電路性能和可靠性,需要嚴格控制蝕刻工藝和PET工藝參數,以獲得良好的通孔形貌和清潔的銅表面。

-

集成電路

+關注

關注

5420文章

12002瀏覽量

367697 -

等離子體

+關注

關注

0文章

129瀏覽量

14553 -

晶圓

+關注

關注

52文章

5134瀏覽量

129350 -

蝕刻工藝

+關注

關注

3文章

52瀏覽量

11916

原文標題:等離子體蝕刻工藝對集成電路可靠性影響

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

金屬蝕刻殘留物對對等離子體成分和均勻性的影響

等離子體蝕刻和沉積問題的解決方案

PCB多層板等離子體處理技術

PCB電路板等離子體切割機蝕孔工藝技術

PCB板制作工藝中的等離子體加工技術

PCB多層板等離子體處理技術

低溫等離子體廢氣處理系統

TDK|低溫等離子體技術的應用

等離子體應用

石英單晶等離子體蝕刻工藝參數的優化

精確跟蹤芯片蝕刻過程,用高分辨率光譜儀監測等離子體

等離子體清洗工藝的關鍵技術 等離子體清洗在封裝生產中的應用

等離子體蝕刻工藝對集成電路可靠性的影響

等離子體蝕刻工藝對集成電路可靠性的影響

評論