Compute Express Link(CXL)于2019年首次發(fā)布,是處理器與AI加速器、內(nèi)存緩沖區(qū)、智能網(wǎng)絡(luò)接口卡、持久性存儲器和固態(tài)驅(qū)動器等設(shè)備之間的開放式行業(yè)標(biāo)準(zhǔn)互連技術(shù)。作為一種行業(yè)標(biāo)準(zhǔn)接口,CXL提升了不同制造商硬件組件之間的互操作性,減少了兼容性問題,為數(shù)據(jù)中心硬件市場帶來了更多樣化且更具競爭力的發(fā)展環(huán)境。

盡管該標(biāo)準(zhǔn)推出至今僅短短5年,然而在此期間,我們所處的世界已發(fā)生諸多變化。其中,數(shù)據(jù)中心與高性能計算環(huán)境工作負(fù)載的持續(xù)增長尤為關(guān)鍵,這為改善人類生活的機(jī)器學(xué)習(xí)與人工智能解決方案的廣泛應(yīng)用提供了有力支撐。

CXL的核心在于提供一致性與內(nèi)存語義,其帶寬能夠隨PCIe擴(kuò)展,同時實現(xiàn)遠(yuǎn)低于PCIe的延遲。在本文中,我們將進(jìn)一步介紹開發(fā)者如何借助符合規(guī)范的CXL IP,緊跟技術(shù)進(jìn)步,滿足市場需求和持續(xù)發(fā)展的行業(yè)標(biāo)準(zhǔn)。本文將介紹CXL 3.1標(biāo)準(zhǔn)的最新更新內(nèi)容,包括新增的安全特性,以及如何持續(xù)為下一代基礎(chǔ)結(jié)構(gòu)提供內(nèi)存池功能。

CXL標(biāo)準(zhǔn)的演進(jìn)歷程

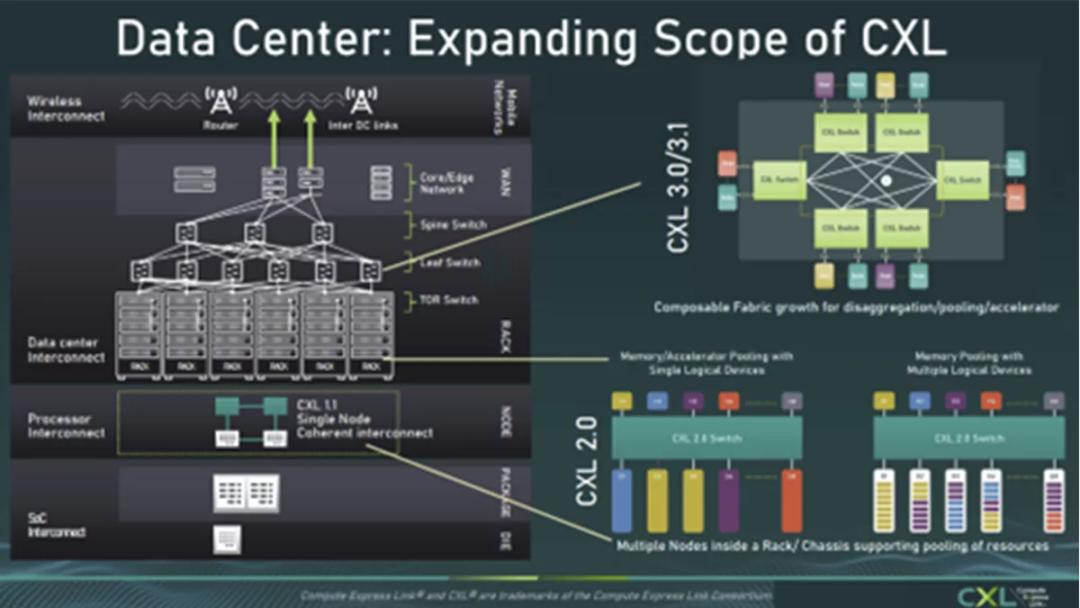

從CXL 2.0到CXL 3.x的演進(jìn),標(biāo)志著在滿足行業(yè)需求方面取得了重大進(jìn)展。對更高速度的需求是推動CXL向3.x演進(jìn)的主要驅(qū)動力之一,這與PCIe 6.x的發(fā)展方向一致。此外,CXL正朝著更對稱的一致性模型轉(zhuǎn)變,這使得連接到CXL的設(shè)備能夠生成內(nèi)存周期,并更高效地相互通信。這一改進(jìn)突破了以主機(jī)為中心的傳統(tǒng)方法,有助于實現(xiàn)在不同設(shè)備之間實現(xiàn)更靈活、高效的內(nèi)存利用。

始終不變的是,CXL一直是關(guān)鍵的互連技術(shù),能夠在CPU、加速器和內(nèi)存設(shè)備之間實現(xiàn)高效、高性能的通信。最新的CXL 3.1規(guī)范充分滿足了下一代計算中數(shù)據(jù)密集型應(yīng)用日益增長的需求。

▲從CXL 2.0過渡到CXL 3.0/3.1。資料來源:CXL聯(lián)盟

CXL 3.1的主要特性

CXL 3.1標(biāo)志著互連技術(shù)在CXL 3.0的基礎(chǔ)上向前邁出了重要一步,它提供了更高的速度、安全性、靈活性和效率,以滿足快速增長的行業(yè)需求。具體來說,與前代產(chǎn)品相比,CXL 3.1具有以下改進(jìn)特性:

擴(kuò)展元數(shù)據(jù):每個高速緩存行支持多達(dá)32位元數(shù)據(jù),以及2位用于緩存一致性的元數(shù)據(jù),用于描述緩存行的共享、獨占、修改或無效狀態(tài)。

新用例:從元數(shù)據(jù)中獲取的新信息可用于訪問控制、數(shù)據(jù)類型標(biāo)記、內(nèi)存分層算法等用例。

提高CXL內(nèi)存設(shè)備錯誤可見性:提供關(guān)于可更正錯誤限制、錯誤來源以及錯誤發(fā)生時所涉事務(wù)的新信息。

強化對內(nèi)存設(shè)備RAS的控制:提供內(nèi)存?zhèn)溆谩?a target="_blank">DDR5錯誤檢查清洗、介質(zhì)測試、巡邏清洗,以及容量/性能下降相關(guān)信息。

可信執(zhí)行環(huán)境安全協(xié)議(TSP):使基于虛擬化的TEE能夠托管機(jī)密性計算工作負(fù)載。

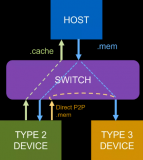

點對點通信:助力加速器實現(xiàn)直接的點對點CXL內(nèi)存訪問,提高資源利用率并減少延遲

雖然這些特性帶來了切實的提升,但CXL 3.1也引入了更多復(fù)雜性,隨之帶來了新的挑戰(zhàn)。對于任何新標(biāo)準(zhǔn)的發(fā)布,應(yīng)對這些挑戰(zhàn)對于確保穩(wěn)定性和性能至關(guān)重要。例如,CXL 3.x采用了256字節(jié)FLIT格式(類似于PCIe 6.x)來實現(xiàn)前向糾錯,從而減少誤碼。這一改變對于在更高傳輸速率下保持?jǐn)?shù)據(jù)完整性和性能至關(guān)重要。

借助可信執(zhí)行環(huán)境安全協(xié)議(TSP)

強化安全性

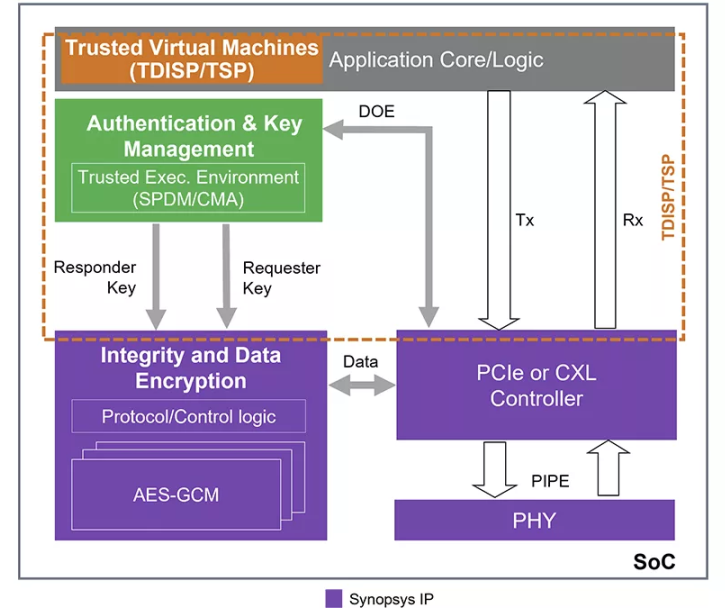

安全性仍然是CXL 3.1標(biāo)準(zhǔn)的基石。具體來說,可信執(zhí)行環(huán)境安全協(xié)議(TSP)適用于CXL.cache和CXL.mem,旨在保護(hù)基于虛擬化的環(huán)境,使其能夠托管機(jī)密性計算工作負(fù)載。該特性基于CXL 2.0中引入的現(xiàn)有完整性和數(shù)據(jù)加密(IDE)協(xié)議,進(jìn)一步增強了整個接口的數(shù)據(jù)保護(hù)。TSP的整合確保了數(shù)據(jù)的機(jī)密性與完整性,防范虛擬化環(huán)境中潛在的安全威脅。在數(shù)據(jù)日益敏感、法規(guī)愈發(fā)嚴(yán)格的當(dāng)下,這一點尤為重要。CXL.io虛擬化支持繼續(xù)受TEE設(shè)備接口安全協(xié)議(TDISP)的約束,該協(xié)議由PCI-SIG管理,并于2022年8月發(fā)布。

這些安全協(xié)議共同提升了與協(xié)議相關(guān)的安全性。憑借在這些領(lǐng)域的深厚專業(yè)知識,新思科技能夠提供全面的支持,確保實施方案既魯棒又安全。

CXL 3.1未來的改進(jìn)方向與新思科技的承諾

展望未來,CXL標(biāo)準(zhǔn)預(yù)計將不斷改進(jìn)。行業(yè)發(fā)展日新月異,新的需求與技術(shù)不斷涌現(xiàn)。新思科技始終致力于在這些變革中保持領(lǐng)先地位。我們積極參與標(biāo)準(zhǔn)制定過程,不僅確保自身能夠迅速適應(yīng)新特性,還主動為推動這些標(biāo)準(zhǔn)的未來發(fā)展貢獻(xiàn)力量。

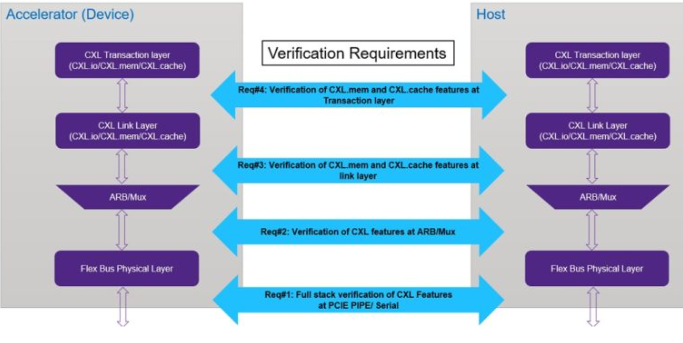

隨著CXL的持續(xù)發(fā)展與變化,新思科技將始終站在前沿,隨時準(zhǔn)備整合并支持這些技術(shù)進(jìn)步。我們高度關(guān)注安全性、性能與適應(yīng)性,完全有能力助力客戶充分釋放CXL 3.1及后續(xù)版本的潛力。新思科技CXL IP為CXL提供了完整的IP解決方案(包括控制器、PHY、IDE安全模塊和驗證IP),為人工智能、機(jī)器學(xué)習(xí)和云計算應(yīng)用提供安全、低延遲且高帶寬的互連。為降低風(fēng)險,新思科技CXL IP解決方案基于新思科技PCI Express IP構(gòu)建,該IP已在眾多應(yīng)用中得到驗證。

-

處理器

+關(guān)注

關(guān)注

68文章

19825瀏覽量

233742 -

存儲器

+關(guān)注

關(guān)注

38文章

7637瀏覽量

166533 -

cpu

+關(guān)注

關(guān)注

68文章

11049瀏覽量

216135 -

新思科技

+關(guān)注

關(guān)注

5文章

856瀏覽量

51269

原文標(biāo)題:CXL 3.1:CXL 標(biāo)準(zhǔn)的進(jìn)階之路上,如何將互連性能推向新高?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

互聯(lián)標(biāo)準(zhǔn)之戰(zhàn),CXL正在走向勝利

【直播回顧】OpenHarmony 3.1 Release版本南北向關(guān)鍵能力解讀

一窺CXL協(xié)議

一文解析CXL系統(tǒng)架構(gòu)

CXL事務(wù)層的結(jié)構(gòu)是由哪些部分組成的

CXL內(nèi)存協(xié)議介紹

一文詳解CXL鏈路層格式的定義

DesignWare CXL為SoC提供優(yōu)化的多芯片IP堆棧

新思CXL2.0驗證IP,加速連接新一代互聯(lián)技術(shù)

新思科技推出新一代開放標(biāo)準(zhǔn)互聯(lián)技術(shù)CXL

關(guān)于CXL的一些基礎(chǔ)知識 CXL將一統(tǒng)CPU互連標(biāo)準(zhǔn)

CXL協(xié)議和標(biāo)準(zhǔn)介紹, CXL2.0和3.0有什么新功能?

揭開CXL的神秘面紗:概述

新思科技CXL 3.1驗證解決方案

第二代AMD Versal Premium系列SoC滿足各種CXL應(yīng)用需求

新思科技解讀CXL 3.1標(biāo)準(zhǔn)

新思科技解讀CXL 3.1標(biāo)準(zhǔn)

評論