Signal Tap 概述

Signal Tap Logic Analyzer是Intel Quartus Prime設計軟件中自帶的新一代系統級調試工具,它可以在FPGA設計中采集和顯示實時的信號行為。當設計在FPGA上全速運行時,無需額外的I/O引腳即可檢查正常器件操作期間內部信號的行為。

Signal Tap Logic Analyzer具有可擴展性,易于使用,支持以下功能:

無需外部設備,通過探測內部信號的狀態來調試FPGA設計。

自定義觸發條件邏輯,提高準確性并提升分析問題的能力。

將所有捕獲的信號數據存儲在設備存儲器中,直到需要進行讀取和分析。

Signal Tap Logic Analyzer支持可編程邏輯市場上任何邏輯分析儀中最多的通道數、最大的采樣深度和最快的時鐘速度。

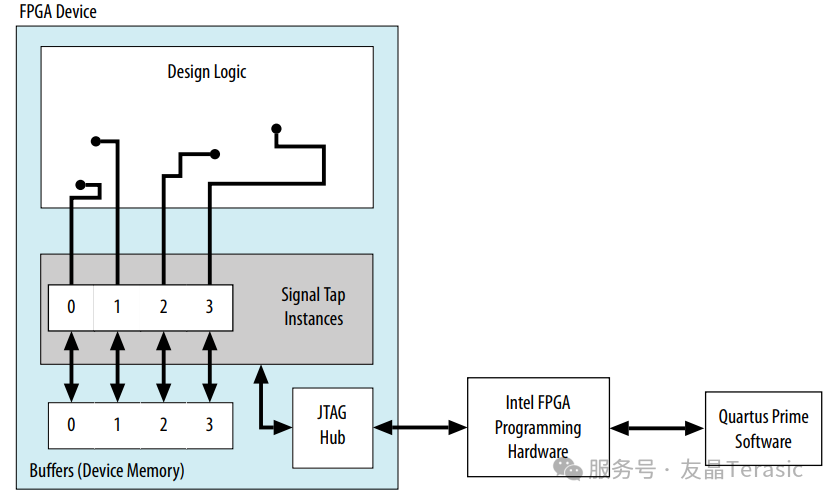

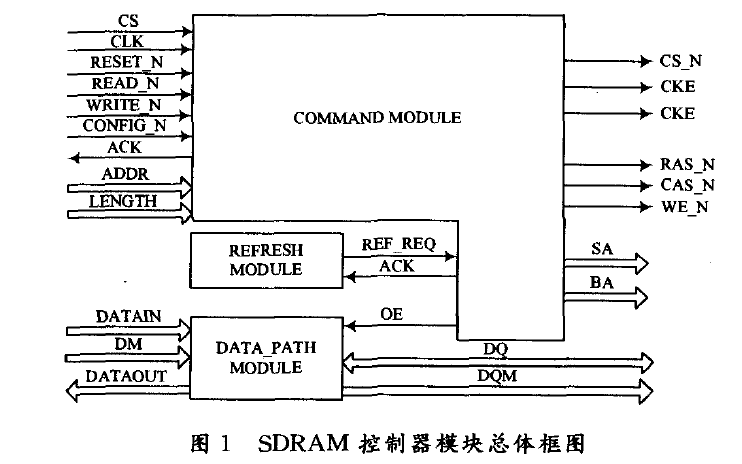

下圖1.1是Signal Tap Logic Analyzer內部結構圖,它是利用JTAG邊界掃描的原理來讀取FPGA內部節點的值,然后傳輸到buffer(緩沖器),再由JTAG把數據送到Quartus下的Signal Tap Logic Analyzer工具。整個過程只讀取數據,而數據的頻率無法直接知道,只能由設計者自行計算得出。

圖1.1 Signal Tap Logic Analyzer結構圖

在設計中嵌入SignalTapLogicAnalyzer

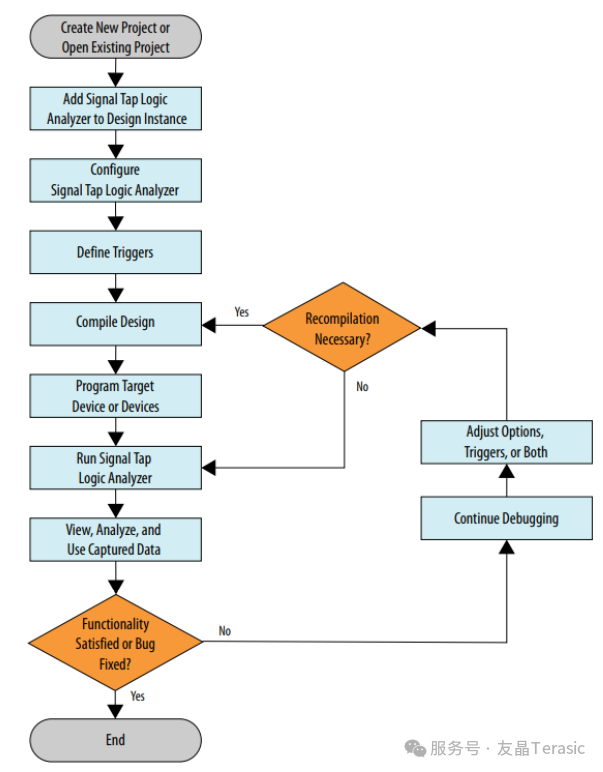

要使用Signal Tap Logic Analyzer對設計進行調試,需要執行幾個任務來添加、配置和運行Signal Tap Logic Analyzer。如下圖所示為Signal Tap Logic Analyzer任務流程圖。

圖2.1 Signal Tap Logic Analyzer任務流程圖

在設計中嵌入Signal Tap Logic Analyzer有以下兩種方法:

建立一個Signal Tap文件,即.stp文件,然后定義該文件的詳細內容。

用MegaWizard Plug-In Manager建立并配置.stp文件,然后使用MegaWizard實例化一個HDL輸出模塊。

本教程采用第一種方法,在設計好的Quartus工程文件中嵌入Signal Tap Logic Analyzer進行時序波形的在線調試。

創建.stp文件

.stp文件包括Signal Tap Logic Analyzer設置部分和捕獲數據的查看、分析部分。創建一個.stp文件的步驟如下:

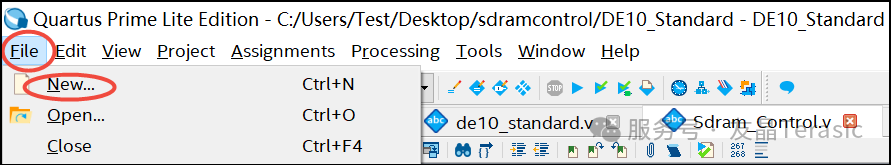

打開Quartus Prime軟件,并打開需要嵌入Signal Tap Logic Analyzer的Quartus工程,然后依次點擊Quartus工具欄的File-->New,如下圖所示2.2所示。

圖2.2 選擇New對話框

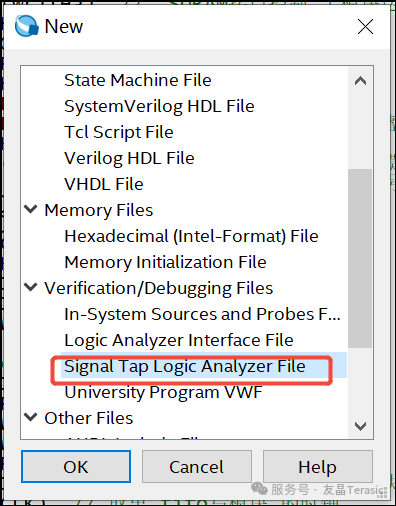

2. 在彈出的New對話框中,選擇Verification/Debugging Files中的Signal Tap Logic Analyzer File,如圖2.3所示,點擊OK確認。

圖2.3 選擇Signal Tap Logic Analyzer File

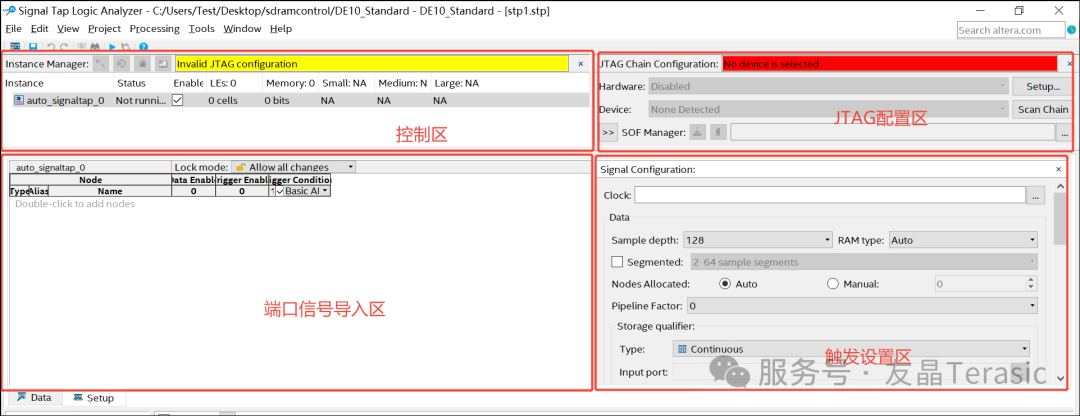

3. 彈出新的Signal Tap Logic Analyzer窗口,如圖2.4所示。

圖2.4 Signal Tap Logic Analyzer窗口

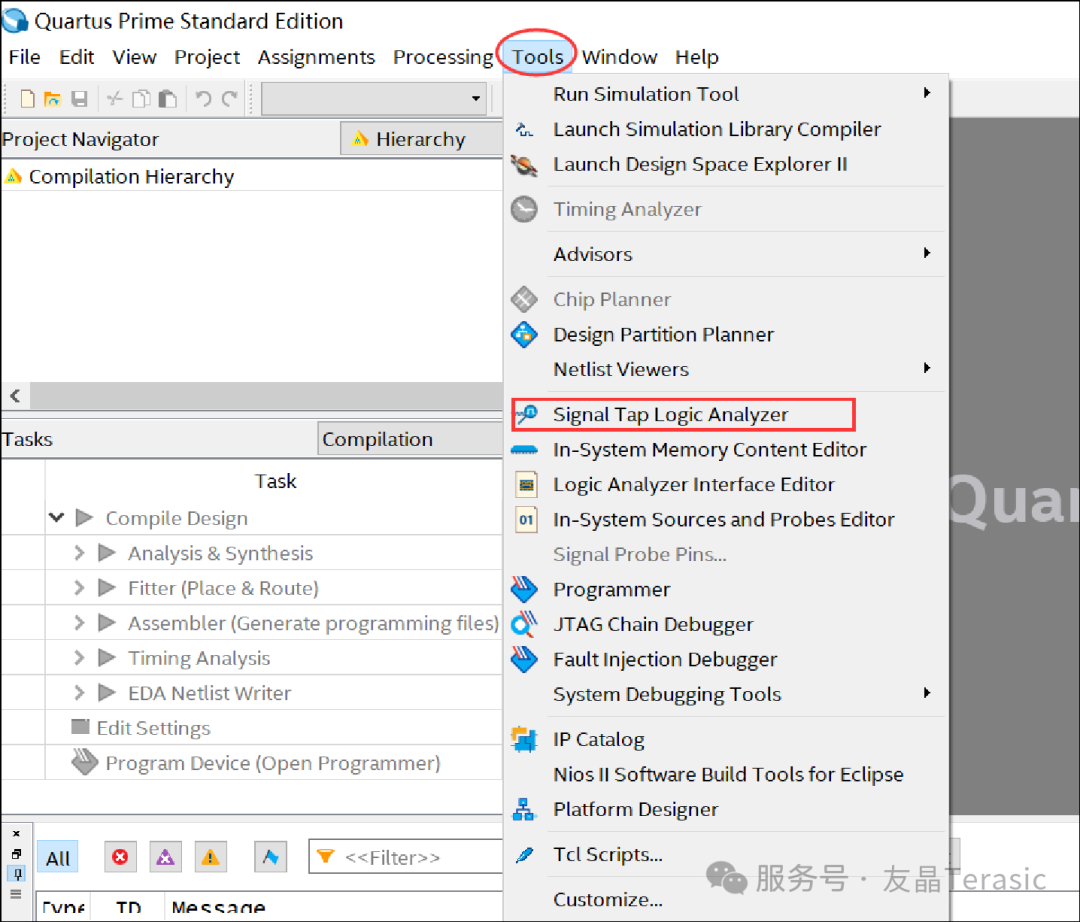

以上操作也可以通過Quartus軟件的工具欄Tools-->Signal Tap Logic Analyzer來完成,如下圖2.5所示。

圖2.5 打開Signal Tap Logic Analyzer

設置.stp文件采集時鐘

在使用Signal Tap Logic Analyzer進行FPGA在線調試之前,需要設置.stp文件的采集時鐘,采集時鐘是在上升沿采集數據。可以使用Quartus工程設計中的任意信號作為采集時鐘,最好使用全局時鐘,而不要使用門控時鐘,并且選擇的采樣信號和待觀測的信號要滿足奈奎斯特采樣定理。

設置采集時鐘的步驟如下:

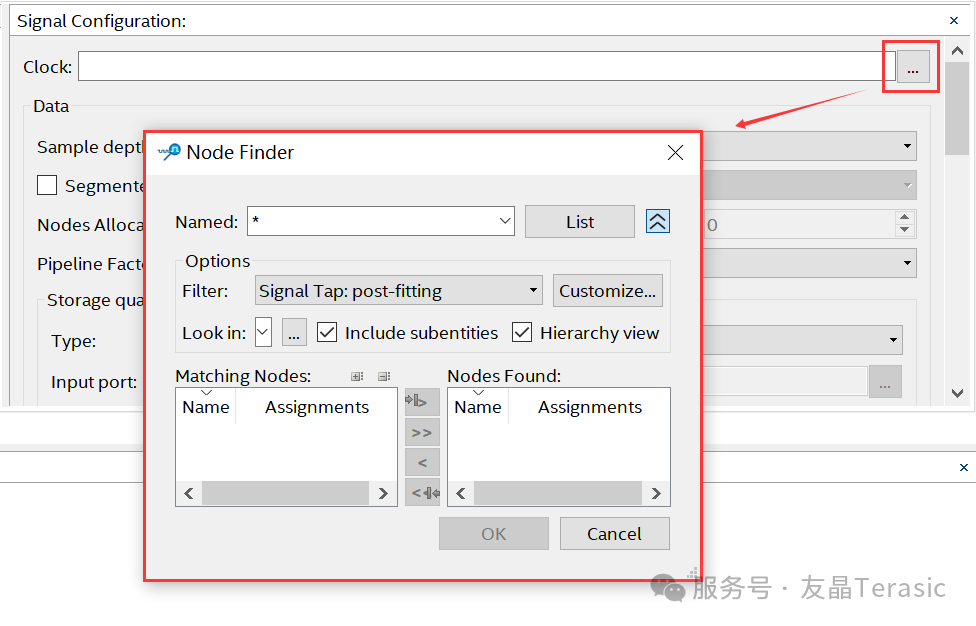

1. 在圖2.4所示的Signal Tap Logic Analyzer窗口的觸發設置框,點開Clock后面的"..."按鈕,打開Node Finder對話框,如圖2.6所示。

圖2.6 打開Node Finder對話框

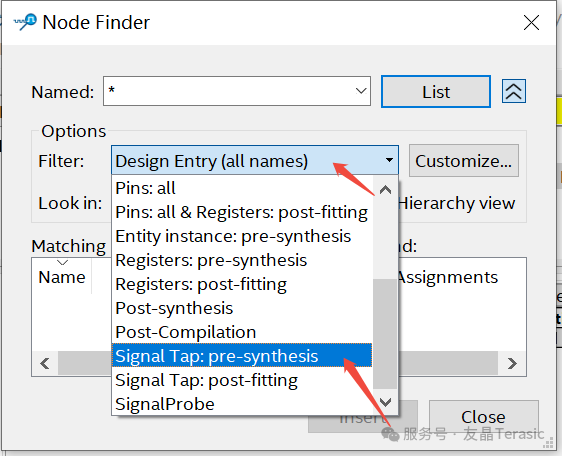

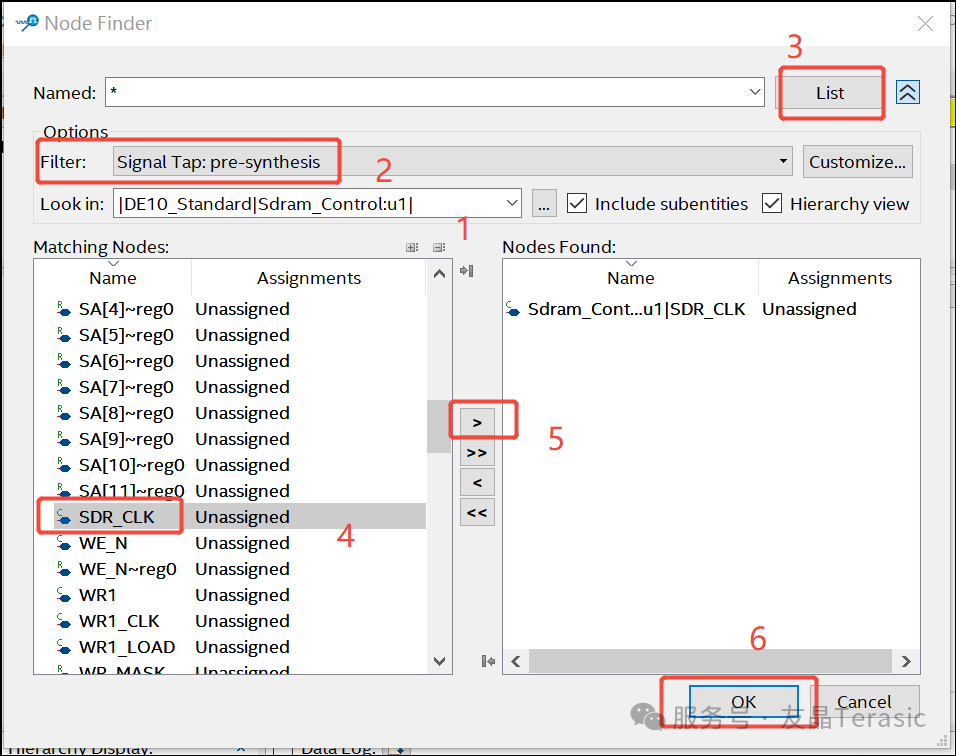

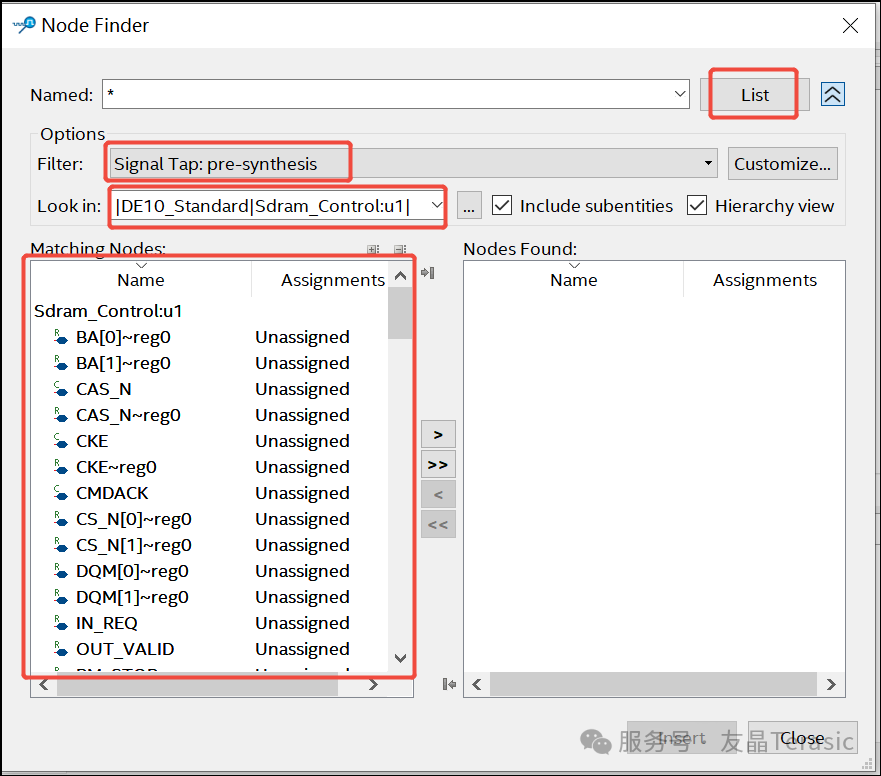

2. 在Node Finder對話框中,在Filter列表中選擇 Design Entry(all names)或SignalTap:pre-synthesis,如圖2.7所示。

圖2.7 選中 Design Entry(all names)

3. 想要看工程里面的哪個文件的信號,就在Look in這里選擇對應的文件(或者直接選top文件,所有信號在top文件里面可以找到),然后點擊Name行后的List按鈕,在Nodes Found列表中選擇合適的信號作為Signal Tap Logic Analyzer的采集時鐘,如圖2.8所示,此處舉例選擇Sdram_Control.v文件的信號進行查看,選擇Sdram_Control.v文件里面的100MHz作為采樣時鐘。選中后點擊">"按鈕將時鐘信號添加到Nodes Found列表中,也可以直接雙擊CLK將時鐘信號添加到Nodes Found列表。

圖2.8 Node Finder對話框設置

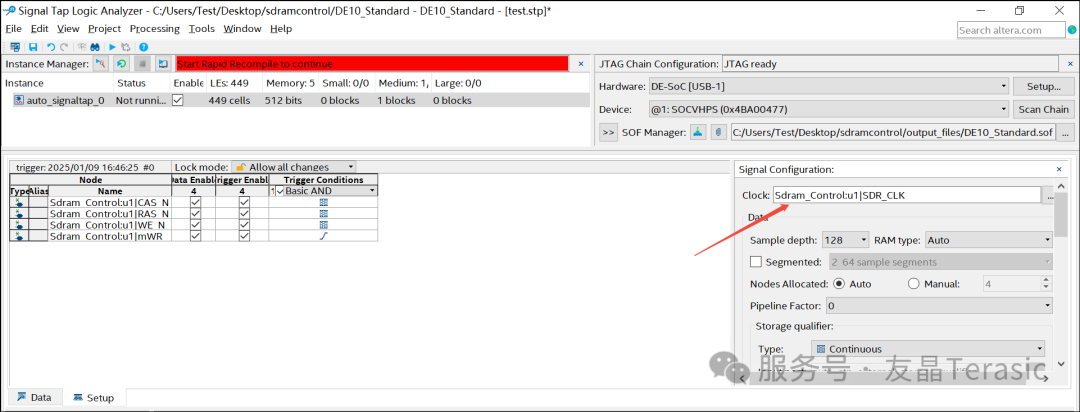

4. 點擊OK按鈕確定。在Signal Tap Logic Analyzer窗口中可以看到,設置作為采樣時鐘的信號CLK顯示在Clock欄中。如圖2.9所示。

圖2.9 顯示Clock采樣時鐘信號

注意:如果在Signal Tap Logic Analyzer窗口中沒有分配采集時鐘,Quartus軟件會自動建立一個名為auto_stp_external_clk_0的時鐘引腳。在設計中必須為這個引腳單獨分配一個器件引腳。在開發板上也必須有一個外部時鐘信號驅動該引腳。

在.stp文件中配置信號節點

在.stp文件中,常分配如下兩種類型的信號:

Signal Tap: pre-synthesis——該信號在對設計進行Analysis&Elaboration操作以后存在,這些信號表示寄存器傳輸級(RTL)信號。在Signal Tap Logic Analyzer中要分配Pre-synthesis信號,可以選擇Quartus軟件工具欄的Processing-->Start Analysis&Elaboration。對設計進行修改后,如果要在物理綜合之前快速加入一個新的節點名,使用這項操作特別有用。

Signal Tap: post-fitting——該信號在對設計進行物理綜合優化以及布局布線操作后存在。

本教程采用分配Signal Tap: pre-synthesis類型信號為例進行說明。

分配數據信號

依次點擊Quartus軟件工具欄的Processing-->Start-->Start Analysis&Elaboration,對設計進行Analysis&Elaboration。

圖2.10 對設計進行Analysis&Elaboration

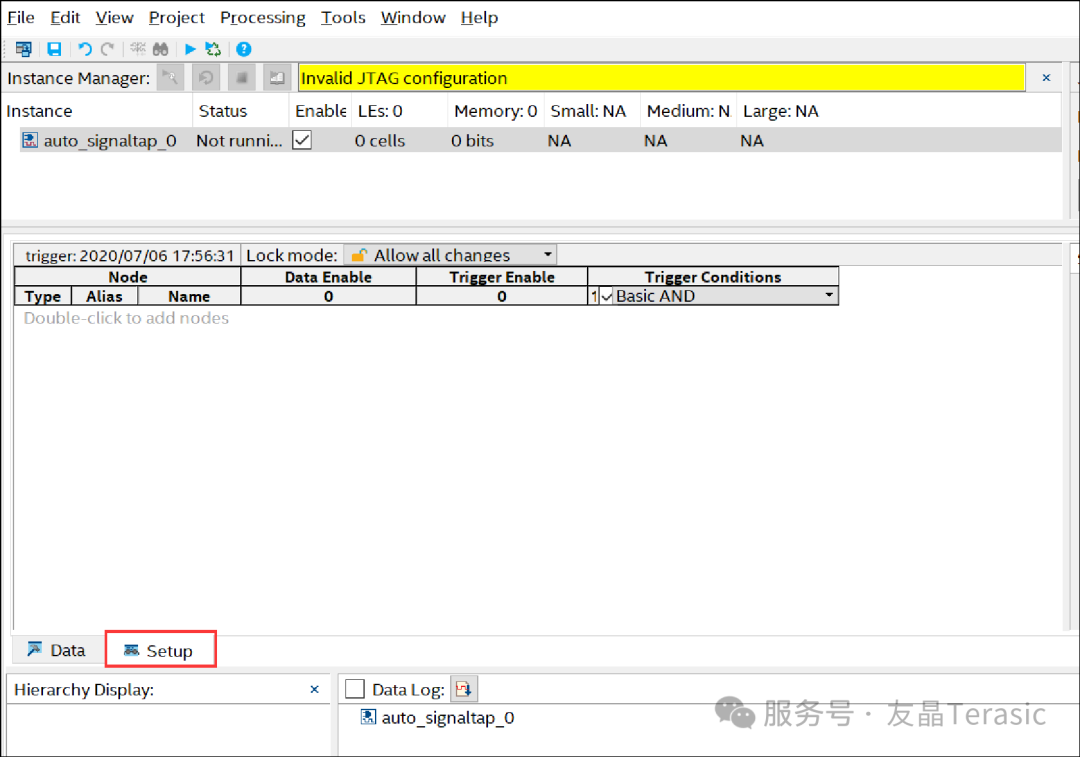

2. 在Signal Tap Logic Analyzer窗口中點擊Setup標簽頁,如下圖2.11所示。

圖2.11 Setup標簽頁

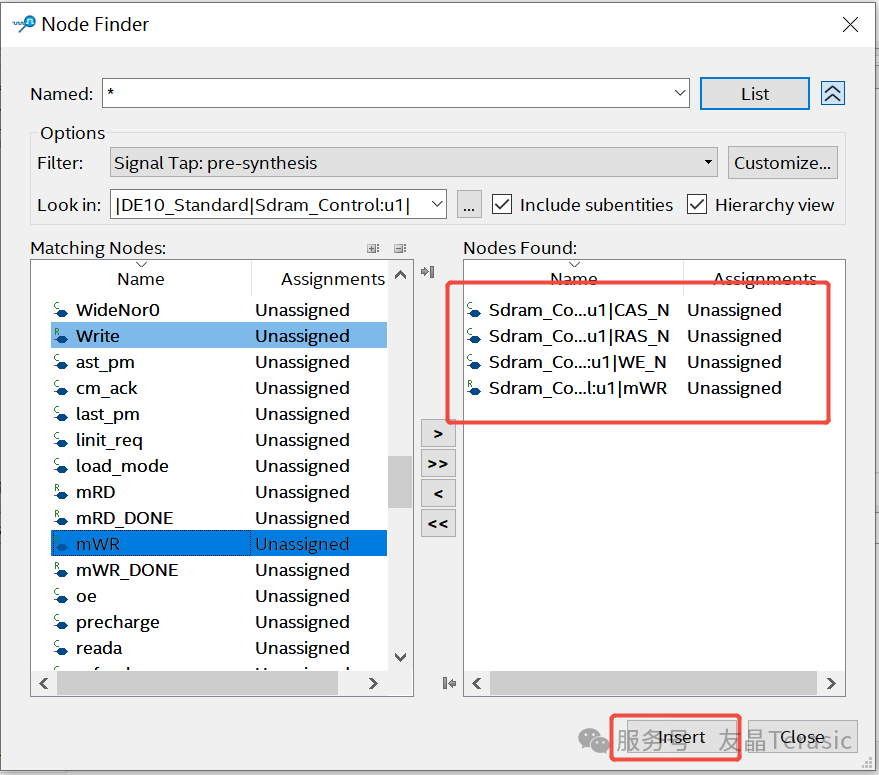

3. 雙擊Setup標簽頁的空白處,彈出Node Finder對話框。

4. 在Node Finder對話框的Filter列表中選擇Signal Tap: pre-synthesis。

5. 點擊Node Finder對話框Name行后的List按鈕查找節點,所有節點都顯示在Matching Nodes列表中。

圖2.12 Nodes Finder對話框

6. 雙擊相應的節點或總線將其添加到Nodes Found列表中。

7. 點擊Insert按鈕,將選擇的節點或總線插入到.stp文件。

圖2.13 選擇節點

SignalTapLogicAnalyzer觸發設置

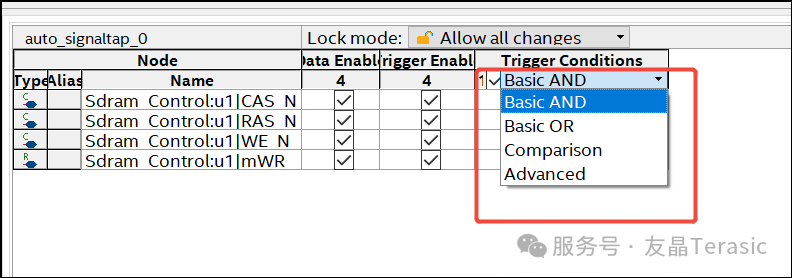

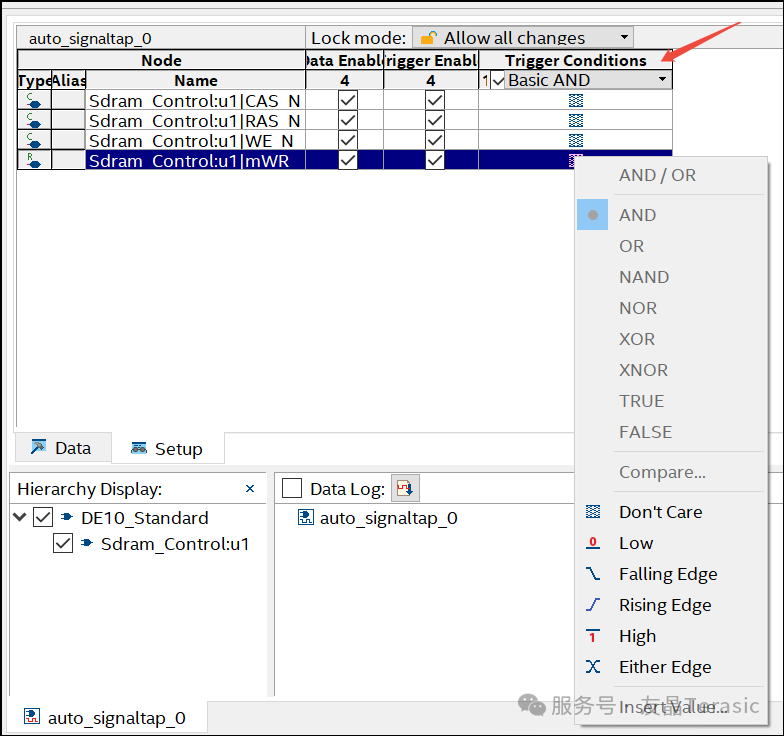

Signal Tap Logic Analyzer觸發設置主要是設置觀測信號的觸發條件(Trigger Conditions)。

觸發類型選擇Basic AND或Basic OR:如果觸發類型選擇Basic,在.stp文件中必須為每個信號設置相應的觸發模式(Trigger Pattern)。Signal Tap Logic Analyzer中的觸發模式包括Don't Care(無關項觸發)、Low(低電平觸發)、High(高電平觸發)、Falling Edge(下降沿觸發)、Rising Edge(上升沿觸發)和Either Edge(雙邊沿觸發)。如圖2.14所示,當設定的觸發條件滿足時,Signal Tap Logic Analyzer開始捕獲數據。

圖2.14-1 設置類型

圖2.14-2 設置觸發模式

觸發類型選擇Advanced:如果觸發類型選擇Advanced,則必須為Signal Tap Logic Analyzer建立觸發條件表達式。一個Signal Tap Logic Analyzer最關鍵的特點是它的觸發能力。如果不能很好的為數據捕獲建立相應的觸發條件,它可能無法幫助設計者捕捉到需要觀測的有效信號。

在Signal Tap Logic Analyzer中,使用高級觸發條件編輯器(Advanced Trigger Condition Editor)可以在簡單的圖形界面建立非常復雜的觸發條件。設計者只需要將運算符拖動到觸發條件編輯器窗口中,就可以建立復雜的觸發條件,如圖2.15所示。

圖2.15 高級觸發條件編輯器

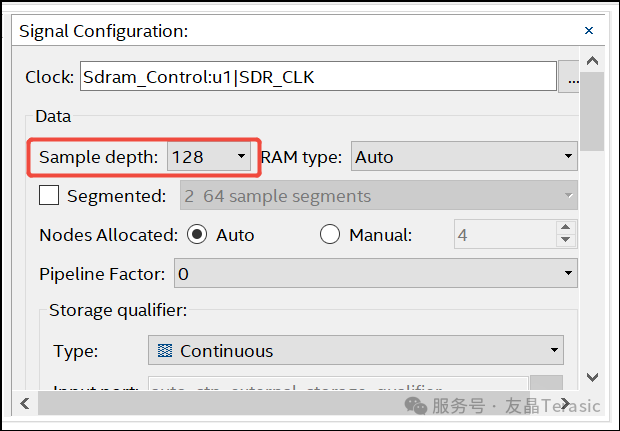

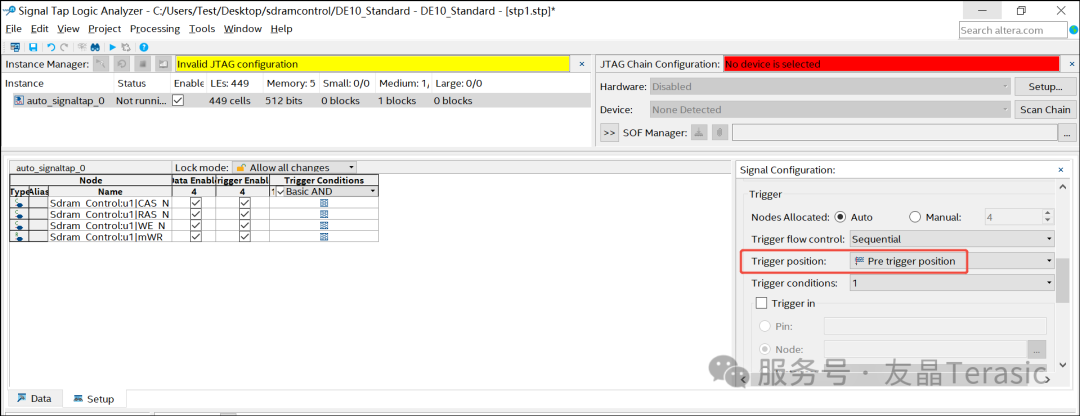

指定采樣點數及觸發位置

在觸發事件開始之前,可以指定要觀測數據的采樣點數,即數據存儲深度,以及觸發事件發生前后的采樣點數,如圖2.16所示。

圖2.16-1 設置采樣點數及觸發位置

圖2.16-2 設置采樣點數及觸發位置

在Signal Tap Logic Analyzer窗口右側Signal Configuration部分的Data欄中,在Sample depth列表中可以選擇需要觀測的采樣點數;在Trigger欄中,在Trigger Condition列表中可以選擇觸發信號有效前后的數據比例:

1. Pre trigger position:保存觸發信號發生之前信號狀態信息(88%的觸發前數據,12%的觸發后數據)。

2. Center trigger position:保存觸發信號發生前后數據,各占50%。

3. Post trigger position:保存觸發信號發生之后信號狀態信息(12%的觸發前數據,88%的觸發后數據)。

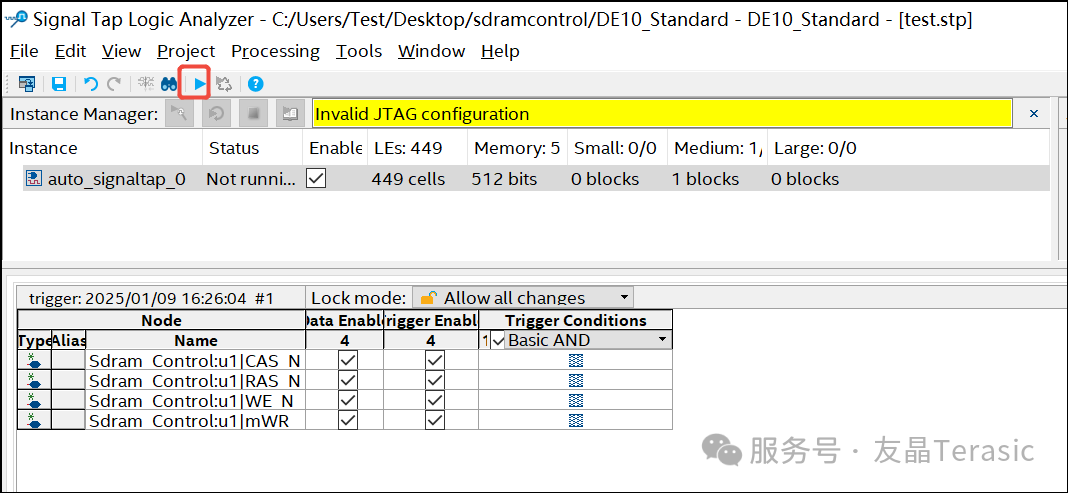

重新編譯嵌入.stp文件的Quartus工程

配置好并保存.stp文件后,在使用Signal Tap Logic Analyzer之前必須編譯Quartus工程。如下圖2.17所示,點擊Signal Tap Logic Analyzer窗口的編譯按鈕,對工程進行全編譯。

圖2.17 全編譯Quartus工程

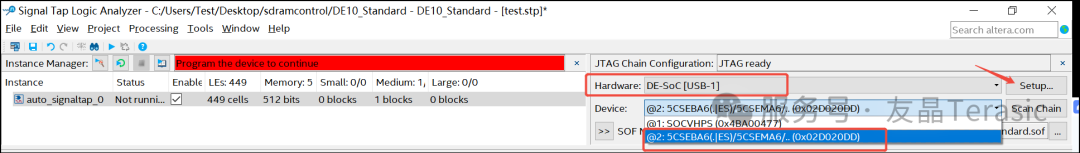

使用Signal Tap Logic Analyzer進行編程調試

在設計中嵌入.stp文件并完全編譯完成后,通過USB Blaster II下載電纜連接好開發板并接通電源。打開.stp文件后,詳細調試步驟如下:

1. 在.stp文件右上方的JTAG Chain Configuration部分,在Hardware列表中選擇 "DE-SoC[USB-1]",一般情況下Signal Tap Logic Analyzer可以自動掃描到開發板上的FPGA器件并顯示在Device列表中。如下圖2.18所示。

圖2.18 JTAG Chain設置

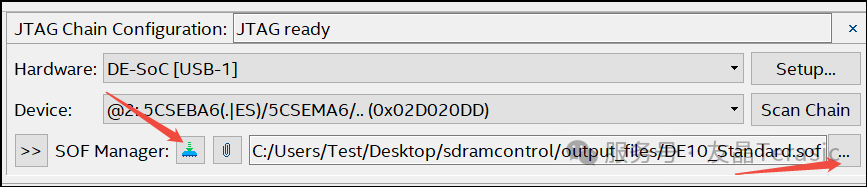

2. 點擊SOF Manager右側的"..."按鈕,選擇.sof文件,然后點擊下載按鈕對FPGA進行配置,如下圖2.19所示。

圖2.19 配置FPGA

查看Signal Tap Logic Analyzer調試波形

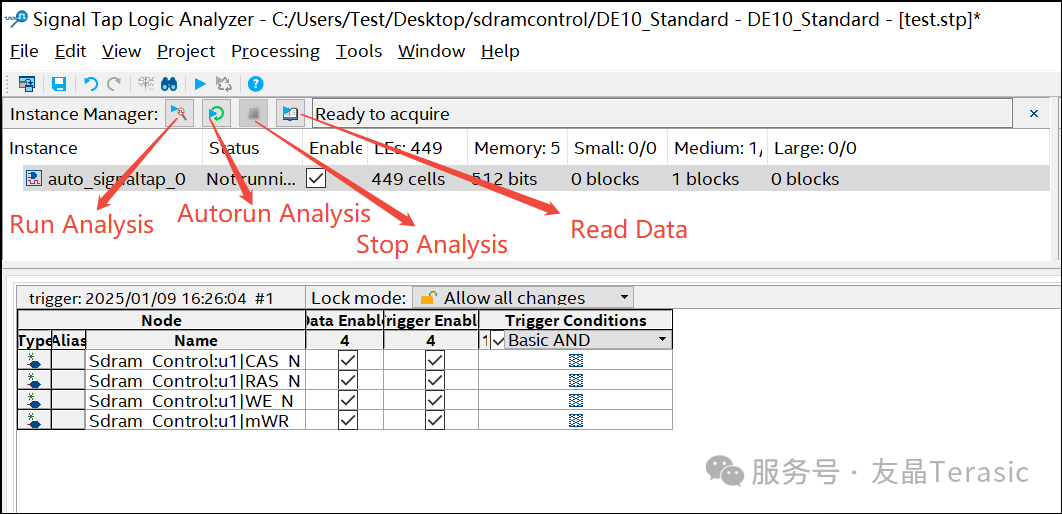

Signal Tap Logic Analyzer工具條上有四個執行邏輯分析的選項,如下圖所示。

圖2.20-1

1. Run Analysis:單步執行捕獲數據進行邏輯分析,即執行該命令后,Signal Tap Logic Analyzer等待觸發事件,當觸發事件發生時開始采集數據,然后停止。

2. Autorun Analysis:執行該命令后,Signal Tap Logic Analyzer根據所設置的觸發條件連續采集數據,直到用戶按下Stop Analysis按鈕為止。

3. Stop Analysis:停止Signal Tap Logic Analyzer。如果觸發事件還沒有發生,則沒有接收數據顯示。

4. Read Data:顯示捕獲的數據。如果觸發事件還沒有發生,用戶可以點擊該按鈕查看當前采集的數據。

選擇Run Analysis或AutoRun Analysis按鈕,當觸發條件滿足時,Signal Tap Logic Analyzer開始捕獲數據。

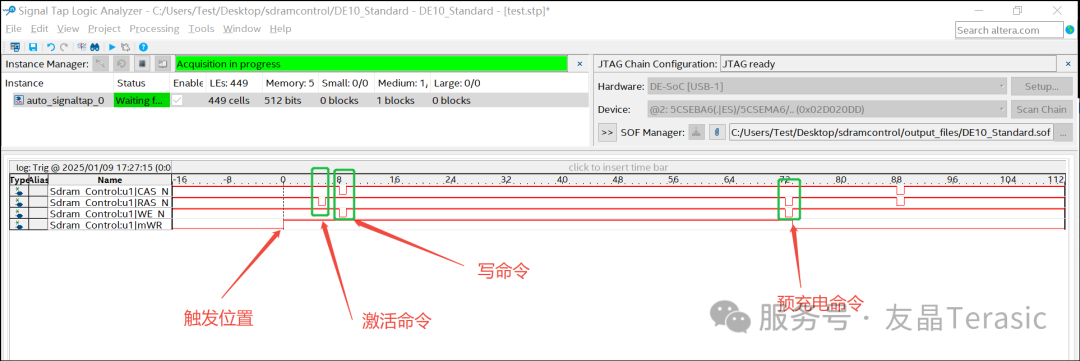

圖2.20-2

Signal Tap Logic Analyzer會自動將采集的數據顯示在Data標簽頁中,如圖2.20-2所示。

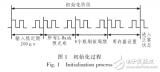

從波形圖可以看到,寫SDRAM之前先發送了一個行激活命令,然后是寫命令,連續寫64個數據以后系統發送了一個預充電命令結束頁突發操作。

-

FPGA

+關注

關注

1645文章

22022瀏覽量

617448 -

存儲器

+關注

關注

38文章

7644瀏覽量

167066 -

調試工具

+關注

關注

1文章

52瀏覽量

12807 -

SignalTap

+關注

關注

0文章

9瀏覽量

9600

原文標題:10-SDRAM控制器的設計—— signaltap 調試

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

SDRAM控制器的設計——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

FPGA之SDRAM控制器設計(二)精選資料分享

使用Verilog實現基于FPGA的SDRAM控制器

基于FPGA的高速SDRAM控制器的視頻應用

SDRAM控制器的設計

FPGA讀寫SDRAM的實例和SDRAM的相關文章及一些SDRAM控制器設計論文

如何使用FPGA設計SDRAM控制器

SDRAM控制器設計之signaltap調試

SDRAM控制器設計之signaltap調試

評論