案例49: PCB中多了1cm2的地層銅

【現(xiàn)象描述】

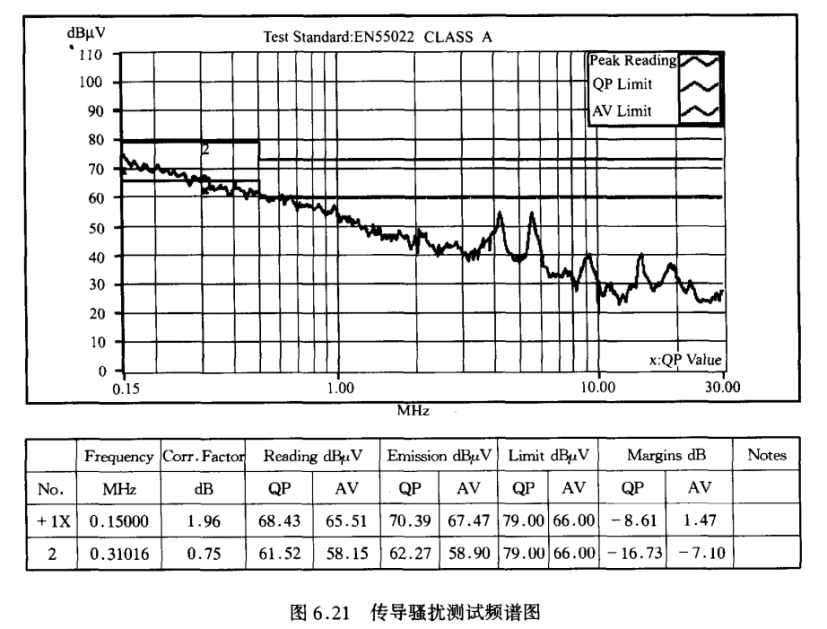

某通信轉(zhuǎn)換模塊的24V直流電源端口傳導(dǎo)騷擾測(cè)試頻譜圖如圖6.21所示。

從圖中可以看出,低頻段平均值超過CLASS A限值。

【原因分析】

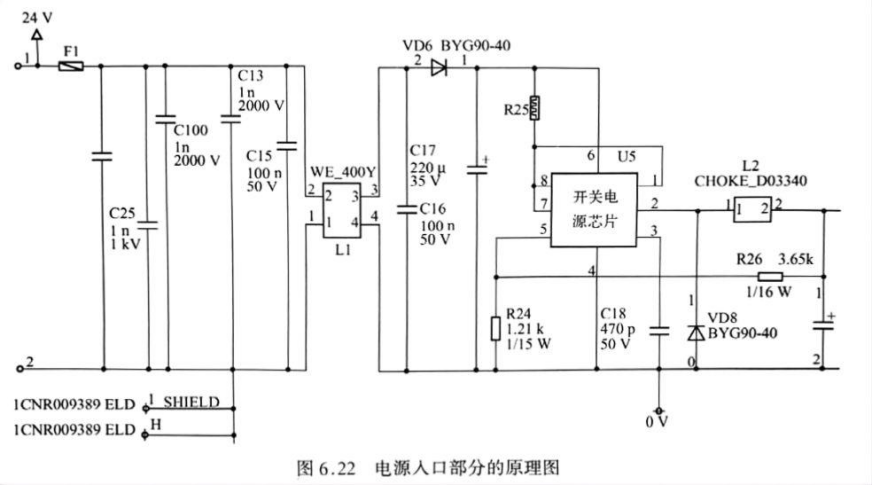

該產(chǎn)品的電源入口部分的原理圖如圖6.22所示。

圖中,U5是非隔離開關(guān)電源。它從EMI角度考慮是一個(gè)干擾源,其開關(guān)信號(hào)及其諧波將直接影響傳導(dǎo)騷擾測(cè)試的幅值。L1 是共模電感,可對(duì)該電源端口進(jìn)行共模濾波,防 止圖中左右兩側(cè)無用共模信號(hào)相互傳輸。對(duì)于EMI來講,主要是用來抑制來自于開關(guān)電源,包括電源線上及0V上的騷擾,從而達(dá)到較好的EMC效果。

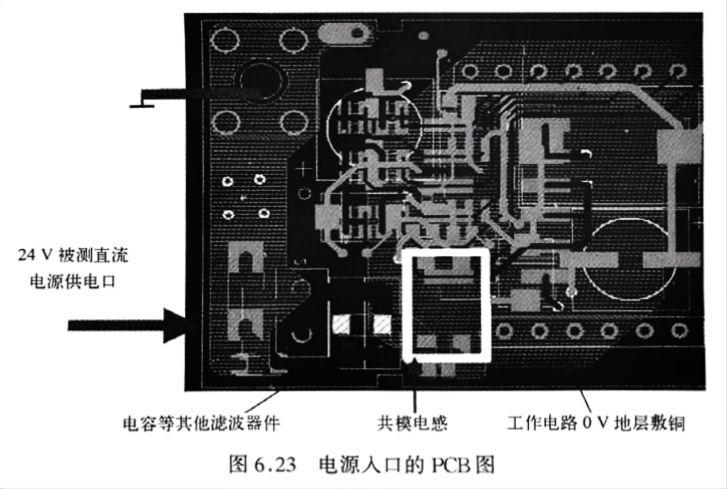

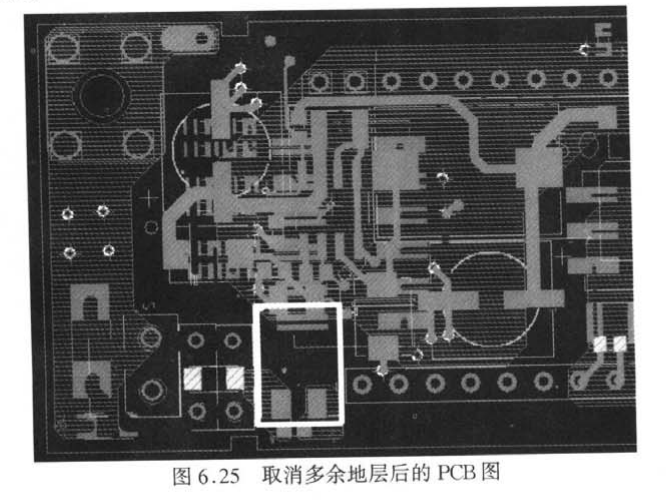

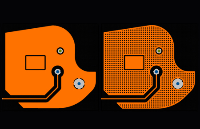

該產(chǎn)品電源入口的PCB圖如圖6.23所示。

其中,白色方框表示共模電感L1的位置。

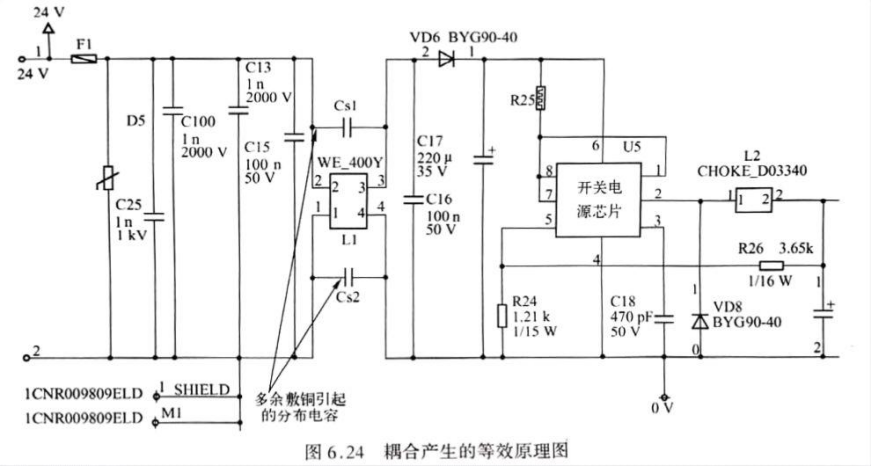

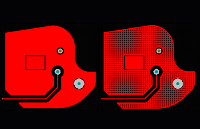

經(jīng)過仔細(xì)分析后發(fā)現(xiàn),共模電感下面的0V 地層敷銅是多余的。由于共模電感的體積較小,因此電感下面的敷銅也較小,約1cm2。雖然面積較小,但將同樣會(huì)起到被隔離的共模電感兩側(cè)容性耦合作用,使共模電感的作用在一定程度上喪失。耦合產(chǎn)生的等效原理圖如圖6.24所示。

圖中,Cl和C2表示多余敷銅引起的分布電容,它在一定的頻率下將共模電感兩端連通,所以來自于后一級(jí)開關(guān)電源的干擾將通過分布電容直接流向傳導(dǎo)騷擾的測(cè)試儀。為了證實(shí)分析的正確性,修改PCB板,將多余的地層取消,取消多余地層后的PCB圖如圖6.25所示。

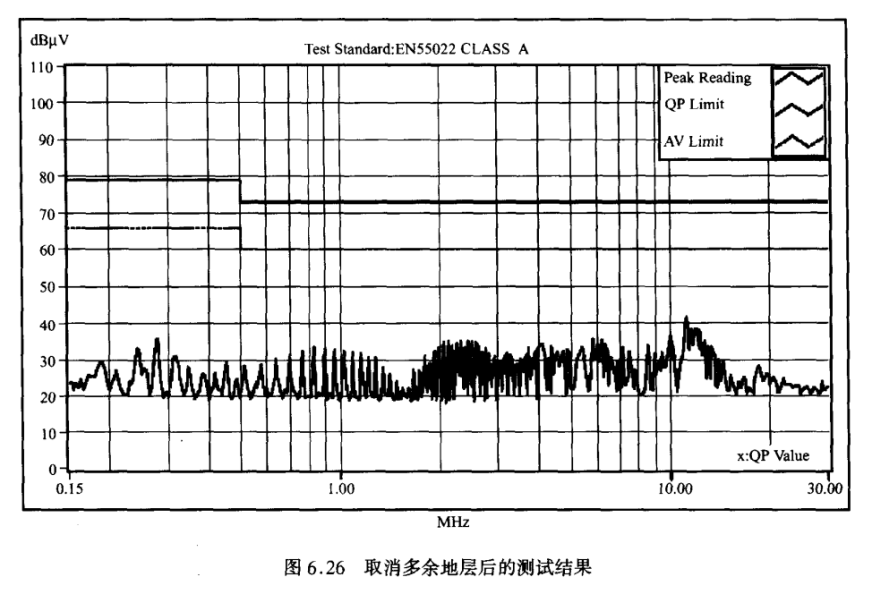

再進(jìn)行測(cè)試,取消多余地層后的測(cè)試結(jié)果如圖6.26所示。

難以置信的結(jié)果,傳導(dǎo)騷擾得到了很大的改善。

【處理措施】

將共模電感下多余的“0V”地層取消,使共模電感起到良好的隔離作用。

【思考與啟示】

(1)地層及電源層不能隨便鋪設(shè),哪怕只有很小的面積。

(2)濾波電路的輸入、輸出之間一定要有良好的隔離,才能最大限度地發(fā)揮濾波電路的預(yù)想作用。

以上案例來自EMC領(lǐng)域知名專家-鄭老師《EMC電磁兼容設(shè)計(jì)與測(cè)試案例分析》著作內(nèi)容其一案例!

-

電源

+關(guān)注

關(guān)注

185文章

18308瀏覽量

255342 -

pcb

+關(guān)注

關(guān)注

4357文章

23440瀏覽量

407655 -

測(cè)試

+關(guān)注

關(guān)注

8文章

5648瀏覽量

128455

發(fā)布評(píng)論請(qǐng)先 登錄

天線角度看PCB覆銅的利與弊

dxp2004pcb加地層不顯示問題

基于STM32 VL53L0激光測(cè)距 精度高于1cm

【PCB多層板設(shè)計(jì)挑戰(zhàn)賽】智能戒指,1cm*1.2cm超小尺寸,可實(shí)現(xiàn)運(yùn)動(dòng)姿態(tài)跟蹤與NFC支付,支持一鍵報(bào)警。

在PCB中兩個(gè)不同電壓的電源層可以共用一個(gè)地層嗎?

PCB設(shè)計(jì)技巧_覆銅技巧

PCB孔銅厚度標(biāo)準(zhǔn)及成品銅厚構(gòu)成

如何對(duì)PCB板進(jìn)行中間地層分割處理

PCB設(shè)計(jì)中銅厚和線寬的選擇

什么是PCB覆銅?pcb覆銅有什么作用

案例49: PCB中多了1cm2的地層銅

案例49: PCB中多了1cm2的地層銅

評(píng)論