“解析數模轉換器與模數轉換器的工作原理——從電阻階梯網絡到Delta-Sigma調制技術。”

微控制器正在“吞噬”整個世界。如今,即使是閃爍LED等最基礎的任務,使用微控制器也比用分立元件搭建振蕩電路或依賴曾經無處不在的555定時器芯片更便宜、更簡單。

然而,在這個日益由軟件定義的世界中,0和1并非萬能。圖像傳感器將光強記錄為一系列模擬值;播放音樂的揚聲器,其振膜需要移動到除了“完全向內”和“完全向外”之外的多種位置。最終,幾乎所有復雜的數字電路都需要專門的數模轉換器(DAC)和模數轉換器(ADC)來連接物理世界。這些轉換器通常集成在微控制器的芯片中,但其原理仍值得探究。

簡單的數模轉換器(DAC)

將數字信號轉換為模擬信號的核心在于將一定位長的二進制數映射為量化輸出電壓范圍。例如,一個4位DAC有16種可能的輸出電壓,其典型行為如下:

0000(0) =0V 0001 (1) =1/15Vdd 0010 (2) =2/15Vdd 0011 (3) =3/15Vdd ...1111(15) = Vdd

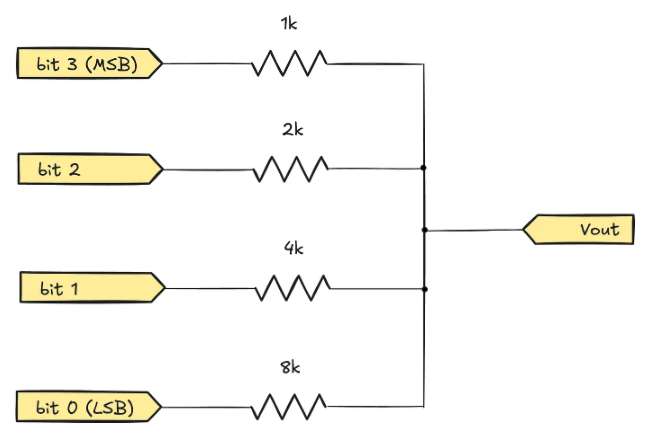

實現此類轉換的最簡單方法是基于電阻的二進制加權DAC:

顯然,當二進制輸入為0000時,模擬輸出應為0V;反之,若輸入為1111,則輸出必須達到Vdd。對于中間數值的輸入,我們應獲得電阻加權平均值,其中每個比特位的影響權重是其高位比特的一半。這種特性與二進制數的工作原理完美契合。

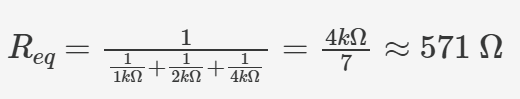

我們可對此進行更嚴謹的電路分析。以輸入值 0001 為例:此時高位三個電阻(比特位#1、#2和#3)并聯接地,其等效電阻值為:

而最低有效位(LSB)對應的電阻則連接至 Vdd。整個電路可視為由兩個串聯電阻構成的Vdd-地分壓網絡,其輸出電壓為:

類似地,當輸入為 1110(十進制14)時,輸出電壓Vout ≈ 14/15 Vdd。這與我們期望的線性響應特性完全吻合。

該 DAC 架構的主要缺陷在于所需電阻值很快會變得不切實際。為避免靜態電流過大,最高有效位(MSB)對應的電阻值不能過低(1 kΩ是合理的起始值)。但對于16位DAC而言,這意味著最低有效位電阻需達到 1 kΩ × 21? ≈ 32 MΩ;若實現24位分辨率,則需數吉歐姆(GΩ)量級的電阻。在集成電路晶圓上制造如此高精度的大阻值電阻極具挑戰性,若還要求其具備相同的溫度系數,則難度更甚。

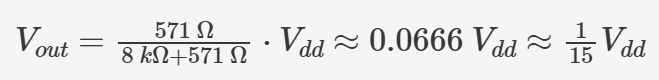

針對這一難題,工程師提出了巧妙的 R-2R 梯形 DAC 架構解決方案:

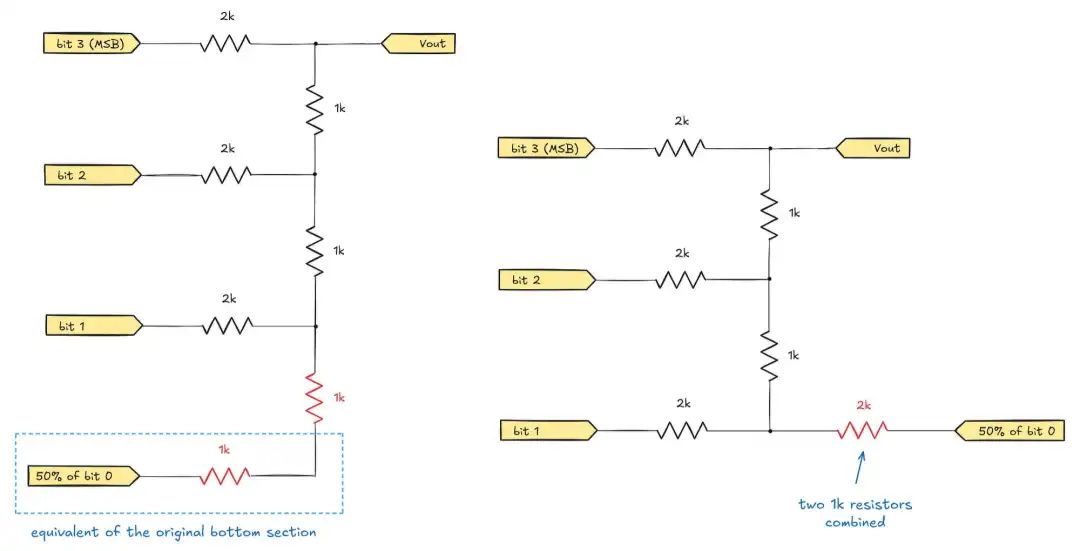

相較于傳統架構,這種 R-2R 梯形電路的沒那么直觀,但其工作原理具有相似性。為解析其設計邏輯,我們從最底層結構入手:即位于比特位#0處的兩個水平放置的電阻。這兩個電阻向電路其余部分提供等量電流,因此其功能等效于一個連接在合成輸入電壓上的 1 kΩ電阻。該合成電壓的取值邏輯為:當 LSB=0 時等于0V,LSB=1 時等于 Vdd/2。換言之,比特位#0的輸入信號在此處被壓縮為50%的權重。

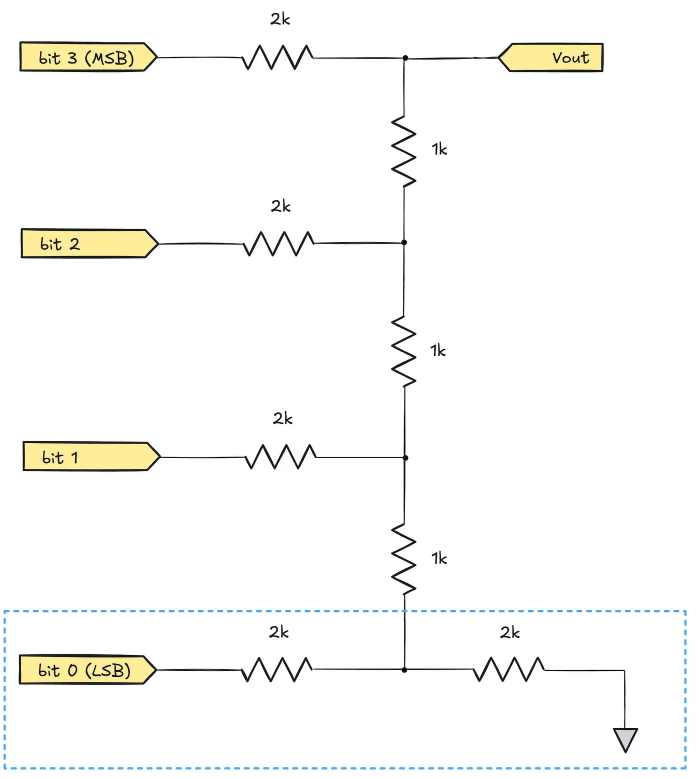

通過這種等效替換,我們得到左圖所示的簡化電路。進一步觀察,底層結構中兩個串聯的1 kΩ電阻(紅色標注)可等效為右圖中的單個2 kΩ電阻:

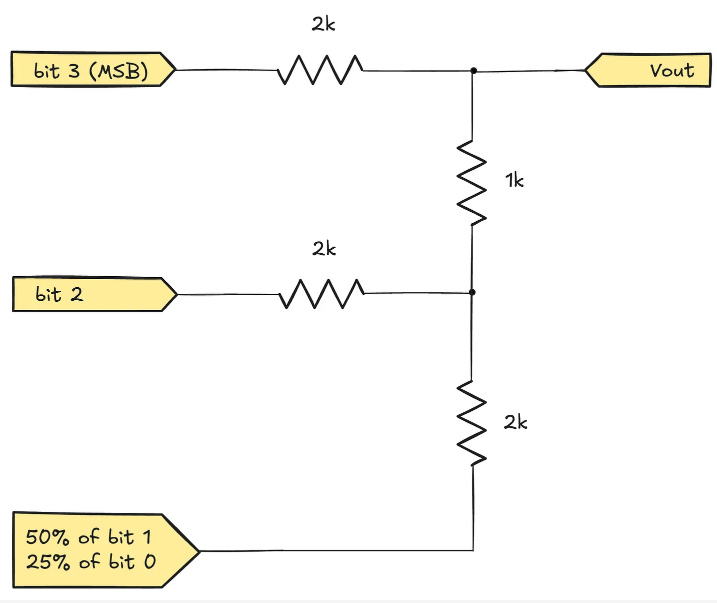

此時可發現,新電路中比特位#1的配置情況與先前對比特位#0的分析具有相似性。其底層結構包含一個連接對應二進制輸入的 2 kΩ 電阻,以及另一個連接前級合成電壓的 2 kΩ 電阻。實際上,該結構實現了兩種信號的50%混合效應。無論上層電路如何變化,此部分均可等效替換為連接新合成輸入信號的單個 1 kΩ 電阻:

此迭代過程可持續推進。最終可明確推導出:輸出電壓將由比特位#3貢獻50%,比特位#2貢獻25%,比特位#1貢獻12.5%,比特位#0貢獻6.25%。

(需說明的是,上述權重之和未達100%,因為梯形結構底部的初始下拉電阻會損耗部分電壓區間。)

過采樣DAC

盡管前文討論的架構簡潔優雅,但在高分辨率(尤其是超過10-12位)場景下會面臨線性度挑戰。雖然電阻元件精度可達0.1%級別,但在16位數模轉換器中,最低有效位(LSB)的理論影響權重僅為最高有效位(MSB)的0.003%。若MSB電阻值與設計值存在0.1%偏差,就足以導致整個系統的線性度嚴重劣化。

這一困境催生了過采樣平均型DAC的研發。此類器件通過高頻輸出低分辨率交替信號,隨后利用輸出端的低通濾波器對信號進行平均化處理,從而生成更精細的低頻中間電壓。

舉例說明:對四個連續的單比特DAC輸出進行平均處理,可在原生輸出范圍間插入三個中間電壓值,相當于獲得兩位有效精度提升:

平均(0,0,0,0)=0平均(0,0,0,1)=0.25平均(0,1,0,1)=0.5平均(0,1,1,1)=0.75平均(1,1,1,1)=1

當然,這種方案需要付出代價:部分高頻噪聲難以被濾波器完全抑制。盡管如此,該方案整體上相當穩健。事實上,消費級音頻設備中大量DAC采用單比特脈沖序列(工作頻率達數十萬赫茲)來實現宣稱的24位輸出分辨率。雖然電路本底噪聲往往使該指標的實際意義有限,但單比特DAC的線性度表現極佳——因為精確時序控制遠比制造超精密電阻容易實現。

經典模數轉換器(ADC)

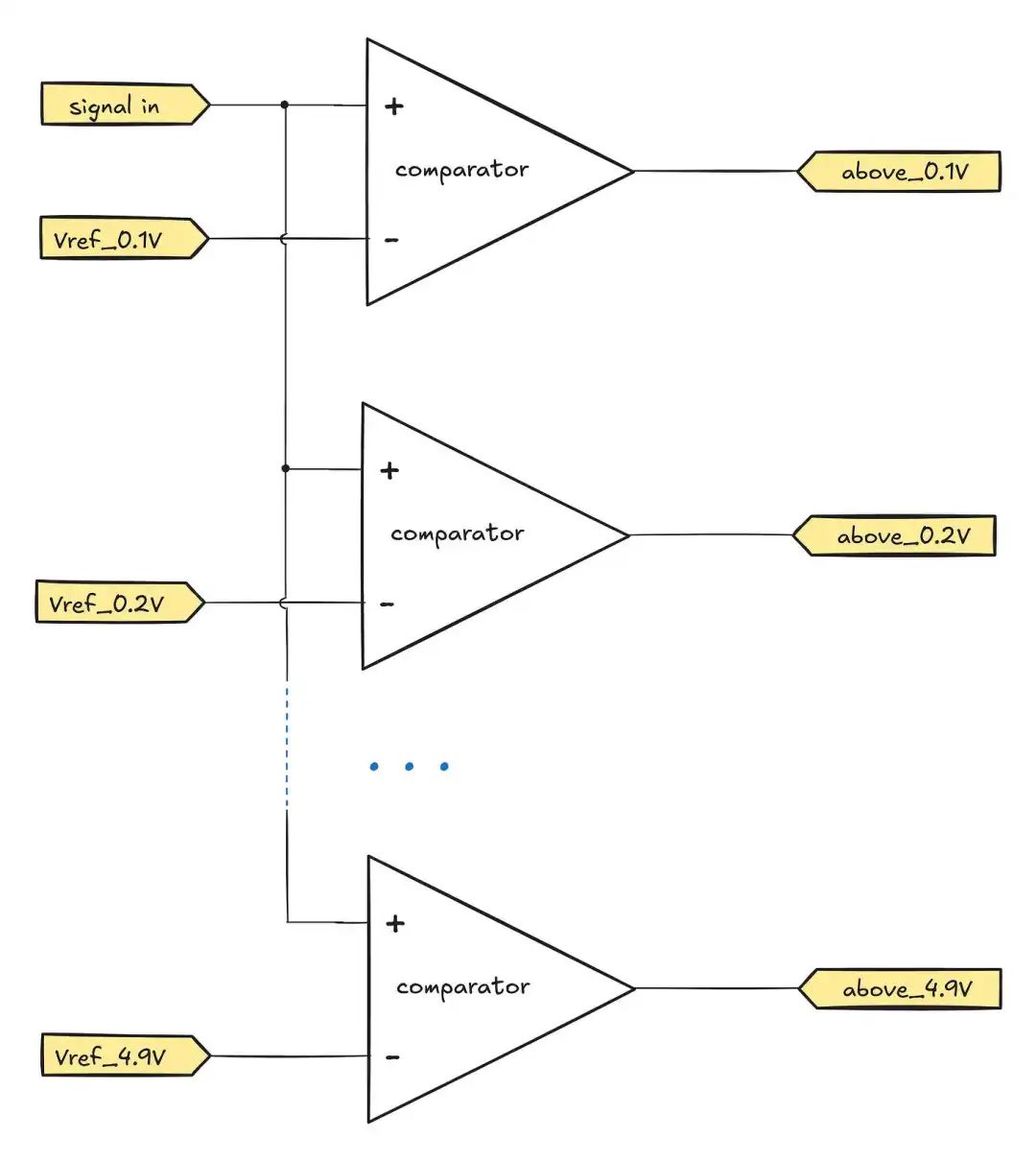

相較于數模轉換,將模擬電壓轉換為二進制數的過程更為復雜。要實現精準的瞬時電壓量化,唯一實用的方法是針對每個量化層級配置獨立的電壓比較器(開環運算放大器),例如:

并聯比較型ADC(也叫"flash" ADC)在需要極致速度的特殊場景中偶有應用,但其電路規模隨位數呈指數級增長——芯片功耗、輸入電容等參數隨之急劇惡化。因此這類ADC的分辨率通常不超過4-8位。

更常見的架構是采用單一比較器與可預測變化的參考電壓協同工作。一個基礎實例是通過電阻對電容充電的電路:通過測量充電開始到比較器觸發的時間間隔,即可反推出輸入電壓值。

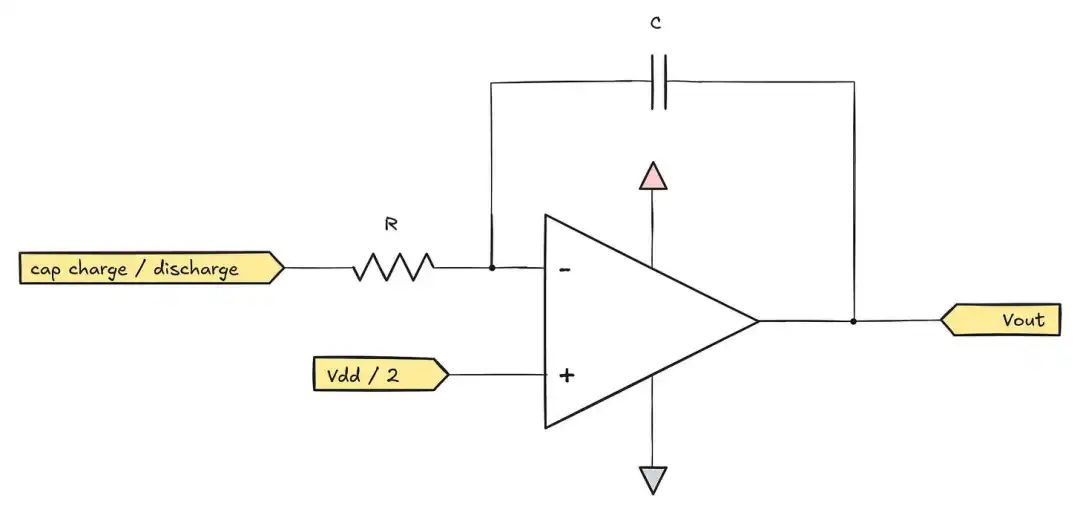

實踐中,由于電容恒壓充電曲線具有非線性特性,通常改用積分器電路生成參考信號:

積分器是在標準運放電路中引入一個有趣的微調:用反饋電容替代常規反饋電阻。當反相輸入端(Vin-)電壓高于同相端(Vin+)時,運放輸出端電壓立即下降,允許充電電流流經電阻 R 對電容充電。

該反饋機制的核心是維持 Vin- 與 Vin+ 電位相等。根據歐姆定律,在固定輸入電阻下,充電電流僅由輸入電壓和電阻 R 決定。當充電電流恒定時,電容電壓呈線性上升特性。若輸入方波信號,積分器將輸出近乎完美的三角波,這為ADC提供了極為理想的線性參考信號。

充電開始到比較器觸發的時間間隔不僅取決于輸入電壓,還與三角波斜率相關,而斜率本身受 R 和 C 參數精度制約。為提高精度,ADC 需測量三角波多個周期內比較器輸出信號的占空比。例如,25% 占空比意味著被測電壓處于 Vdd 的 75% 處,該測量結果與R、C精度無關。

基于斜率積分的 ADC 具備高精度與低噪聲優勢,但存在轉換速度緩慢的缺陷。性能優化的解決方案是采用數字輔助技術:即逐次逼近寄存器(SAR)架構。其核心原理是通過內置 DAC 生成參考電壓,并執行類似計算機科學中二分查找的算法:首先將輸入電壓與 Vdd/2 比較,若輸入更高則排除下半區間,隨后在剩余區間的中值(3/4 Vdd)處進行下一輪比較。通過逐次對半壓縮搜索范圍,僅需數次迭代即可鎖定精確值。代價是受DAC線性誤差影響存在精度損失,且數字開關噪聲有所增加。

高端("流水線")ADC常采用多技術融合方案:例如先通過 "flash" ADC 架構快速確定部分高位,再通過多級縮放與轉換處理獲取更多低位數據。

Delta-sigma(Δ-Σ) ADC

至此,ADC技術已展現出多樣化的實現路徑,但最精妙的方案當屬高頻插值法,通常采用 Δ-Σ(Delta-Sigma)調制技術。其工作機制頗具反常規特性。

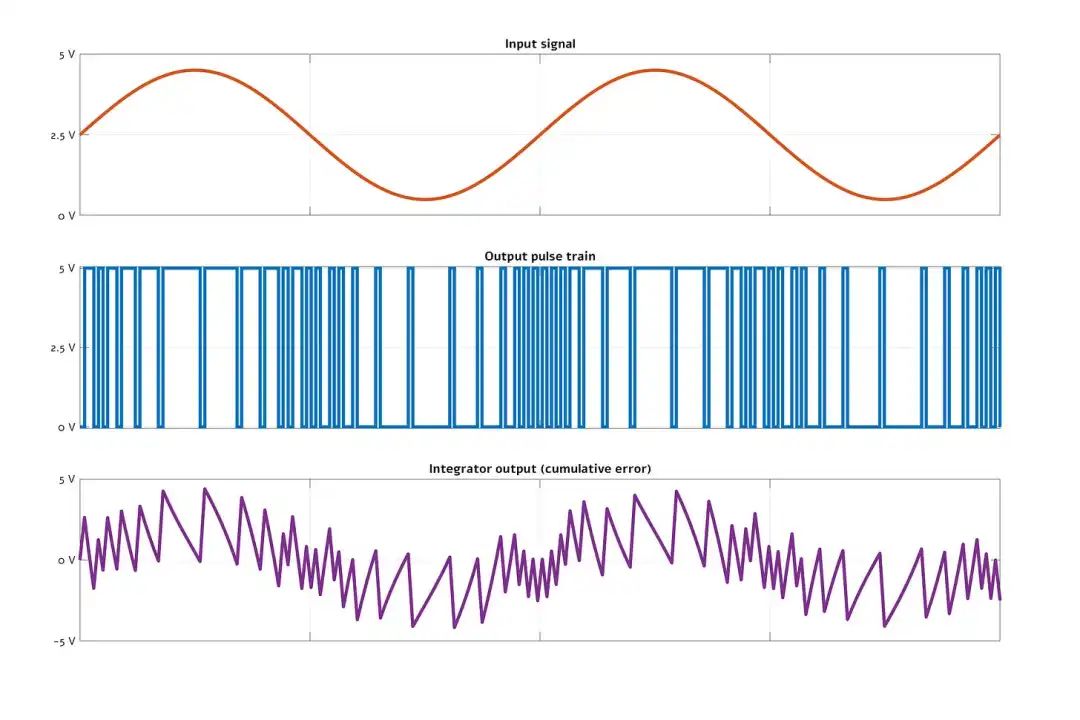

基礎型1位Δ-Σ ADC通過比較器級高速輸出"0"或"1"邏輯脈沖序列。這些數字輸出被引入特殊反饋回路,用于計算二進制輸出與輸入信號的差異:

簡化版1位Δ-Σ ADC架構示意圖(時鐘信號省略)

在多數情況下,模擬輸入電壓并不等于數字輸出的兩種可能電壓值,因此位于Δ-Σ ADC前端(左圖)的增益為1的運放會輸出瞬時大幅正向或負向誤差電壓。

這些瞬時誤差隨后輸入積分器。如本文前文所述,積分器通過對誤差進行時間積分(將累計值存儲在線性充電的電容中)實現誤差累積。若輸入信號正向偏離脈沖序列的平均值,積分器輸出電壓將逐步攀升;反之則逐漸下降。

該累計誤差最終輸入至產生實際輸出比特流的正相端比較器。其核心邏輯在于:若誤差為正(即ADC輸出"0"過多),比較器將強制輸出"1";反之若累計誤差為負(輸出"1"過多),則轉向輸出"0":

一階Δ-Σ ADC典型工作波形

盡管這種測量方式看似非理性,但通過數字處理看似混沌的高頻脈沖占空比,即可精確反推出模擬輸入值。該架構的最大優勢在于模擬誤差源極少,因此線性度表現卓越。代價則是為實現合理精度,ADC工作時鐘頻率需遠高于目標采樣率。

需特別說明的是,"Δ-Σ"術語也用于指代前文所述的過采樣插值型DAC子類。但與ADC相比,這類DAC的智能程度顯著降低:其脈沖調制主要發生在數字域,缺乏精妙的模擬反饋機制。

原文轉載自:https://lcamtuf.substack.com/p/dacs-and-adcs-or-there-and-back-again,經過翻譯及校驗

-

adc

+關注

關注

99文章

6670瀏覽量

548634 -

dac

+關注

關注

43文章

2393瀏覽量

193274 -

模擬

+關注

關注

7文章

1437瀏覽量

84418 -

數字

+關注

關注

1文章

1698瀏覽量

51798 -

KiCAD

+關注

關注

5文章

247瀏覽量

9395

發布評論請先 登錄

混合信號設備接地須知 ADC的數字地DGND模擬地AGND接地謎團

高速ADC/DAC在現代全數字雷達中的應用

DAC 與 ADC:數字與模擬的往復之旅

如何挑選ADC和DAC?

ADC與DAC的原理參考電壓

ADC/DAC,ADC/DAC的原理是什么?

什么是DAC_adc是什么意思

DAC 與 ADC:數字與模擬的往復之旅

DAC 與 ADC:數字與模擬的往復之旅

評論