一、PCIe協議與參考時鐘要求

1、PCIe是什么?

PCI Express(Peripheral Component Interconnect Express)是一種高性能、高帶寬的串行總線標準,用于連接計算機內部的各種硬件設備,如顯卡、存儲設備(SSD)、網卡等。它取代了傳統的 PCI 和 AGP 總線,并以其高速度、低延遲和強擴展性成為現代計算機系統的核心互聯技術。

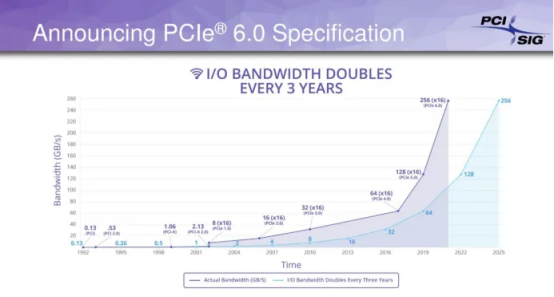

PCIe 支持多種速率版本,包括 PCIe 1.0、PCIe 2.0、PCIe 3.0、PCIe 4.0、PCIe 5.0和PCIe 6.0,每個版本都在前一代的基礎上實現了帶寬的翻倍。

PCIe 6.0已于2022年發布,其單通道速率提升至64 GT/s,并引入PAM4調制技術,帶寬再次翻倍。同時,PCIe 6.0還增加了FEC(前向糾錯)功能,以應對高速傳輸中的信號衰減問題。

圖1:PCIE 6.0協議標準

圖1:PCIE 6.0協議標準2、PCIe參考時鐘的關鍵作用

在PCIe系統中,參考時鐘(Reference Clock)是確保數據傳輸準確性和穩定性的核心組件。其主要作用包括:

· 同步數據傳輸:為SerDes(串行器/解串器)提供精準時鐘信號,確保發送端與接收端同步。

· 降低誤碼率:高精度時鐘減少信號抖動,降低數據傳輸誤碼率(BER)。

· 支持多設備協同:在CXL、NVMe-oF等復雜架構中,參考時鐘需實現多設備間的相位對齊。

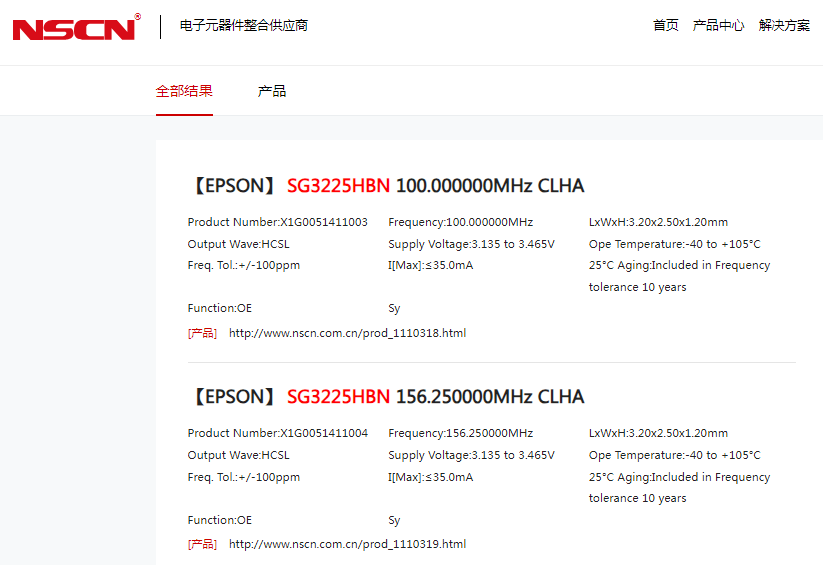

PCIE協議下的參考時鐘基本為100MHz HCSL輸出,要求確保數據傳輸的正確性和穩定性,解決時鐘抖動、偏移和噪聲問題。

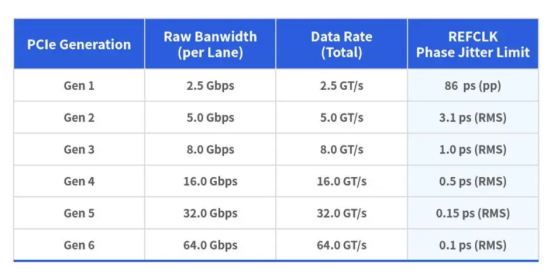

隨著PCIe版本的升級,參考時鐘的性能要求也大幅提高,下表展示了不同PCIe協議版本對于參考時鐘RMS抖動的要求:

表1:不同PCIe協議版本對于參考時鐘RMS抖動的要求

表1:不同PCIe協議版本對于參考時鐘RMS抖動的要求二、YXC HCSL輸出差分晶振:滿足PCIe 5.0時鐘需求的理想選擇

為應對PCIe 5.0對參考時鐘的嚴苛要求,推薦使用揚興科技YXC差分振蕩器YSO230LR系列和YSO231LJ系列。這兩款產品憑借卓越的性能和可靠性,成為PCIe 5.0參考時鐘的理想選擇。

YSO230LR差分晶振

YSO230LR差分晶振 YSO231LJ超低抖動差分晶振

YSO231LJ超低抖動差分晶振YXC產品優勢:

· 超低抖動:相位抖動可達0.05ps(typ.) RMS,滿足PCIe 5.0的嚴苛要求,確保信號完整性;

· 高穩定度:總頻差最優可達±25ppm @ -40~﹢85℃;

· 差分輸出:支持HSCL、LVDS、LVPECL等多種差分輸出;

· 小型化:提供2.5*2.0mm緊湊設計,適配高密度主板布局;

· 寬溫范圍:提供-40℃~﹢105℃、-40℃~﹢125℃等寬廣的工作溫度選項。

-

有源晶振

+關注

關注

1文章

931瀏覽量

21329 -

晶振

+關注

關注

35文章

3260瀏覽量

70076 -

PCIe

+關注

關注

16文章

1340瀏覽量

85116 -

PCIe5.0

+關注

關注

0文章

29瀏覽量

1668 -

差分晶振

+關注

關注

0文章

146瀏覽量

731

發布評論請先 登錄

27MHz HCSL晶體振蕩器選型與PHY對接設計指南

27MHz HCSL 差分晶體振蕩器在數據中心網絡存儲系統中的應用方案

從SerDes到SoC,全場景適配的FCom差分晶振設計全解

差分輸出VCXO振蕩器 | FCom富士晶振 - 低抖動時鐘解決方案

MG7050HAN 基于聲表的差分多輸出 晶體振蕩器(HCSL)

愛普生6G路由器晶振MG7050HAN,HCSL輸出有源晶振,X1M0004310007

差分輸出VCXO振蕩器 | FCom富士晶振 - 低抖動時鐘解決方案

YXC低抖動HCSL差分晶振助力PCIE 5.0

YXC低抖動HCSL差分晶振助力PCIE 5.0

評論