概述

AD9546 采用數(shù)字化時(shí)鐘技術(shù),可在系統(tǒng)中高效傳輸和分配時(shí)鐘信號(hào)。數(shù)字化時(shí)鐘具有設(shè)計(jì)靈活性,且可使用可擴(kuò)展的時(shí)鐘傳輸系統(tǒng),并具有良好的相位(時(shí)間)對(duì)齊控制。這些特性使 AD9546 成為必須滿足 ITU-T G.8273.2 D 類(lèi)的 IEEE^?^ 1588^?^ 邊界時(shí)鐘的同步要求的網(wǎng)絡(luò)設(shè)備設(shè)計(jì)的首選。數(shù)字時(shí)鐘還與要求將頻率和相位精確傳輸?shù)蕉鄠€(gè)使用端點(diǎn)的應(yīng)用有關(guān)(例如,將同步系統(tǒng)參考 (SYSREF) 時(shí)鐘分配到 ADC 通道陣列)。

AD9546 支持現(xiàn)有和新興的國(guó)際電信聯(lián)盟 (ITU) 標(biāo)準(zhǔn),通過(guò)服務(wù)提供商分組網(wǎng)絡(luò),可交付頻率、相位和時(shí)刻,這些分組網(wǎng)絡(luò)包括 ITU-G.8262、ITU-T G.812、ITU-T G.813、ITU-T G.823、ITU-T G.824、ITU-T G.825 和ITU-T G.8273.2。

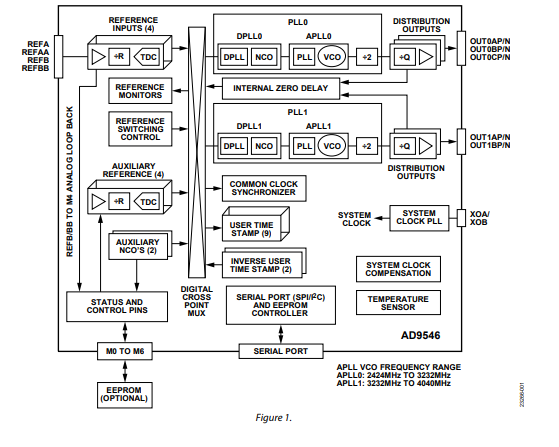

將 AD9546 的 10 個(gè)時(shí)鐘輸出同步為多達(dá)八個(gè)輸入基準(zhǔn)電壓源中的任意一個(gè)。數(shù)字鎖相環(huán) (DPLL) 減少了與外部基準(zhǔn)電壓源相關(guān)的時(shí)序抖動(dòng),而模擬鎖相環(huán) (APLL) 提供了具有低抖動(dòng)輸出時(shí)鐘的頻率轉(zhuǎn)換。數(shù)字控制的環(huán)路和保持電路即使在所有參考輸入失敗時(shí)仍可持續(xù)產(chǎn)生低抖動(dòng)輸出信號(hào)。

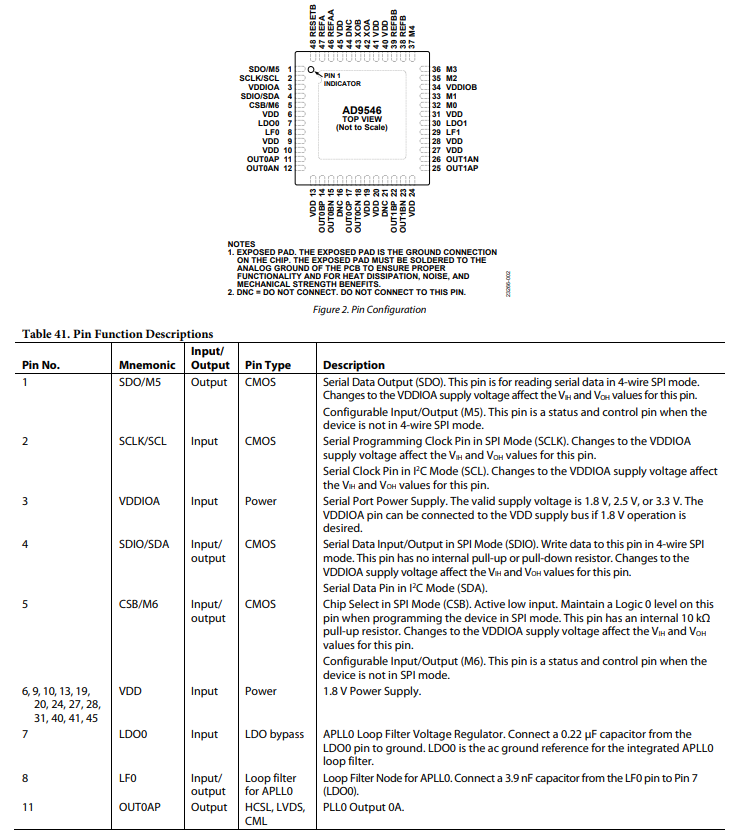

AD9546 提供 48 引腳 LFCSP (7 mm × 7 mm) 封裝,可在 ?40°C 至 +85°C 的溫度范圍內(nèi)工作。

在整個(gè)數(shù)據(jù)手冊(cè)中,當(dāng)僅涉及多功能引腳名稱的單個(gè)功能時(shí)(例如,針對(duì)SDO/M5 的 M5),可參考該功能。

數(shù)據(jù)表:*附件:AD9546雙DPLL數(shù)字時(shí)鐘同步器技術(shù)手冊(cè).pdf

應(yīng)用

- 5G 時(shí)序傳輸高精度同步

- 全球定位系統(tǒng) (GPS)、精確時(shí)間協(xié)議 PTP (IEEE 1588) 和同步以太網(wǎng) (SyncE) 抖動(dòng)濾除和同步

- 光傳送網(wǎng)絡(luò) (OTN)、同步數(shù)字體系 (SDH) 以及宏基站和小蜂窩基站。小型基站時(shí)鐘(基帶和射頻)

- Stratum 2、Stratum 3e 和 Stratum 3 保持、去除信號(hào)抖動(dòng)和相位瞬態(tài)控制

- JESD204B 支持模數(shù)轉(zhuǎn)換器 (ADC) 和數(shù)模轉(zhuǎn)換器 (DAC) 時(shí)鐘

- 運(yùn)營(yíng)商級(jí)以太網(wǎng)

特性

- 數(shù)字時(shí)鐘傳輸子系統(tǒng)

- 9 個(gè)獨(dú)立的 UTS 塊(時(shí)間戳出口)

- 2 個(gè)獨(dú)立的 IUTS 塊(時(shí)間戳入口)

- 雙 DPLL 可同步 1 Hz 到 750 MHz 物理層時(shí)鐘,可在提供頻率轉(zhuǎn)換的同時(shí)去除噪聲基準(zhǔn)電壓源的信號(hào)抖動(dòng)

- 符合 ITU-T G.8262 和 Telcordia GR-253 標(biāo)準(zhǔn)

- 支持 Telcordia GR-1244、ITU-T G.812、ITU-T G.813、ITU-T G.823、ITU-T G.824、ITU-T G.825 和 ITU-T G.8273.2

- 針對(duì)低至 50 ppb (5 × 10

?8) 的頻率偏移,可進(jìn)行持續(xù)頻率監(jiān)控和基準(zhǔn)電壓源驗(yàn)證 - 兩個(gè) DPLL 都配有帶有 24 位可編程模塊的 24 位小數(shù)分頻器

- 可編程數(shù)字環(huán)路濾波器帶寬:0.0001 Hz 至 1850 Hz

- 兩個(gè)獨(dú)立的可編程輔助 NCO(1 Hz 至 65,535 Hz,分辨率 < 1.37 pHz),適合 PTP 應(yīng)用中的 IEEE-1588 第 2 版伺服反饋

- 自動(dòng)和手動(dòng)保持和基準(zhǔn)電壓源切換,實(shí)現(xiàn)零延遲、無(wú)中斷或相位增建

- 基于可編程優(yōu)先級(jí)的基準(zhǔn)電壓源切換,支持手動(dòng)、自動(dòng)可逆和自動(dòng)不可逆模式

- 5 對(duì)時(shí)鐘輸出引腳,每對(duì)都可用作差分 LVDS/HCSL/CML 或用作 2 個(gè)單端輸出(1 Hz 至 500 MHz)

- 2 個(gè)差分或 8 個(gè)單端輸入基準(zhǔn)電壓源

- 交叉點(diǎn)多路復(fù)用器將參考輸入與 PLL 互連

- 支持嵌入式(模塊化)輸入/輸出時(shí)鐘信號(hào)

- 快速 DPLL 鎖定模式

- 提供內(nèi)部功能,可兼具晶體諧振器或晶體振蕩器的低相位噪聲特點(diǎn),以及 TCXO 或 OCXO 的頻率穩(wěn)定性和精度

- 針對(duì)自主初始化提供外部 EEPROM 支持

- 1.8 V 單電源供電,帶有內(nèi)部調(diào)節(jié)功能

- 內(nèi)置溫度監(jiān)視器/警報(bào)和溫度補(bǔ)償,可增強(qiáng)零延遲性能

框圖

引腳配置描述

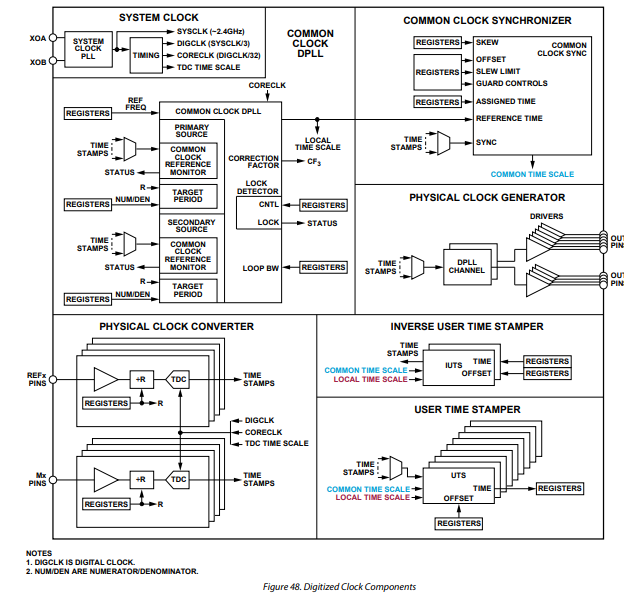

數(shù)字化時(shí)鐘技術(shù)可實(shí)現(xiàn)精確的定時(shí)傳輸(頻率和相位),在空間上分離的設(shè)備之間通過(guò)數(shù)字時(shí)間碼進(jìn)行同步(假設(shè)所有設(shè)備都能訪問(wèn)公共參考時(shí)鐘信號(hào))。

數(shù)字化時(shí)鐘系統(tǒng)由多個(gè)定時(shí)節(jié)點(diǎn)組成,每個(gè)節(jié)點(diǎn)依賴于共享的外部時(shí)基(公共時(shí)鐘參考)。由于每個(gè)節(jié)點(diǎn)共享相同的公共時(shí)鐘參考,且節(jié)點(diǎn)增量以相同速率變化,因此所有節(jié)點(diǎn)都具有相同的時(shí)間尺度。盡管所有節(jié)點(diǎn)都處于同一尺度,但并不能保證它們共享同一時(shí)刻。數(shù)字化時(shí)鐘依賴于用戶在每個(gè)節(jié)點(diǎn)設(shè)置的同步信號(hào),最終使所有節(jié)點(diǎn)實(shí)現(xiàn)時(shí)間對(duì)齊。數(shù)字化時(shí)鐘的一個(gè)獨(dú)特特性是能夠通過(guò)數(shù)字總線在節(jié)點(diǎn)之間交換數(shù)字時(shí)間碼,這意味著可以向一個(gè)或多個(gè)數(shù)字總線(時(shí)鐘聚合)發(fā)送多個(gè)時(shí)鐘,以路由多個(gè)模擬時(shí)鐘信號(hào)來(lái)構(gòu)建系統(tǒng)。AD9546包含實(shí)現(xiàn)數(shù)字化時(shí)鐘節(jié)點(diǎn)所需的所有構(gòu)建模塊。

圖48展示了AD9546中實(shí)現(xiàn)的完整數(shù)字化時(shí)鐘節(jié)點(diǎn)的各個(gè)組件。這些數(shù)字化時(shí)鐘組件包括:

- 系統(tǒng)時(shí)鐘PLL,用于生成系統(tǒng)時(shí)鐘頻率,以實(shí)現(xiàn)內(nèi)部定時(shí)功能(詳見(jiàn)“系統(tǒng)時(shí)鐘PLL”部分)

- 公共時(shí)鐘DPLL,用于與參考時(shí)基(公共時(shí)鐘參考)進(jìn)行鎖相,并維持本地時(shí)間尺度

- 物理時(shí)鐘轉(zhuǎn)換器,用于將系統(tǒng)時(shí)鐘的時(shí)間戳轉(zhuǎn)換為物理時(shí)鐘

- 物理時(shí)鐘發(fā)生器,用于將從公共時(shí)間尺度導(dǎo)出的時(shí)間戳轉(zhuǎn)換為物理時(shí)鐘輸出信號(hào)

- ACCS,通過(guò)為本地時(shí)間尺度分配時(shí)刻來(lái)創(chuàng)建公共時(shí)間尺度

- UTS,用于將內(nèi)部時(shí)間戳轉(zhuǎn)換為基于公共時(shí)間尺度的時(shí)間碼,并將這些時(shí)間碼提供給用戶用于外部使用

- IUTS,用于將用戶提供的基于公共時(shí)間尺度的一系列時(shí)間碼轉(zhuǎn)換為內(nèi)部時(shí)間戳

圖48展示了多種時(shí)間戳源。某些數(shù)字化時(shí)鐘組件需要能夠連接到任意一個(gè)時(shí)間戳源,這就是為什么這些組件在其輸入處包含時(shí)間戳選擇多路復(fù)用器。

系統(tǒng)時(shí)鐘PLL組件

系統(tǒng)時(shí)鐘PLL通常使用外部晶體諧振器作為頻率源,這往往能提供最佳的整體相位噪聲性能。系統(tǒng)時(shí)鐘PLL從外部頻率源(約2.4GHz)合成高頻內(nèi)部系統(tǒng)時(shí)鐘信號(hào),為設(shè)備提供基本的內(nèi)部定時(shí)。設(shè)備使用系統(tǒng)時(shí)鐘來(lái)生成時(shí)間戳(詳見(jiàn)“時(shí)間數(shù)字轉(zhuǎn)換器(TDC)”部分)。

請(qǐng)注意,內(nèi)部系統(tǒng)時(shí)鐘信號(hào)是公共時(shí)鐘DPLL組件用于生成本地時(shí)間尺度的兩個(gè)頻率源之一。

公共時(shí)鐘DPLL組件

公共時(shí)鐘DPLL的作用是生成本地時(shí)間尺度。公共時(shí)鐘DPLL使用系統(tǒng)時(shí)鐘進(jìn)行內(nèi)部定時(shí),但其相位鎖定到參考時(shí)基,即公共時(shí)鐘參考。公共時(shí)鐘DPLL的輸出是本地時(shí)間尺度,它累積了公共時(shí)鐘參考的周期,并為數(shù)字化時(shí)鐘組件提供內(nèi)部時(shí)間感知。

公共時(shí)鐘DPLL固有的閉環(huán)架構(gòu)意味著其運(yùn)行會(huì)產(chǎn)生誤差,校正因子3(CF3)有效地補(bǔ)償了系統(tǒng)時(shí)鐘的波動(dòng)。請(qǐng)注意,CF3信號(hào)可用于AD9546的系統(tǒng)時(shí)鐘補(bǔ)償功能模塊(詳見(jiàn)“補(bǔ)償方法3”部分)。

物理時(shí)鐘轉(zhuǎn)換器

物理時(shí)鐘轉(zhuǎn)換器有一個(gè)輸入,用于接收外部時(shí)鐘信號(hào),提供可選的整數(shù)頻率分頻功能,并將上升沿時(shí)鐘轉(zhuǎn)換為數(shù)字時(shí)間戳。然后,這些時(shí)間戳可供需要時(shí)間戳源的數(shù)字化時(shí)鐘組件使用。

物理時(shí)鐘發(fā)生器

物理時(shí)鐘發(fā)生器利用AD9546的DPLL通道和輸出分配驅(qū)動(dòng)器,從時(shí)間戳生成模擬時(shí)鐘輸出信號(hào)。在數(shù)字化時(shí)鐘應(yīng)用中,時(shí)間戳源自公共時(shí)間尺度。由于DPLL可以從這些時(shí)間戳中獲取其參考輸入,因此物理時(shí)鐘發(fā)生器的輸出由模擬時(shí)鐘信號(hào)組成。

-

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132895 -

DPLL

+關(guān)注

關(guān)注

1文章

26瀏覽量

14190 -

數(shù)字化

+關(guān)注

關(guān)注

8文章

9326瀏覽量

63120

發(fā)布評(píng)論請(qǐng)先 登錄

DAY-1000數(shù)字音頻同步器

基于FPGA的提取位同步時(shí)鐘DPLL設(shè)計(jì)

同步器的作用

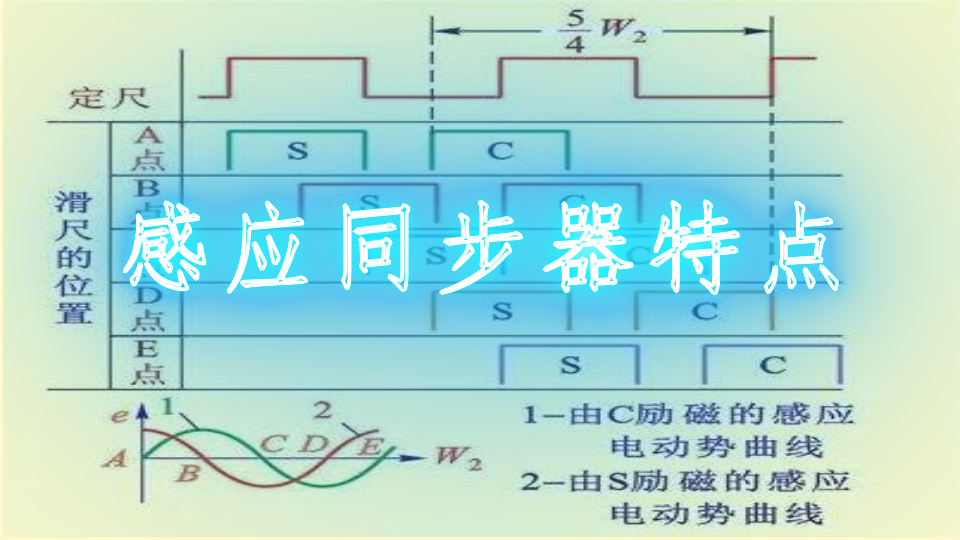

感應(yīng)同步器特點(diǎn)

單錐、雙錐、三錐同步器到底有什么區(qū)別

AD9546: Dual DPLL Digitized Clock Synchronizer Data Sheet

AD9546:雙DPLL數(shù)字化時(shí)鐘同步器數(shù)據(jù)表

AD9547:雙/四輸入網(wǎng)絡(luò)時(shí)鐘發(fā)生器/同步器數(shù)據(jù)表

AD9542:四輸入、五輸出、雙DPLL同步器和自適應(yīng)時(shí)鐘轉(zhuǎn)換器產(chǎn)品手冊(cè)

AD9543:四路輸入、10路輸出、雙DPLL/IEEE 1588同步器和抖動(dòng)清除器

LMK5B33216 3 DPLL、3 APLL、2路輸入、16路輸出網(wǎng)絡(luò)同步器數(shù)據(jù)表

AD9546雙DPLL數(shù)字時(shí)鐘同步器技術(shù)手冊(cè)

AD9546雙DPLL數(shù)字時(shí)鐘同步器技術(shù)手冊(cè)

評(píng)論