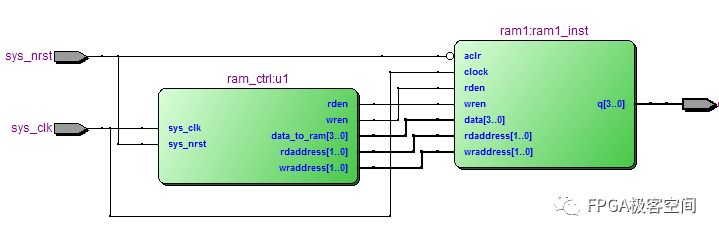

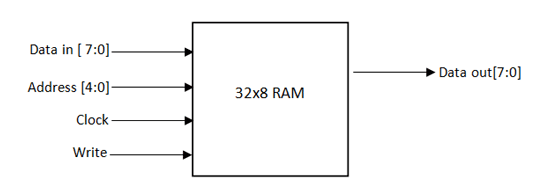

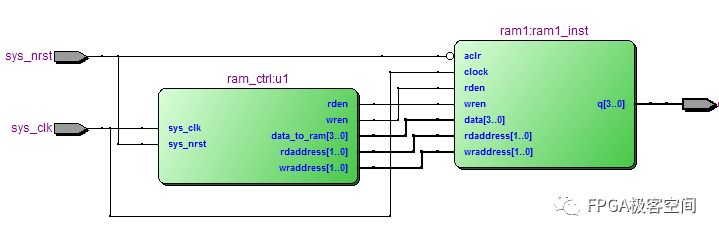

FPGA中RAM的使用探索。以4bitX4為例,數(shù)據(jù)位寬為4,深度為4。

第一種方式,直接調(diào)用4bitX4的RAM。編寫控制邏輯對齊進行讀寫。

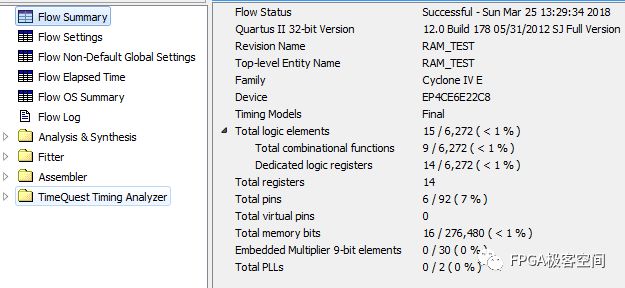

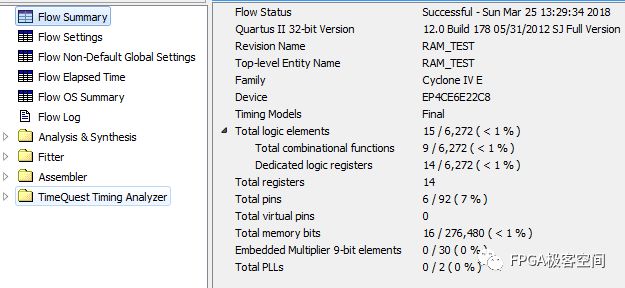

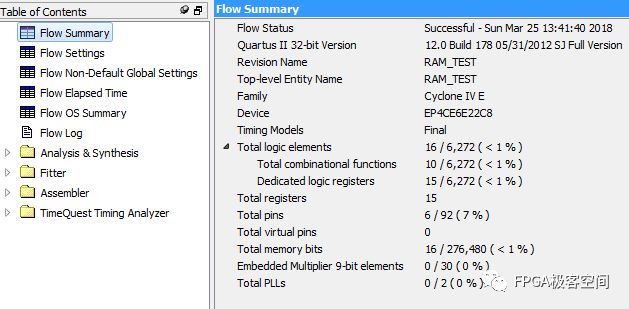

quartus ii 下的編譯,資源消耗情況。

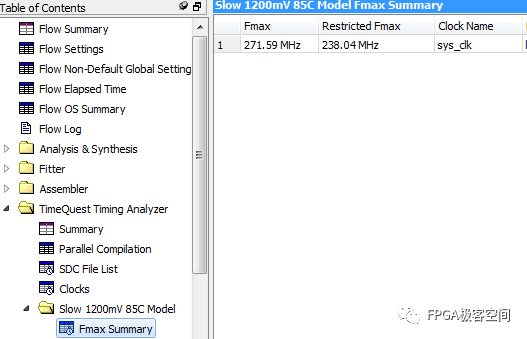

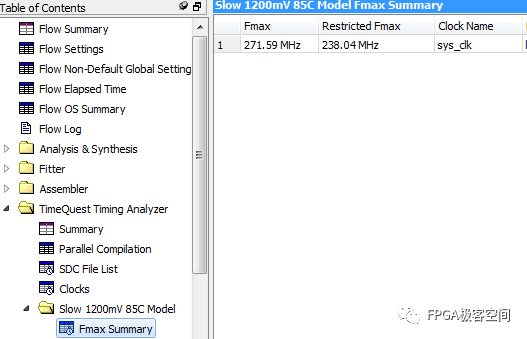

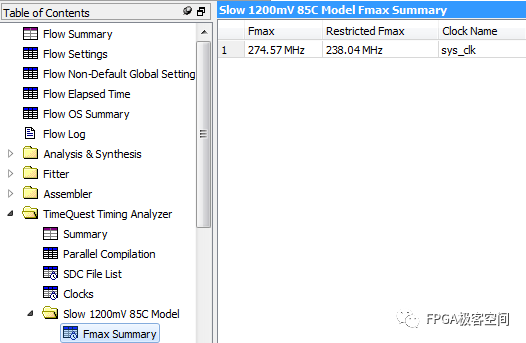

85C模型下的時鐘頻率。

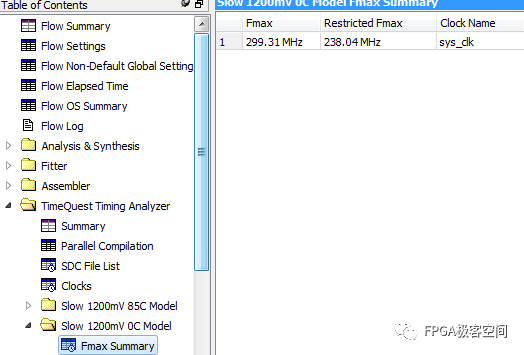

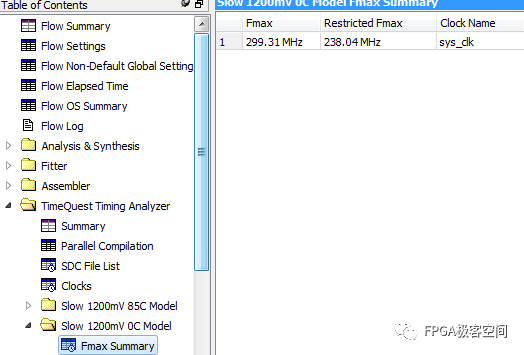

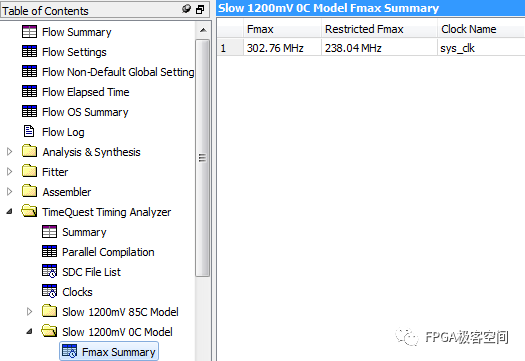

0C模型下的時鐘頻率。

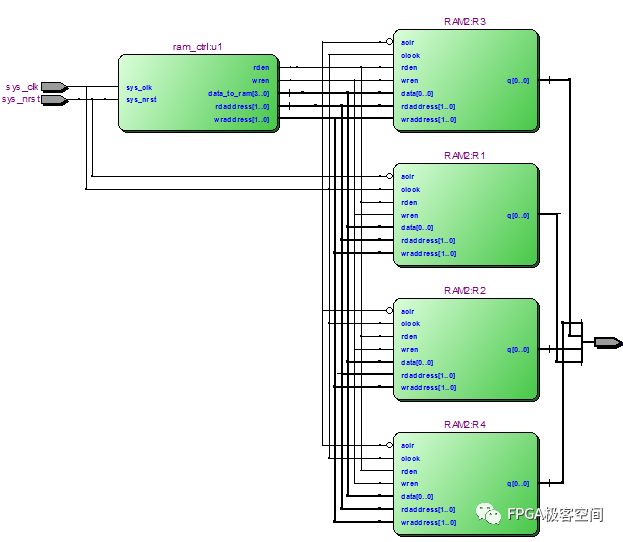

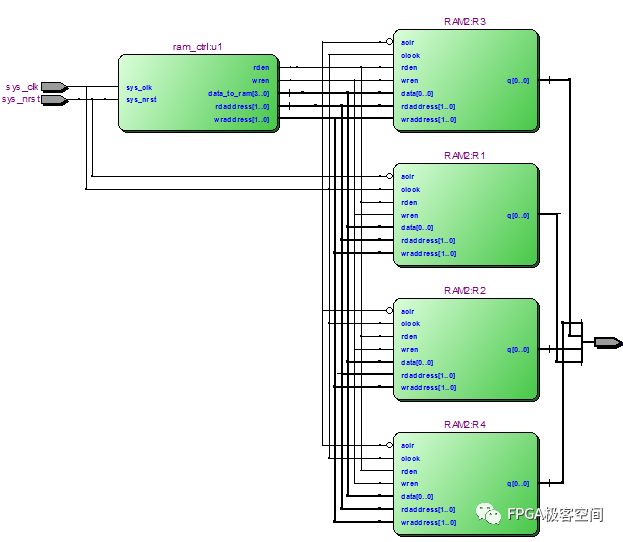

第二種方式,調(diào)用1bitX4的RAM,例化4次。編寫控制邏輯對齊進行讀寫。

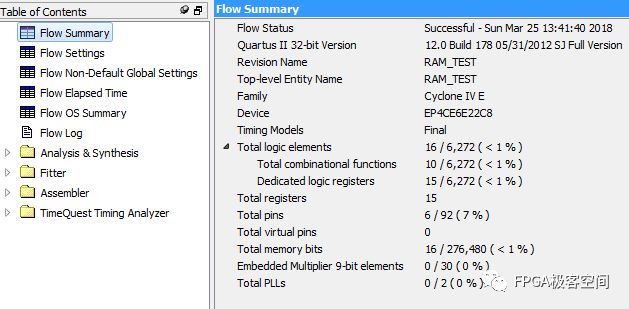

quartus ii 下的編譯,資源消耗情況。

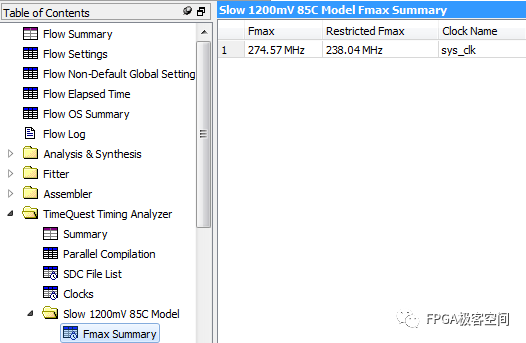

85C模型下的時鐘頻率。

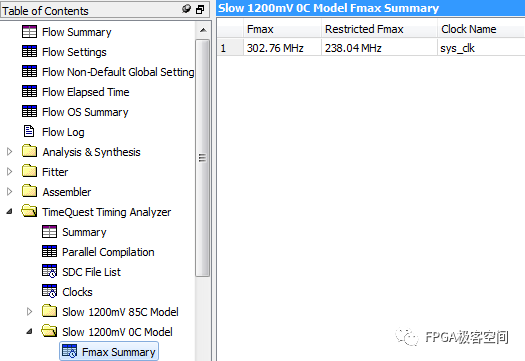

0C模型下的時鐘頻率。

從上述兩種情況來看,兩種RAM的使用方式,最終使用資源比較接近,方案二稍多,而從時序模型綜合結(jié)果看,方案二的時鐘頻率明顯比方案一高。在高速情況下,建議使用方案二。同樣在位寬較寬情況下,可使用生成塊語句進行例化,減少頂層對同一模塊的例化數(shù),是比較方便的。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

原文標題:FPGA中RAM使用探索

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

相關(guān)推薦

在選擇FPGA時,關(guān)注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因為它們是FPGA架構(gòu)中的兩個核心資源,對于設(shè)計的性能和資源利用至關(guān)重要。

![的頭像]() 發(fā)表于

發(fā)表于 11-21 15:03

?2770次閱讀

實現(xiàn)了不同的邏輯功能。查找表(Look-Up-Table) 簡稱為LUT,LUT 本質(zhì)上就是一個RAM。目前FPGA 中多使用4 輸入的LUT,所以每一個LUT 可以看成一個有4 位地址線的 的

發(fā)表于 08-23 09:14

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一個單獨的奇偶校驗寫使能位,但在FPGA RAM

發(fā)表于 04-24 09:37

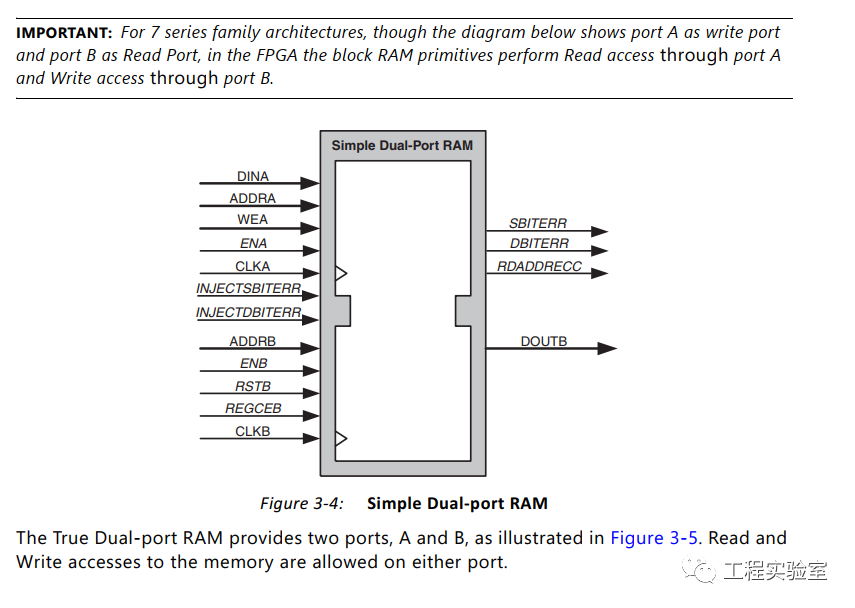

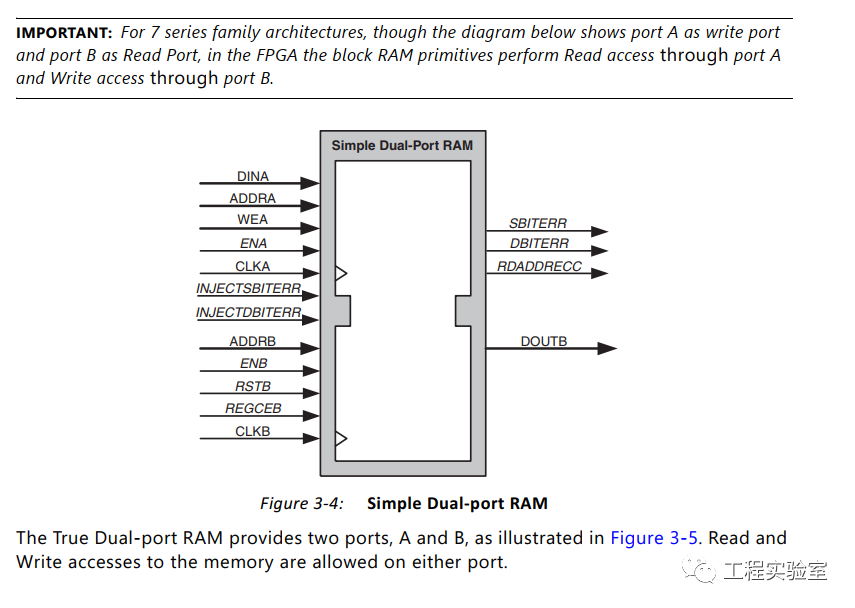

為了在高速采集時不丟失數(shù)據(jù),在數(shù)據(jù)采集系統(tǒng)和CPU之間設(shè)置一個數(shù)據(jù)暫存區(qū)。介紹雙口RAM的存儲原理及其在數(shù)字系統(tǒng)中的應(yīng)用。采用FPGA技術(shù)構(gòu)造雙口

發(fā)表于 02-11 11:20

?69次下載

在現(xiàn)代邏輯設(shè)計中,FPGA占有重要的地位,不僅因為具有強大的邏輯功能和高速的處理速度,同時因為其內(nèi)部嵌有大量的可配置的塊RAM,使其得到了廣泛地應(yīng)用,例如FFT算法的實現(xiàn)等。

發(fā)表于 09-27 17:07

?54次下載

本文介紹了如何在FPGA 中利用Block RAM 的特殊結(jié)構(gòu)實現(xiàn)HDTV視頻增強算法中灰度直方圖統(tǒng)計。

![的頭像]() 發(fā)表于

發(fā)表于 07-10 08:10

?2952次閱讀

本指南是描述所有Spartan-6 FPGA中可用的Spartan?6 FPGA塊RAM的技術(shù)參考。塊R

發(fā)表于 02-15 16:38

?13次下載

本文檔的主要內(nèi)容詳細介紹的是FPGA硬件基礎(chǔ)之FPGA的RAM存儲課件和工程文件。

發(fā)表于 12-10 15:27

?30次下載

在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優(yōu)化整個設(shè)計,節(jié)約資源利用率,充分開發(fā)FPGA芯片中的潛在價值,本文結(jié)合安路科技

![的頭像]() 發(fā)表于

發(fā)表于 12-24 14:28

?1349次閱讀

RAM),其中BRAM是block ram,是存在FPGA中的大容量的RAM,DRAM是FPGA

發(fā)表于 12-30 16:27

?9次下載

RAM是

FPGA中常用的基礎(chǔ)模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎(chǔ)。本實驗將為大家介紹如何使用

FPGA內(nèi)部的

RAM以及程序?qū)υ?/div>

![的頭像]() 發(fā)表于

發(fā)表于 02-08 15:50

?1.4w次閱讀

在本教程中,我們將探索如何使用 ModelSim 在 VHDL 中實現(xiàn) RAM。

發(fā)表于 07-29 16:34

?2797次閱讀

在FPGA 邏輯設(shè)計中經(jīng)常用到的數(shù)據(jù)存儲方式有ROM、RAM和FIFO,根據(jù)不同的應(yīng)用場景選擇不同的存儲方式。Xilinx 平臺三種存儲方式在使用過程中的區(qū)別如下。

![的頭像]() 發(fā)表于

發(fā)表于 08-22 16:12

?4475次閱讀

FPGA在一個時鐘周期可以讀取多個RAM數(shù)據(jù)嗎?如何理解FPGA中存放程序的RAM? FPGA在

![的頭像]() 發(fā)表于

發(fā)表于 10-18 15:28

?1414次閱讀

FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點是有兩組獨立的端口,可以對同一存儲塊進行讀寫操作,從而實現(xiàn)并行訪問。

![的頭像]() 發(fā)表于

發(fā)表于 03-15 13:58

?1128次閱讀

技術(shù)控:FPGA中RAM使用技巧探索

技術(shù)控:FPGA中RAM使用技巧探索

評論