概述

LTC 6603 是一款雙通道、匹配、可編程低通濾波器,適用于通信接收器和發送器。 LTC6603 的選擇性,再加上其線性相位、相位匹配和動態范圍,使其適合于許多通信系統中的濾波處理。 憑借通道之間的 1.5° 相位匹配精度,LTC6603 可以在那些需要匹配濾波器對的應用 (例如:收發器 I 和 Q 通道) 中使用。 此外,差分輸入和輸出還提供了一個適合于大多數通信系統的簡單接口。

采樣數據濾波器不需要使用一個外部時鐘,而且其截止頻率可以采用單個外部電阻器來設定 (準確度達 3.5% 或更高)。 該外部電阻器負責設置一個內部振蕩器,這個振蕩器在應用于濾波器網絡之前便被分頻。 這使得對于每個外部電阻器阻值可以獲得多達 3 種截止頻率,從而允許在一個超過 6 個倍頻程的范圍內設置截止頻率。 或者,也可以利用一個外部時鐘來設定濾波器截止頻率。 濾波器增益也可被設置為 1、2、4 或 16。

LTC6603 具有一種可通過串行接口來設置的低功率停機模式,并采用 24 引腳 4mm x 4mm QFN 封裝。

數據表:*附件:LTC6603雙通道、可調低通濾波器技術手冊.pdf

應用

特性

- 保證相位和增益匹配規格

- 可編程帶寬 (BW) 高達 2.5MHz

- 可編程增益 (0dB/6dB/12dB/24dB)

- 9 階線性相位響應

- 差分、軌至軌輸入和輸出

- 低噪聲:-145dBm/Hz (參考于輸入)

- 低失真:-75dBc (在200kHz)

- 簡單的引腳編程或 SPI 接口

- 可利用一個外部電阻器來設定最大速率/功率

- 工作電壓范圍:2.7V 至 3.6V

- 輸入范圍從 0V 至 5.5V

- 4mm x 4mm QFN 封裝

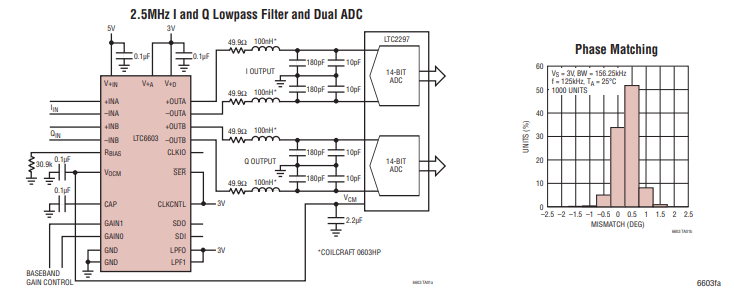

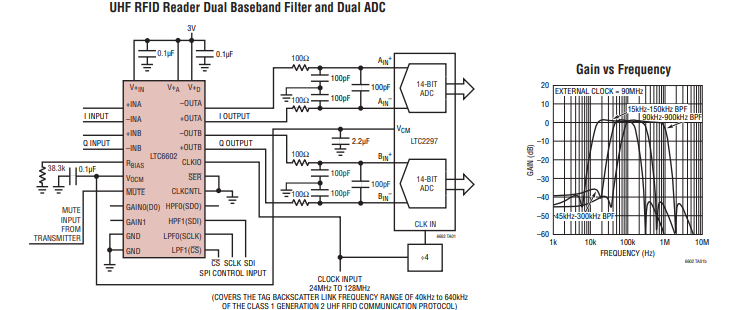

典型應用

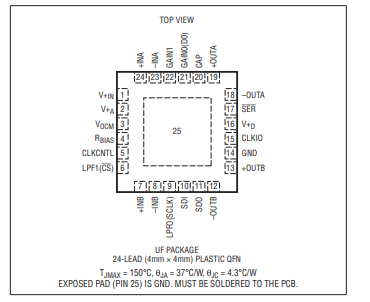

引腳配置描述

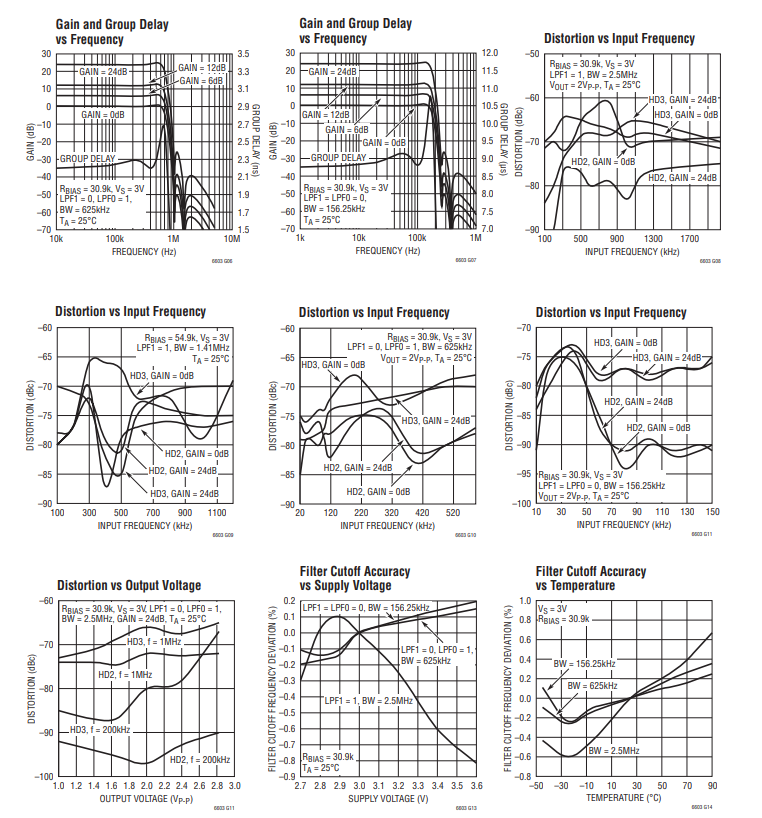

典型性能特征

典型性能特征

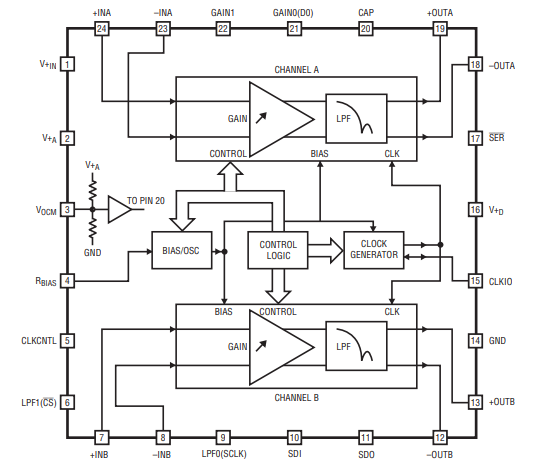

框圖

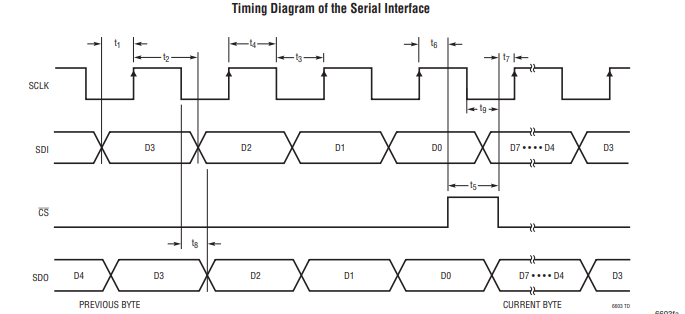

時序圖

應用信息

工作原理(參考框圖)

LTC6603具有兩個匹配的濾波器通道,每個通道都包含增益控制和低通濾波器網絡,由單個控制模塊控制,并由單個時鐘發生器提供時鐘信號。增益和截止頻率可以分別進行編程。這兩個通道并非相互獨立,例如,若將增益設置為24dB,那么兩個通道的增益均為24dB。濾波器可以由外部時鐘驅動,也可以使用內部振蕩器。連接到RBias引腳的電阻為濾波器網絡和內部振蕩器設置偏置電流(除非由外部時鐘驅動)。改變時鐘頻率會改變濾波器帶寬,這使得濾波器能夠“調諧”到多種不同的帶寬。

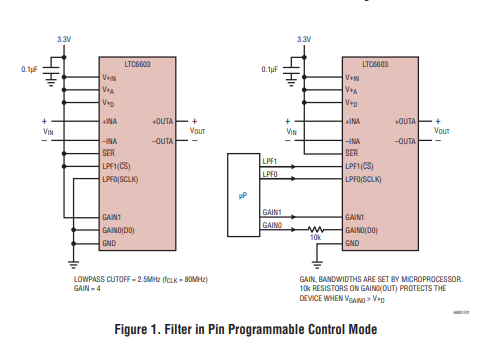

引腳可編程接口

如圖1所示,將SER連接到V+D可使濾波器通過引腳直接控制,通過引腳可編程控制線GAIN0、GAIN1、LPF1和LPF0進行控制。GAIN0(D0)引腳為雙向引腳(在引腳可編程控制模式下為輸入,在串行控制模式下為輸出)。在引腳可編程控制模式下,該引腳上的電壓不能超過V+D;否則,大電流可能會通過寄生二極管注入V+D(見圖2)。建議在GAIN0(D0)引腳處連接一個10kΩ電阻(見圖1)。SER具有內部電流限制功能,限制電流約為1mA。邏輯輸入均無內部上拉或下拉,需上拉至V+D 。

串行接口

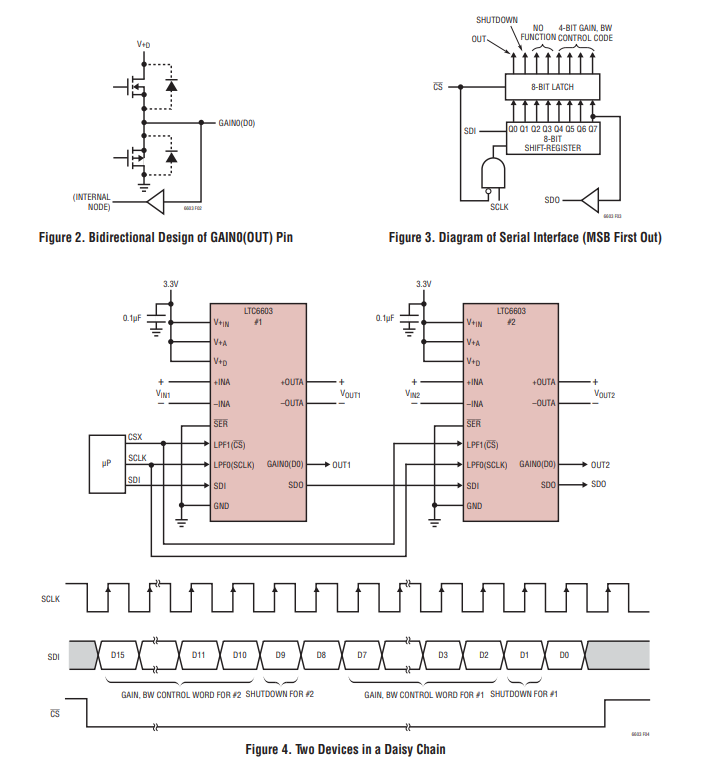

將SER連接到地可通過SPI串行接口控制濾波器。當CS為低電平時,串行數據在時鐘(SCLK)上升沿從SDI移入8位移位寄存器,最高有效位(MSB)最先移出(見圖3)。串行數據在時鐘下降沿從SDO移出。CS為高電平時,8位移位寄存器中的數據將加載到8位D鎖存器(即串行控制寄存器)中。注意:在拉高CS之前,SCLK必須為低電平,以避免出現額外的內部時鐘脈沖。SDO始終處于活動狀態(不會處于三態),不能與其他SPI輸出進行“線或”操作。此外,CS為高電平時,SDO不會強制為零。

多個LTC6603可以與其他LTC6603或其他具有串行接口的器件進行菊花鏈連接。菊花鏈連接通過將前級芯片的SDO連接到下一級芯片的SDI來實現,同時SCLK和CS保持連接到所有芯片,菊花鏈串行數據在時鐘作用下傳輸到所有芯片,然后拉高CS信號以同時更新所有芯片。圖4展示了兩個LTC6603菊花鏈連接的SPI配置示例。

-

濾波器

+關注

關注

162文章

8115瀏覽量

181476 -

接收器

+關注

關注

15文章

2565瀏覽量

73606 -

低通濾波器

+關注

關注

14文章

495瀏覽量

48129

發布評論請先 登錄

具有雙通道可編程帶通濾波器和差分驅動器LTC6602的演示板DC1304A-A

LTC6603 雙通道、可調低通濾波器

LTC6601/LTC6603/LTC6605 - 高性能寬帶有源濾波器和 ADC 驅動器系列提供前所未有的準確度以減輕設計負擔

UG-1045:評估ADRF6520雙通道、可編程低通濾波器和VGA,用于微波無線電的2 GHz通道間距

LTC6603雙通道、可調低通濾波器技術手冊

LTC6603雙通道、可調低通濾波器技術手冊

評論